Architecture

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Humidity & Temperature Sensor

Humidity & Temperature Sensor AM2322 Product Manuals product Features Super Mini Size Easy Protable Ultra-Low Power State Ultra-low voltage work Excellent long-term stability StandardI2C And single bus output 一、 Product Overview AM2322 The digital temperature and humidity sensor is a kind of temperature and humidity composite sensor with the output of calibrated digitalsignal.The special temperature and humidity collection technology is adopted to ensure the high reliability and long-term stability of the product.The sensor includes a capacitive sensing element and a high-precision integrated temperature measurement element, which is connected to a high- performance microprocessor.The product has high quality, super fast response, strong anti-interference ability and high cost performance. AM2322 communication mode adopts single bus, standard I squared C communication mode.Standard single bus interface makes system integration easy and fast.The super small volume, extremely low power consumption, the signal transmission distance can reach up to 20 meters, making it the best choice for all kinds of Two kinds of communication mode is used directly output after applications and even the most demanding applications.The I temperature compensation, humidity, temperature and the CRC squared C communication mode adopts standard communication check and other digital information, users need to secondary timing, and the user can be directly attached to the I squared C calculation of digital output, also need not to compensate the communication bus, with no additional wiring and simple use. temperature humidity, accurate temperature and humidity information can be got.The two modes of communication are free to switch, users are free to choose, easy to use, and should be widely used.The product is 4 lead wire and convenient connection. -

Tms320f28004x Microcontrollers Datasheet (Rev. F)

TMS320F280049, TMS320F280049C, TMS320F280048, TMS320F280048C, TMS320F280045, TMS320F280049, TMS320F280049C,TMS320F280041, TMS320F280041C, TMS320F280048, TMS320F280048C,TMS320F280040, TMS320F280040C TMS320F280045, www.ti.com TMS320F280041, TMS320F280041C,SPRS945F –TMS320F280040, JANUARY 2017 – REVISED TMS320F280040C FEBRUARY 2021 SPRS945F – JANUARY 2017 – REVISED FEBRUARY 2021 TMS320F28004x Microcontrollers 1 Features – Embedded Real-time Analysis and Diagnostic (ERAD) • TMS320C28x 32-bit CPU • Communications peripherals – 100 MHz – One Power-Management Bus (PMBus) – IEEE 754 single-precision Floating-Point Unit interface (FPU) – One Inter-integrated Circuit (I2C) interface – Trigonometric Math Unit (TMU) (pin-bootable) • 3×-cycle to 4×-cycle improvement for – Two Controller Area Network (CAN) bus ports common trigonometric functions versus (pin-bootable) software libraries – Two Serial Peripheral Interface (SPI) ports • 13-cycle Park transform (pin-bootable) – Viterbi/Complex Math Unit (VCU-I) – Two Serial Communication Interfaces (SCIs) – Ten hardware breakpoints (with ERAD) (pin-bootable) • Programmable Control Law Accelerator (CLA) – One Local Interconnect Network (LIN) – 100 MHz – One Fast Serial Interface (FSI) with a – IEEE 754 single-precision floating-point transmitter and receiver instructions • Analog system – Executes code independently of main CPU – Three 3.45-MSPS, 12-bit Analog-to-Digital • On-chip memory Converters (ADCs) – 256KB (128KW) of flash (ECC-protected) • Up to 21 external channels across two independent banks -

CP2725AC54TE Compact Power Line High Efficiency Rectifier 100-120/200-277VAC Input; Default Outputs: ±54VDC @ 2725W, 5VDC @ 4W

GE Data Sheet CP2725AC54TE Compact Power Line High Efficiency Rectifier 100-120/200-277VAC input; Default Outputs: ±54VDC @ 2725W, 5VDC @ 4W RoHS Compliant Features • Efficiency 96.2% • Compact 1RU form factor with 30 W/in3 density • Constant power from 52 – 58VDC • 2725W from nominal 200 – 277VAC • 1200W from nominal 100 – 120VAC • Output voltage programmable from 42V – 58VDC • PMBus compliant dual I2C and RS485 serial busses • Isolated +5V Aux, signals and I2C communications • Power factor correction (meets EN/IEC 61000-3-2 and EN 60555-2 requirements) Applications • Output overvoltage and overload protection • 48VDC distributed power architectures • AC Input overvoltage and undervoltage protection • Routers/Switches • Over-temperature warning and protection • VoIP/Soft Switches • Redundant, parallel operation with active load sharing • LAN/WAN/MAN applications • Remote ON/OFF • File servers • Internally controlled Variable-speed fan • Indoor wireless • Hot insertion/removal (hot plug) • Telecommunications equipment • Four front panel LED indicators • Enterprise Networks • UL* Recognized to UL60950-1, CAN/ CSA† C22.2 No. • SAN/NAS/iSCSI applications 60950-1, and VDE‡ 0805-1 Licensed to IEC60950-1 § • CE mark meets 2006/95/EC directive • RoHS Directive 2011/65/EU and amended Directive (EU) 2015/863 Description • Conformally coated option The CP2725AC54TE Rectifier provides significant efficiency improvements in the Compact Power Line platform of Rectifiers. High- density front-to-back airflow is designed for minimal space utilization and is highly expandable for future growth. The wide-input standard product is designed to be deployed internationally. It is configured with both RS485 and dual-redundant I2C communications busses that allow it to be used in a broad range of applications. -

Intel® Agilex™ Device Data Sheet

Intel® Agilex™ Device Data Sheet Subscribe DS-1060 | 2021.06.02 Send Feedback Latest document on the web: PDF | HTML Contents Contents Intel® Agilex™ Device Data Sheet............................................................................................................................................... 3 Electrical Characteristics...................................................................................................................................................... 5 Operating Conditions..................................................................................................................................................5 Switching Characteristics....................................................................................................................................................27 Core Performance Specifications.................................................................................................................................28 Periphery Performance Specifications.......................................................................................................................... 37 E-Tile Transceiver Performance Specifications...............................................................................................................46 P-Tile Transceiver Performance Specifications...............................................................................................................50 R-Tile Transceiver Performance Specifications...............................................................................................................55 -

Table of Contents

Table of Contents Chapter 1 Bus Decode -------------------------------------------------------------- 1 Basic operation --------------------------------------------------------------------------------------------- 1 Add a Bus Decode ----------------------------------------------------------------------------------------------------- 1 Advance channel setting ---------------------------------------------------------------------------------------------- 2 Specially Bus Decode: ------------------------------------------------------------------------------------------------ 4 1-Wire ------------------------------------------------------------------------------------------------------------------- 7 3-Wire ------------------------------------------------------------------------------------------------------------------- 9 7-Segment -------------------------------------------------------------------------------------------------------------- 11 A/D Converter--------------------------------------------------------------------------------------------------------- 14 AcceleroMeter -------------------------------------------------------------------------------------------------------- 17 AD-Mux Flash -------------------------------------------------------------------------------------------------------- 19 Advanced Platform Management Link (APML) ---------------------------------------------------------------- 21 BiSS-C------------------------------------------------------------------------------------------------------------------ 23 BSD --------------------------------------------------------------------------------------------------------------------- -

The PET750-12-050 Is a 759 Watts, 1U Form Factor Power Supply Module with Active PFC (Power Factor Correction)

The PET750-12-050 is a 759 Watts, 1U form factor power supply module with Active PFC (Power Factor Correction). It converts standard AC mains power into a main output of 12V for powering intermediate bus architectures (IBA) in high performance and reliability servers, routers, and network switches. The PET750-12-050 meets international safety standards and displays the CE-Mark for the European Low Voltage Directive (LVD). • Best-in-Class, 80 PLUS Certified “Platinum” Efficiency • Wide Input Voltage Range 90-264 VAC • AC Input with Power Factor Correction • Always-On 15 W Standby Output (5 V/3 A) • Hot-Plug Capability • Parallel Operation with Active Current Sharing • DC-DC Digital Controls for Improved Performance • High Density Design 20.5 W/in3 • Small Form Factor 300 x 50.5 x 40 mm (11.81 x 1.99 x 1.57 in) • Power Management Bus Communications Protocol for Control, Programming and Monitoring • Over Temperature, Output Over Voltage and Over Current Protection • One DC OK Signaling Status LED • Networking Switches • High Performance Servers • Routers 2 PET750-12-050xA PET 750 - 12 - 050 x A Product Family Power Level Dash V1 Output Dash Width Airflow Input N: Normal PET Front-Ends 750 W 12 V 50 mm A: AC R: Reverse OUTPUT MAX LOAD MAX LOAD MINIMUM RIPPLE & TOTAL MODEL CONNECTOR VOLTAGE CONVECTION 1 300 LFM 1,2 LOAD NOISE 3 REGULATION PET750-12-050NA 12 VDC 62 A 62 A 0 A 1% Card edger ± 2.5% PET750-12-050RA 12 VDC 62 A 62 A 0 A 1% Card edger ± 2.5% The PET750-12-050 AC-DC power supply is a mainly DSP controlled, highly efficient front-end. -

Design and Development of I C Protocol Using Verilog

DESIGN AND DEVELOPMENT OF I2C PROTOCOL USING VERILOG 1SIREESHA BHUVANAGIRI, 2SHAIK KHASIM BEEBI 1PG Scholar, Dept of ECE, JNTUK, AP, India. 2Krishanveni Engineering College for Women, HOD, Dept of ECE, JNTUK, AP, India. E-mail: [email protected], [email protected] Abstract - The I2C protocol was given by the Philips Semiconductors in order to allow faster devices to communicate with slower devices and also allow devices to communicate with each other over a serial data bus without data loss. I2C plays an important role as an interface in communication between devices. Electrically Erasable Programmable Read Only Memory (EEPROM), Analog to Digital Converter (ADC), Digital to Analog Converter (DAC) and Real Time Clock (RTC) requires an interface for communication and I2C is used as an interface between them. In this paper, the I²C (Inter-Integrated Circuit; generically referred to as "two-wire interface") is implemented using Verilog with Field Programmable Gate Arrays (FPGA). The I2C master bus controller was interfaced with Alter DE1 board, which act as a slave. This module was designed in Verilog HDL and simulated in Modelsim 10.1c. The design was synthesized using Quartus 11 10.1 tool. Today, testing and verification are alternatively used for the same thing. Testing of a large design using FPGA consumes longer compilation time in case of debugging and committing small mistakes. Keywords - Altera DE1 Board, System Verilog, I2C bus , SDA, SCL. I. INTRODUCTION more pins and signals to connect devices. The I²C (Inter-Integrated IC) bus developed by Philips The Inter Integrated Circuit (I2C) bus developed by company, is a simple bidirectional serial bus that Philips Company is a single bidirectional serial bus that supports multiple masters and slaves. -

An135f AN135-1 Application Note 135

Application Note 135 April 2012 Implementing Robust PMBus System Software for the LTC3880 Nick Vergunst INTRODUCTION commands because PMBus/SMBus provide timeouts to prevent bus hangups and optional packet error checking The LTC®3880 is a dual output PolyPhase® step-down DC/DC (PEC) to ensure data integrity. controller with integrated digital power system manage- ment. The LTC3880 can easily be controlled through a In general, a master device configured for I2C communi- PMBus interface, which builds upon I2C/IIC at speeds up cation is used for PMBus communication with little or no to 400kHz. System telemetry data can be obtained quickly change to hardware or firmware. Repeated starts (restarts) 2 and painlessly with simple polling functions. This exposes are not supported by all I C controllers but are required for 2 all important and critical information to the system devel- PMBus/SMBus reads. If a general purpose I C controller oper such as the voltage and current readings for the input is used, check that repeated starts are supported. and both outputs, temperature, fault conditions, general For a full description of the extensions and exceptions status information, and more. PMBus makes to SMBus, refer to PMBus Specification This application note discusses the design requirements Part 1 Revision 1.1: Paragraph 5: Transport. in regards to implementing robust firmware capable of For a full description of the differences between SMBus interacting with the LTC3880. and I2C, refer to System Management Bus (SMBus) Speci- fication Version 2.0: Appendix B—Differences Between 2 DOCUMENT OVERVIEW SMBus and I C. This document is broad in scope. -

HUAWEI X6800 Server

HUAWEI X6800 Server White Paper Issue 05 Date 2017-12-22 HUAWEI TECHNOLOGIES CO., LTD. Copyright © Huawei Technologies Co., Ltd. 2017. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written consent of Huawei Technologies Co., Ltd. Trademarks and Permissions and other Huawei trademarks are trademarks of Huawei Technologies Co., Ltd. All other trademarks and trade names mentioned in this document are the property of their respective holders. Notice The purchased products, services and features are stipulated by the contract made between Huawei and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied. The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied. Huawei Technologies Co., Ltd. Address: Huawei Industrial Base Bantian, Longgang Shenzhen 518129 People's Republic of China Website: http://e.huawei.com Issue 05 (2017-12-22) Huawei Proprietary and Confidential i Copyright © Huawei Technologies Co., Ltd. HUAWEI X6800 -

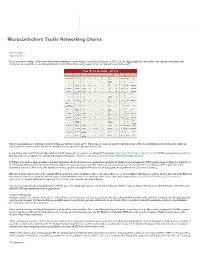

Microcontrollers Tackle Networking Chores

Microcontrollers Tackle Networking Chores 0 William Wong August 02, 2012 Developers have a range of wired and wireless mechanisms to connect microcontrollers to their peers (Table 1). On-chip peripherals often dictate the options, but many of the interfaces are accessible via off-chip peripherals. External line drivers and support chips are frequently required as well. There’s a maximum speed/distance tradeoff with some interfaces such as I2C. There also are many proprietary interfaces like 1-Wire from Maxim Integrated Products. Likewise, many high-performance DSPs and microcontrollers have proprietary high-speed interfaces. Some Analog Devices DSPs have high-speed serial links designed for connecting multiple DSP chips (see “Dual Core DSP Tackles Video Chores”). XMOS has proprietary serial links that allow processor chips to be combined in a mesh network (see “Multicore And Soft Peripherals Target Multimedia Applications”). PCI Express is used for implementing redundant interfaces often found in storage applications using the PCI Express non-transparent (NT) bridging support. High-speed interfaces like Serial RapidIO and InfiniBand are built into higher-end microprocessors, but they tend to be out of reach for most microcontrollers since they push the upper end of the bandwidth spectrum. Microcontroller speeds are moving up, but only high-end versions touch the gigahertz range where microprocessors are king. Ethernet is in the mix because of its compatibility from the low end at 10 Mbits/s. Also, some micros have 10- or 10/100-Mbit/s interfaces as options. In fact, this end of the Ethernet spectrum is the basis for many automation control networks where small micro nodes provide sensor and control support (see “Consider Fast Ethernet For Your Industrial Applications”). -

MSP Pmbus Library Users Guide

MSP PMBus Library Users Guide DOCNUM-1.00.00.00 Copyright ©2015 Texas Instruments Incorporated Contents 1 Copyright 1 2 Introduction 2 2.1 Associated Files............................................ 2 3 PMBus Protocol 3 3.1 PMBus Layer ............................................. 4 3.1.1 Alert Signal (SMBALERT) .................................. 4 3.1.2 Control Signal (CONTROL).................................. 4 3.1.3 Packet Error Checking (PEC)................................. 5 3.2 PMBus Procotol Formats....................................... 5 4 MSP PMBus Library 6 4.1 Library structure............................................ 6 4.2 Device Support ............................................ 7 4.3 Initialization .............................................. 7 4.3.1 PEC.............................................. 7 4.4 Initialization .............................................. 7 4.4.1 PEC.............................................. 8 4.4.1.1 Device specific PMBus command interface.................... 8 4.5 SMBALERT and Alert Response Address (ARA)........................... 8 4.6 CONTROL............................................... 8 5 Examples 9 5.1 Supported Devices .......................................... 9 5.2 Summary of the examples....................................... 9 5.3 Running the examples......................................... 9 5.3.1 Obtaining Code Composer Studio (CCS) or IAR Kickstart.................. 9 5.3.2 Hardware support....................................... 10 5.3.3 Obtaining and building the -

CP3000/3500AC54TE Global Platform High Efficiency Rectifier

GE Data sheet CP3000/3500AC54TE Global Platform High Efficiency Rectifier Input: 100-120/200-277 Vac; Default Output: ±54 Vdc @ 3000W/3500W; 5 Vdc @ 10W • RoHS Compliant Features • Efficiency meets 80plus Titanium requirements • Compact 1RU form factor with 40 W/in3 density • Constant power from 52 – 58VDC • 3000 or 3500W from nominal 200-277VAC • 1500W from nominal 100 – 120VAC • Output voltage programmable from 42V – 58VDC • ON/OFF control of the main output • Comprehensive input, output and overtemp. protection • PMBus compliant dual I2C serial bus and RS485 • Precision measurement reporting such as input power Applications consumption, input/output voltage & current • 48V distributed power architectures DC • Remote firmware upgrade capable • Routers/ VoIP/Soft and other Telecom Switches • Power factor correction (meets EN/IEC 61000-3-2 and • LAN/WAN/MAN applications EN 60555-2 requirements) • File servers, Enterprise Networks, Indoor wireless • Redundant, parallel operation with active load sharing • SAN/NAS/iSCSI applications • Redundant +5V @ 2A Aux power • Internally controlled Variable-speed fan • Hot insertion/removal (hot plug) • Four front panel LED indicators • UL and cUL approved to UL/CSA †62368-1, TUV (EN62368- 1), CE Mark§ (for LVD) and CB Report available • RoHS Directive 2011/65/EU and amended Directive (EU) 2015/863 • Compliant to REACH Directive (EC) No 1907/2006 Description The CP3000/3500AC54TEP Rectifiers provide significantly higher power density in the same form factor and efficiency improvements in the Compact Power Line of Rectifiers. The only difference between these rectifiers is output power limit. High-density front-to-back airflow is designed for minimal space utilization and is highly expandable for future growth.