Free Electronic Circuits Design Software

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Using the ELECTRIC VLSI Design System Version 9.07

Using the ELECTRIC VLSI Design System Version 9.07 Steven M. Rubin Author's affiliation: Static Free Software ISBN 0−9727514−3−2 Published by R.L. Ranch Press, 2016. Copyright (c) 2016 Static Free Software Permission is granted to make and distribute verbatim copies of this book provided the copyright notice and this permission notice are preserved on all copies. Permission is granted to copy and distribute modified versions of this book under the conditions for verbatim copying, provided also that they are labeled prominently as modified versions, that the authors' names and title from this version are unchanged (though subtitles and additional authors' names may be added), and that the entire resulting derived work is distributed under the terms of a permission notice identical to this one. Permission is granted to copy and distribute translations of this book into another language, under the above conditions for modified versions. Electric is distributed by Static Free Software (staticfreesoft.com), a division of RuLabinsky Enterprises, Incorporated. Table of Contents Chapter 1: Introduction.....................................................................................................................................1 1−1: Welcome.........................................................................................................................................1 1−2: About Electric.................................................................................................................................2 1−3: Running -

A Fedora Electronic Lab Presentation

Chitlesh GOORAH Design & Verification Club Bristol 2010 FUDConBrussels 2007 - [email protected] [ Free Electronic Lab ] (formerly Fedora Electronic Lab) An opensource Design and Simulation platform for Micro-Electronics A one-stop linux distribution for hardware design Marketing means for opensource EDA developers (Networking) From SPEC, Model, Frontend Design, Backend, Development boards to embedded software. FUDConBrussels 2007 - [email protected] Electronic Designers Problems Approx. 6 month design development cycle Tackling Design Complexity Lower Power, Lower Cost and Smaller Space Semiconductor Industry's neck squeezed in 2008 Management (digital/analog) IP Portfolio FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] A basic Design Flow FUDConBrussels 2007 - [email protected] TIP: Use verilator to lint your verilog files. Most of the Veripool tools are available under FEL. They are in sync with Wilson Snyder's releases. FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] GTKWaveGTKWave Don'tDon't forgetforget itsits TCLTCL backendbackend WidelyWidely usedused togethertogether withwith SystemCSystemC FUDConBrussels 2007 - [email protected] Tools Standard Cell libraries FUDConBrussels 2007 - [email protected] BackendBackend designdesign Open Circuit Design, Electric FUDConBrussels 2007 - [email protected], Toped gEDA/gafgEDA/gaf Well known and famous. A very good example of opensource -

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD

Experiences in Using Open Source Software for Teaching Electronic Engineering CAD Dr Simon Busbridge1 & Dr Deshinder Singh Gill School of Computing, Engineering and Mathematics, University of Brighton, Brighton BN2 4GJ [email protected] Abstract Embedded systems and simulation distinguish modern professional electronic engineering from that learnt at school. First year undergraduates typically have little appreciation of engineering software capabilities and file handling beyond elementary word processing. This year we expedited blended teaching through the experiential based learning process via open source engineering software. Students engaged with the entire electronic engineering product creation process from inception, performance simulation, printed circuit board design, manufacture and assembly, to cabinet design and complete finished product. Currently students learn software skills using a mixture of electronic and mechanical engineering software packages. Although these have professional capability they are not available off-campus and are sometimes surprisingly poor in simulating real world devices. In this paper we report use of LTspice, FreePCB and OpenSCAD for the learning and teaching of analogue electronics simulation and manufacture. Comparison of the software options, the type of tasks undertaken, examples of student assignments and outputs, and learning achieved are presented. Examples of assignment based learning, integration between the open source packages and difficulties encountered are discussed. Evaluation of student attitudes and responses to this method of learning and teaching are also discussed, and the educational advantages of using this approach compared to the use of commercial packages is highlighted. Introduction Most educational establishments use software for simulating or designing engineering. Most commercial packages come with an academic licence which restricts access to on-site computers. -

Bridging the Gap Between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation

Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik Bridging the Gap between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation A method for automatically identifying and characterising combinational macros in synchronous sequential systems at register-transfer level and subsequent executable high-level model generation with respect to non-functional properties Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften von Dipl.-Inform. Kai Hylla Gutachter: Prof. Dr. Wolfgang Nebel Prof. Dr. Wolfgang Rosenstiel Tag der Disputation: 13. Januar 2014 Abstract Knowing a system’s power dissipation and timing behaviour is mandatory for today’s system development and key to an effective design space exploration. Not only does battery lifetime or design of the power supply directly depend on the power dissipation of the system. Second-order effects such as thermal behaviour or degradation effects that are directly or indirectly affected by the power dissipation must be considered, too. Various techniques for power estimation exist at different levels of abstraction. Low-level approaches provide accurate estimation results but require a lot of computational effort. High- level approaches however, allow fast and early estimates, but lack of a deeper knowledge and understanding of the hardware, implementing the behaviour. Therefore, they can only give rough estimates. What is missing is an approach allowing fast and early estimates with respect to as many relevant hardware artefacts and physical properties as possible. This doctoral thesis tackles the problem of a fast, yet accurate power and timing estimation of embedded hardware modules at a high-level of abstraction. A comparatively time consuming low-level estimation is performed once in order to obtain an accurate estimate. -

Elektronikentwicklung Unter Linux

Elektronikentwicklung unter Linux Clifford Wolf Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 1 Einführung ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation Leiterplattenentwurf und Schematic Einführung Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 2 Behandelte Themen Einführung ■ Schaltungssimulation ● Behandelte Themen ● Unvollständigkeit Schaltungssimulation ■ Leiterplattenentwurf und Schematic Leiterplattenentwurf und Schematic Compiler und Libraries ■ Compiler fuer embedded CPUs und ausgewaehlte Libraries Mathematik Mechanik ■ Mathematik ■ Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 3 Unvollständigkeit Einführung ■ Ich kann nur etwas über die Tools erzaehlen die ich selbst ● Behandelte Themen ● Unvollständigkeit verwende. Schaltungssimulation Leiterplattenentwurf und ■ Schematic Für Hinweise und Ergänzungen bin ich jederzeit offen und Compiler und Libraries dankbar. Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 4 Einführung Schaltungssimulation ● QUCS ● GnuCap ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave Schaltungssimulation Leiterplattenentwurf und Schematic Compiler und Libraries Mathematik Mechanik Clifford Wolf, 26. September 2010 http://www.clifford.at/ - p. 5 QUCS Einführung http://qucs.sourceforge.net/ Schaltungssimulation ● QUCS ● GnuCap ■ Sehr sauber implementierter Simulator ● LTspice ● Java Circuit Simulator ● Icarus Verilog ● GTKWave ■ Gute GUI für Schematic-Entry -

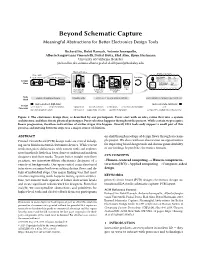

Beyond Schematic Capture Meaningful Abstractions for Better Electronics Design Tools

Beyond Schematic Capture Meaningful Abstractions for Better Electronics Design Tools Richard Lin, Rohit Ramesh, Antonio Iannopollo, Alberto Sangiovanni Vincentelli, Prabal Dutta, Elad Alon, Björn Hartmann University of California, Berkeley {richard.lin,rkr,antonio,alberto,prabal,elad,bjoern}@berkeley.edu Physical Device Parts Selection Ideas and ATmega Part Number Size Vf +3.3v Iteration Requirements System Architecture OVLFY3C7 5mm 2 V D0 APG1005SYC-T 0402 2.05 V Button J1 Design Micro- D1 5988140107F 0805 2 V D1 controller - or - ... SW1 Part Number Core LED Flow R1 U1 R2 ATmega32u4 AVR GND Micro- controller LPC1549 ARM CM3 Final FE310-G000 RV32IMAC Hand-built Schematic Prototype PCB Prototypes Capture PCB Tools paper, drawing software breadboards EDA suites: Altium, EAGLE, KiCAD parts libraries, catalogs, spreadsheets Used more abstract, high-level more concrete, low-level Design user stories implementation exploration documentation verification cost, manufacturability cost Concerns functional specification verification supporting circuitry system integration component availability and sourcing Figure 1: The electronics design flow, as described by our participants. Users start with an idea, refine that intoasystem architecture, and then iterate physical prototypes. Parts selection happens throughout the process. While certain steps require linear progression, iteration and revision of earlier stages also happen. Overall, EDA tools only support a small part of this process, and moving between steps was a major source of friction. ABSTRACT on clickthrough mockups of design flows through an exam- Printed Circuit Board (PCB) design tools are critical in help- ple project. We close with our observation on opportunities ing users build non-trivial electronics devices. While recent for improving board design tools and discuss generalizability work recognizes deficiencies with current tools and explores of our findings beyond the electronics domain. -

Ecebuntu - an Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses

RESEARCH ARTICLE Electrica 2018; 18(2): 210-217 ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses Bilal Wajid1 , Ali Rıza Ekti2 , Mustafa Kamal AlShawaqfeh3 1Department of Electrical Engineering, University of Engineering and Technology, Lahore, Pakistan 2Department of Electrical-Electronics Engineering, Balıkesir University School of Engineering, Balıkesir, Turkey 3School of Electrical Engineering and Information Technology, German Jordanian University, Amman, Jordan Cite this article as: B. Wajid, A. R. Ekti, M. K. AlShawaqfeh, “ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses”, Electrica, vol. 18, no: 2, pp. 210-217, 2018. ABSTRACT ECEbuntu is a free, easily distributable, customized operating system based on Ubuntu 12.04 long term support (LTS) designed for electrical/electronic and computer engineering (ECE) students. ECEbuntu is aimed at universities and students as it represents a cohesive environment integrating more than 30 pre-installed software and packages all catering to undergraduate coursework offered in ECE and Computer Science (CS) programs. ECEbuntu supports a wide range of tools for programming, circuit analysis, printed circuit board design, mathematical and numerical analysis, network analysis, and RF and microwave transmitter design. ECEbuntu is free and effective alternative to the existing costly and copyrighted software packages. ECEbuntu attempts -

Digital Sensors Operate on 3.3V

Worcester Polytechnic Institute A Major Qualifying Project AURORA Autonomous Unpowered Recovery of Radiosonde Aircraft Submitted By: Richard Eberheim, Robotics Engineering Nicholas Hassan, Robotics Engineering and Electrical & Computer Engineering Joshua O’Connor, Mechanical Engineering Advised By: Kenneth Stafford, Professor Robotics Engineering, Mechanical Engineering Fred Looft, Professor Electrical Engineering This report represents the work of WPI undergraduate students submitted to the faculty as evidence of completion of a degree requirement. WPI routinely publishes these reports on its website without editorial or peer review. For more information about the projects program at WPI, please see http://www.wpi.edu/academics/ugradstudies/project-learning.html Abstract This project developed an autonomous radiosonde glider that actively steers itself from the apex of its flight to safe recovery locations on the ground. This enables easy and reliable recovery, reducing costs and offering new capabilities to atmospheric researchers. The glider integrates the essential weather sensors used on current radiosondes with those needed for autonomous flight in a durable, easy to manufacture airframe capable of multiple data gathering flights with minimal repairs between each flight. 1 Acknowledgments This project was made possible through the support, guidance, and assistance of the staff and students of Worcester Polytechnic Institute. We would like to thank Professors Ken Stafford and Fred Looft for advising the project. We would also like -

Performed the Most Often. in FPGA Design Flow, Functional and Gate

performed the most often. In FPGA design flow, functional and gate-level timing simulation is typically performed when designers suspect that there might be a mismatch between RTL and functional or gate-level timing simulation results, which can lead to an incorrect design. The mismatch can be caused for several reasons discussed in more detail in Tip #59. Note that the nomenclature of simulation types is not consistent. The same name, for instance “gate-level simulation”, can have slightly different meaning in simulation flows of different FPGA vendors. The situation is even more confusing in ASIC simulation flows, which have many more different simulation types, such as transistor-level, and dynamic simulation. The following figure shows simulation types designers can perform during Xilinx FPGA synthesis and physical implementation process. Figure 1: Simulation types Xilinx FPGA designers can perform simulation after each level of design transformation from the original RTL to the bitstream. The following example is a 12-bit OR gate implemented in Verilog. module sim_types(input [11:0] user_in, output user_out); assign user_out = |user_in; endmodule XST post-synthesis simulation model is implemented using LUT6 and LUT2 primitives, which are parts of Xilinx UNISIMS RTL simulation library. wire out, out1_14; LUT6 #( .INIT ( 64'hFFFFFFFFFFFFFFFE )) out1 ( .I0(user_in[3]), .I1(user_in[2]), .I2(user_in[5]), .I3(user_in[4]), .I4(user_in[7]), .I5(user_in[6]), .O(out)); LUT6 #( .INIT ( 64'hFFFFFFFFFFFFFFFE )) out2 ( .I0(user_in[9]), .I1(user_in[8]), .I2(user_in[11]), .I3(user_in[10]), .I4(user_in[1]), .I5(user_in[0]), .O(out1_14)); LUT2 #( .INIT ( 4'hE )) out3 ( .I0(out), .I1(out1_14), .O(user_out) ); Post-synthesis simulation model can be generated using the following command: $ netgen -w -ofmt verilog -sim sim.ngc post_synthesis.v Post-translate simulation model is implemented using X_LUT6 and X_LUT2 primitives, which are parts of Xilinx SIMPRIMS simulation library. -

Metadefender Core V4.17.3

MetaDefender Core v4.17.3 © 2020 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of MetaDefender Core 14 1. Quick Start with MetaDefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Process Files with MetaDefender Core 21 2. Installing or Upgrading MetaDefender Core 22 2.1. Recommended System Configuration 22 Microsoft Windows Deployments 22 Unix Based Deployments 24 Data Retention 26 Custom Engines 27 Browser Requirements for the Metadefender Core Management Console 27 2.2. Installing MetaDefender 27 Installation 27 Installation notes 27 2.2.1. Installing Metadefender Core using command line 28 2.2.2. Installing Metadefender Core using the Install Wizard 31 2.3. Upgrading MetaDefender Core 31 Upgrading from MetaDefender Core 3.x 31 Upgrading from MetaDefender Core 4.x 31 2.4. MetaDefender Core Licensing 32 2.4.1. Activating Metadefender Licenses 32 2.4.2. Checking Your Metadefender Core License 37 2.5. Performance and Load Estimation 38 What to know before reading the results: Some factors that affect performance 38 How test results are calculated 39 Test Reports 39 Performance Report - Multi-Scanning On Linux 39 Performance Report - Multi-Scanning On Windows 43 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. -

Designspark PCB PRO V10.0 Supplement 2 Designspark V10.0 Supplement

DesignSpark PCB PRO V10.0 Supplement 2 DesignSpark V10.0 Supplement Copyright Notice Copyright in the whole and every part of this software and manual belongs to RS Components and may not be used, sold, transferred, copied or reproduced in whole or in part in any manner or in any media to any person, without the prior written consent of RS Components. If you use this manual you do so at your own risk and on the understanding that neither RS Components nor associated companies shall be liable for any loss or damage of any kind. RS Components does not warrant that the software package will function properly in every hardware software environment. Although RS Components has tested the software and reviewed the documentation, RS Components makes no warranty or representation, either express or implied, with respect to this software or documentation, their quality, performance, merchantability, or fitness for a particular purpose. This software and documentation are licensed 'as is', and you the licensee, by making use thereof, are assuming the entire risk as to their quality and performance. In no event will RS Components be liable for direct, indirect, special, incidental, or consequential damage arising out of the use or inability to use the software or documentation, even if advised of the possibility of such damages. RS Components reserves the right to alter, modify, correct and upgrade our software programs and publications without notice and without incurring liability. DesignSpark is a Trademark of RS Components, Microsoft, Windows, Windows NT and Intellimouse are either registered trademarks or trademarks of Microsoft Corporation. -

Circuit Cellar No.269

PROJECT: Proximity Card Access Control INSIGHT: Determine a Design’s Failure Rate INNOVATE: Power-Up with Heat LOCATION: United States LOCATION: Canada LOCATION: United States PAGE: 34 PAGE: 64 PAGE: 68 N O 269 CIRCUIT CELLAR THE WoRLD’S SoURCE foR EMBEDDED ELECTRonICS EnGInEERInG InfoRMaTIon DECEMBER 2012 The World’s Source for Embedded Electronics Engineering Information ISSUE 269 PROGRAMMABLE LOGIC MCU-Based Bike Computer Inside Arduino’s Power Supply Linux & Concurrency DECEMBER 2012 PROGRAMMABLE LOGIC Synchronous Detection Explained Electrically Actuated Sound Effects PLUS Green Energy Design Innovative RL78-Based Projects // Electrostatic Cleaning Robot // Solar-Powered Water Heater // Portable Power Quality Meter www.circuitcellar.com NowNNow withwiwitithth 32MB3322MMB FlashFllasashh andand 64MB64M4MBMBB RAM!RAM! MOD54415 Core Module NANO54415 Core Module 32-bit 250 MHz processor 32-bit 250 MHz processor 64MB DDR2 RAM 64MB DDR2 RAM 32MB ash 8MB ash $ 00 10/100 Mbps Ethernet 10/100 Mbps Ethernet 69 Qty.. 100100ytQ 44 general purpose I/O 30 general purpose I/O Eight UARTs Eight UARTs NANO54415 Five I2C Four I2C Two CAN Two CAN 3 SPI 3 SPI 1-Wire® 1-Wire® 5 pulse width modulators (PWM) 8 pulse width modulators (PWM) SSI SSI MicroSD ash card MicroSD ash card ready $ 00 8 analog to digital converters (ADC) 6 analog to digital converters (ADC) Qty.tQ yy.. 100 Two digital to analog converters (DAC) Two digital to analog converters (DAC) MOD54415 89 Quickly create and deploy applications from your Mac or Windows PC Low cost NetBurner development kits are available to customize Development Kit for MOD54415 any aspect of operation including web pages, data ltering, or custom Part No.