Sensorless PMSM Field-Oriented Control on Kinetis KV and KE

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AND8002/D Eclinps™, Eclinps Lite™, Eclinps Plus™, Eclinps MAX™, and Gigacomm™ Marking and Ordering Information Guide

查询AND8003-D供应商 捷多邦,专业PCB打样工厂,24小时加急出货 AND8002/D ECLinPS,ECLinPSLite, ECLinPSPlus, ECLinPSMAX,and GigaCommMarkingand OrderingInformationGuide http://onsemi.com APPLICATION NOTE Prepared by: Paul Shockman ON Semiconductor HFPD Applications Engineer Introduction This application note describes the device markings and This application note also includes the following ordering information for the following ON Semiconductor appendices: families (refer to the respective family data book for family • Appendix 1: ECLinPS Device Order Number and information): Marking tables. • ECLinPS • Appendix 2: ECLinPS Lite Device Order Number and • ECLinPS Lite Marking tables. • ECLinPS Plus • Appendix 3: ECLinPS Plus Device Order Number and • ECLinPS MAX Marking tables. • GigaComm • Appendix 4: ECLinPS MAX Device Order Number Note that data sheet information takes precedence over and Marking Tables. this application note if there are any differences. • Appendix 5: GigaComm Device Order Number and Marking tables. Application Note Information This application note is divided into the following sections: • Section 1: Data Sheet Marking Diagrams − The diagrams provide identification, traceability, date, and packaging information. • Section 2: Data Sheet Ordering Information Tables − The tables list the device order numbers for every available device configuration. Semiconductor Components Industries, LLC, 2005 1 Publication Order Number: April, 2005 − Rev. 6 AND8002/D AND8002/D SECTION 1: Data Sheet Marking Diagrams Device Marking Examples • Code 1. Circuit Identification Code The marking format is dependent upon the device • Code 2. Temperature Compensation Code package, and larger device packages allow the inclusion of • Code 3. Family Identification Code more information on the face of the device. On the larger • packages where marking space permits, the Pb Free Code 4. -

Problems and Innovations

ТЕХНИЧЕСКИЕ НАУКИ........................................................................................................... 7 О СОВЕРШЕНСТВОВАНИИ ТЕХНОЛОГИИ ЗАГОТОВКИ ДРЕВЕСИНЫ ОСИНЫ КАК МАТЕРИАЛА ДЛЯ УСТРОЙСТВА КРОВЛИ С УЧЕТОМ ПРИРОДНЫХ И ПРОИЗВОДСТВЕННЫХ УСЛОВИЙ БОРИСОВ А.Ю., КОЛЕСНИКОВ Г.Н. ...................................................................................... 8 АНАЛИЗ УЯЗВИМОСТЕЙ ИСХОДНОГО КОДА НА ЭТАПАХ РАЗРАБОТКИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ НЕСТЕРЕНКО М.А. МИКОВА С.А., БЕЛОЗЁРОВА А.А. ...................................................... 14 СХЕМА МОБИЛЬНОЙ СИСТЕМЫ КРУГОВОГО ОБЗОРА ДЛЯ ВИДЕОСКАНИРОВАНИЯ ПРОСТРАНСТВА СМИРНОВ М.Л. ...................................................................................................................... 20 СЕЛЬСКОХОЗЯЙСТВЕННЫЕ НАУКИ ................................................................................ 24 УРОЖАЙНОСТЬ ОДНОЛЕТНИХ ТРАВ ПО СИСТЕМАМ ОСНОВНОЙ ОБРАБОТКИ ПОЧВЫ В СЕВЕРНОМ ЗАУРАЛЬЕ РЗАЕВА В.В. .......................................................................................................................... 25 ЭКОНОМИЧЕСКИЕ НАУКИ .................................................................................................. 30 НЕЙРО-СЕТЕВАЯ ТРАНСФОРМАЦИЯ СТРУКТУРЫ ИНФОРМАЦИОННОЙ ЭКОНОМИКИ ДЯТЛОВ С.А. .......................................................................................................................... 31 МЕЖДИСЦИПЛИНАРНЫЙ ПОДХОД К ИССЛЕДОВАНИЮ НЕЙРО-СЕТЕВОЙ РЕИНДУСТРИАЛИЗАЦИИ ЭКОНОМИКИ ДЯТЛОВ С.А., НОВОСЕЛОВА Е.М. ..................................................................................... -

119 Original Article the GOLDEN SHRINES of TUTANKHAMUN

id9070281 pdfMachine by Broadgun Software - a great PDF writer! - a great PDF creator! - http://www.pdfmachine.com http://www.broadgun.com Egyptian Journal of Archaeological and Restoration Studies "EJARS" An International peer-reviewed journal published bi-annually Volume 2, Issue 2, December - 2012: pp: 119-130 www. ejars.sohag-univ.edu.eg Original article THE GOLDEN SHRINES OF TUTANKHAMUN AND THEIR INTENDED BURIAL PLACE Soliman, R. Lecturer, Tourism guidance dept., Faculty of Archaeology & Tourism guidance, Misr Univ. for Sciences & Technology, 6th October city, Egypt E-mail: [email protected] Received 3/5/2012 Accepted 12/10/2012 Abstract The most famous tomb at the Valley of the Kings, KV 62 housed so far the most intact discovery of royal funerary treasures belonging to the eighteenth dynasty boy-king Tutankhamun. The tomb has a simple architectural plan clearly prepared for a non- royal burial. However, the hastily death of Tutankhamun at a young age caused his interment in such unusually small tomb. The treasures discovered were immense in number, art finesse and especially in the amount of gold used. Of these treasures the largest shrine of four shrines laid in the burial chamber needed to be dismantled and reassembled in the tomb because of its immense size. Clearly the black marks on this shrine helped in the assembly and especially the orientation in relation to the burial chamber. These marks are totally incorrect and prove that Tutankhamun was definitely intended to be buried in another tomb. Keywords: KV62, WV23, Golden shrines, Tutankhamun, Burial chamber, Orientation. 1. Introduction Tutankhamun was only nine and the real cause of his death remains years old when he got to throne; at that enigmatic. -

DSFRA IKEN Report Template

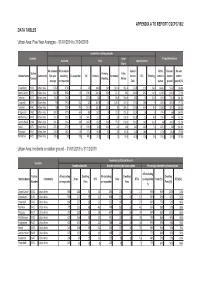

APPENDIX A TO REPORT CSCPC/19/2 DATA TABLES Urban Area: Five-Year Averages – 01/04/2014 to 31/04/2019 Incidents on station grounds Location False Pump Attendances Overview Fires Special Service Alarm All incidents All incidents Special All by On own On own Station Primary: False Station Name Community five-year excluding Co-responder All Primary Secondary Service RTC Flooding station's station station Number Dwelling Alarms average co-responder Calls pumps ground ground (%) Greenbank KV50 Urban Area 878.6 878.6 0 245 104.6 56.6 140.4 361.4 271.8 21.6 24.6 1424.8 974.2 68.4% Danes Castle KV32 Urban Area 832.6 830.8 1.8 198.8 126.4 56.6 72.4 385 248.4 29.2 14.8 1090.6 849.4 77.9% Torquay KV17 Urban Area 744.8 744.8 0 207.8 111 59 96.8 306.8 230 36 15.8 919.8 776.4 84.4% Crownhill KV49 Urban Area 742 741.8 0.2 227 100.6 43 126.4 337.4 177.4 28.6 9 878.4 680.6 77.5% Taunton KV61 Urban Area 734 733.4 0.6 227.8 132.8 56.6 95 284.6 221.6 65.4 8.4 1038.8 901.8 86.8% Bridgwater KV62 Urban Area 584.2 577.6 6.6 160 88.2 38 71.8 231.8 192.4 56 8 774.4 666 86.0% Middlemoor KV59 Urban Area 537.6 535.8 1.8 144.2 91.2 33 53 239.6 153.8 51 8.8 724.4 444 61.3% Camels Head KV48 Urban Area 491.6 491.2 0.4 162.8 85.2 50.4 77.6 178.6 150.2 16.6 11.8 638 390.2 61.2% Yeovil KV73 Urban Area 471.6 471.6 0 139.6 78.6 34.8 61 191 141 46.8 7.4 674.2 569 84.4% Plympton KV47 Urban Area 218.4 204.4 14 57.8 34.8 12 23 87.8 72.4 18.6 3 170.6 135.8 79.6% Plymstock KV51 Urban Area 185.8 185 0.8 48.4 27.4 12 21 76.8 60.6 12.6 2.6 165.4 123.8 74.8% Urban Area: Incidents on -

Risk Assessment of Flash Floods in the Valley of the Kings, Egypt

京都大学防災研究所年報 第 60 号 B 平成 29 年 DPRI Annuals, No. 60 B, 2017 Risk Assessment of Flash Floods in the Valley of the Kings, Egypt Yusuke OGISO(1), Tetsuya SUMI, Sameh KANTOUSH, Mohammed SABER and Mohammed ABDEL-FATTAH(1) (1) Graduate School of Engineering, Kyoto University Synopsis Flash floods unavoidably affect various archaeological sites in Egypt, through increased frequency and severity of extreme events. The Valley of the Kings (KV) is a UNESCO World Heritage site with more than thirty opened tombs. Recently, most of these tombs have been damaged and inundated after 1994 flood. Therefore, KV mitigation strategy has been proposed and implemented with low protection wall surrounding tombs. The present study focuses on the evaluation and risk assessment of the current mitigation measures especially under extreme flood events. Two dimensional hydrodynamic model combined with rainfall runoff modeling by using TELEMAC-2D to simulate the present situation without protection wall and determine the risk of 1994 flood. The results revealed that the current mitigation measures are not efficient. Based on the simulation scenarios, risk of flash floods is assessed, and the more efficient mitigation measurements are proposed. Keywords: Flash floods, The Valley of the Kings, TELEMAC-2D, Mitigation measures 1. Introduction Recently, most of these tombs have been damaged and inundated after 1994 flood. In response to this Egypt is one of arid and semiarid Arabian flood event, the American Research Center in Egypt countries that faces flash floods in the coastal and (ARCE) hired an interdisciplinary team of Nile wadi systems. Wadi is a dry riverbed that can consultants to prepare a flood-protection plan. -

October 14 Newsletter

ESSEX EGYPTOLOGY GROUP Newsletter 92 October 2014/November 2014 DATES FOR YOUR DIARY 5th October Beyond Indiana Jones: The Ark of the Covenant and Egyptian ritual processional furniture: David Falk 2nd November New Discoveries at Hierakonpolis: Dr Renee Friedman 7th December Times of Transition: the High Priests of Amun at the end of the New Kingdom: Jennifer Palmer 4th January Lunch at Crofter’s Wine Bar for Members and Friends 1st February Gebel el-Silsila: Sarah Doherty This month we welcome David Falk who is travelling to us from Liverpool where he is currently studying and next month we welcome Dr.Renée Friedman who is a graduate of the University of California, Berkeley, in Egyptian Archaeology and has worked at many sites throughout Egypt since 1980. With special interest in the Predynastic, Egypt’s formative period, in 1983 she joined the team working at Hierakonpolis, and went on to become the director of the Hierakonpolis Expedition in 1996, a title she still holds. Currently the Heagy Research Curator of Early Egypt at the British Museum, she is the author of many scholarly and popular articles about all aspects of the fascinating site of Hierakonpolis. NEW YEAR LUNCH Our New Year Lunch next year is on Sunday 4th January at Crofters in Witham, the restaurant where we have enjoyed a similar occasion for the past couple of years. The cost for three courses is £18.50, so with wine and tips it will probably be about £25. It is being organised by Alison Woollard and you will need to give her a £5 deposit, per person. -

ABSTRACT Carl Nicholas Reeves STUDIES in the ARCHAEOLOGY

ABSTRACT Carl Nicholas Reeves STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies This study considers the physical evidence for tomb robbery on the Theban west bank, and its resultant effects, during the New Kingdom and Third Intermediate Period. Each tomb and deposit known from the Valley of the Kings is examined in detail, with the aims of establishing the archaeological context of each find and, wherever possible, isolating and comparing the evidence for post-interment activity. The archaeological and documentary evidence pertaining to the royal caches from Deir el-Bahri, the tomb of Amenophis II and elsewhere is drawn together, and from an analysis of this material it is possible to suggest the routes by which the mummies arrived at their final destinations. Large-scale tomb robbery is shown to have been a relatively uncommon phenomenon, confined to periods of political and economic instability. The caching of the royal mummies may be seen as a direct consequence of the tomb robberies of the late New Kingdom and the subsequent abandonment of the necropolis by Ramesses XI. Associated with the evacuation of the Valley tombs may be discerned an official dismantling of the burials and a re-absorption into the economy of the precious commodities there interred. STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies (Volumes I—II) Volume I: Text by Carl Nicholas Reeves Thesis submitted for the degree of Doctor of Philosophy School of Oriental Studies University of Durham 1984 The copyright of this thesis rests with the author. -

Coptic Items the Screaming Mummy How to Design an Egyptian Door

Coptic Items The Screaming How to Design Mummy An Egyptian Door Some highlights of TEC’s Coptic Egypt collection. Murder and vengeance in the Do you know your Torus from 20th Dynasty. your Cavetto? Rex Wale Editor in Chief Dulcie Engel Associate Editor A former French and linguistics lecturer, I have volunteered at the Egypt Centre since April 2014. I am a gallery supervisor in both galleries, and author of the Egyptian Writing Trails. Apart from language, I am particularly interested in the history of collecting. I won the 2016 Volunteer of the Year award. Hello all, The World may be changing, but here’s one thing you can rely on; the Egypt Centre Newsletter will keep on keeping on! Rob Stradling Technical Editor We hope you enjoy the issue, A volunteer since 2012, you can find packed as it is with the usual (and me supervising the House of Life on Tuesdays & Thursdays; at the the not-so-usual) to keep you computer desk, paternally tending informed and entertained. this luminous organ; or roaming the corridors, pursuing my one-man We intend to keep going however quest for a biscuit-free workplace. long the hiatus lasts, so please don’t stop submitting material. If reading a new newsletter helps you to keep your spirits up, just imagine how If you would like to contribute to the newsletter or good writing for one would feel! submit articles for consideration please contact: [email protected] The Newsletter is ordinarily published every three Take care, months, however publication will be on an ad hoc basis for the time being. -

Durham E-Theses

Durham E-Theses Studies in the archaeology of the Valley of the Kings : with particular reference to tomb robbery and the caching of the royal mummies. Reeves, Carl Nicholas How to cite: Reeves, Carl Nicholas (1984) Studies in the archaeology of the Valley of the Kings : with particular reference to tomb robbery and the caching of the royal mummies., Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/958/ Use policy The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-prot purposes provided that: • a full bibliographic reference is made to the original source • a link is made to the metadata record in Durham E-Theses • the full-text is not changed in any way The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full Durham E-Theses policy for further details. Academic Support Oce, Durham University, University Oce, Old Elvet, Durham DH1 3HP e-mail: [email protected] Tel: +44 0191 334 6107 http://etheses.dur.ac.uk 2 STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies (Volumes I-II) Volume II: Notes to Text by Carl Nicholas Reeves Thesis submitted for the degree of Doctor of Philosophy School of Oriental Studies University of Durham 1984 The copyright of this thesis rests with the author. -

Religija I Pogrebni Običaji Tijekom 18. Dinastije

Religija i pogrebni običaji tijekom 18. dinastije Škrlec, Andreja Master's thesis / Diplomski rad 2018 Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Department of Croatian Studies / Sveučilište u Zagrebu, Hrvatski studiji Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:111:319953 Rights / Prava: In copyright Download date / Datum preuzimanja: 2021-09-28 Repository / Repozitorij: Repository of University of Zagreb, Centre for Croatian Studies SVEUČILIŠTE U ZAGREBU HRVATSKI STUDIJI Andreja Škrlec RELIGIJA I POGREBNI OBIČAJI TIJEKOM XVIII. DINASTIJE DIPLOMSKI RAD Zagreb, 2018. SVEUČILIŠTE U ZAGREBU HRVATSKI STUDIJI ODSJEK ZA POVIJEST ANDREJA ŠKRLEC RELIGIJA I POGREBNI OBIČAJI TIJEKOM XVIII. DINASTIJE DIPLOMSKI RAD Mentor: doc. dr. sc. Mladen Tomorad Zagreb, 2018. SADRŢAJ 1. UVOD .................................................................................................................................... 3 2. NOVO KRALJEVSTVO (o. 1539. - o. 1069. g. pr. Kr.) ....................................................... 6 3. NEKROPOLE ........................................................................................................................ 9 3.1. Kraljevske nekropole ..................................................................................................... 10 3.1.1. Dra Abu el-Naga ..................................................................................................... 10 3.1.1.1. Amozis - ? ....................................................................................................... -

Donjoy Catalogue

Direct seat valve HX type Direct seat valve has very flexible valve body combination and Various functional configuration, such as aseptic, sterlization,diaphragm type,adjustable valve position, jacket insulatlon, damping buffer,double seat etc. Also can install with automatic positioner, control head, feedback device, position sensor etc. Technical Features • Size: 1/2”-6”, DN10-DN150 • Material: 316L/1.4404, ASME BPE 316L 1.4435 NB2 Fe ≤ 0.5% • Pressure: Vacuum to 10 bar (1.0 MPa) • Temperature: EPDM -20 °C to+ 150°C, Depending on the seal material • Seal: EPDM FKM HNBR PTFE • Connection standard: DIN SMS ISO IDF RJT BS4825 ASME BPE 3A DIN11864 DIN11853 • Connection method: thread, clamp, welding, flange • Drive mode: manual, pneumatic, electric. • Surface: Ra ≤ 0.6 µm; MP = Ra ≤ 0.3 µm; FP = Ra ≤ 0.3 µm • Certification: FDA 177.2600: 3A-53-06: Glass II USP Glass VI Chapter 88: GB4806.11: EG VO/1935-2004: PED/97/23/EC www.kuga-thailand.com I I 46 Direct seat valve Very Flexible Valve Body Combination And Connection Type 20 30 111 211 11 12 112 212 21A 22A 121 221 21 22 122 222 31 32 Different Connection End 1. Vacuum clamp 2. Clamp 3. Welding 4. Flange 5. Aseptic flange 6. Thread 7. Nut 1 2 3 7 6 5 4 47 Recommended direct Valve body adopts clamp type, normally closed and normally open 180° U- turn round seat valve realization, pressure bear ≤ 10bar, size 1/2"-4', DN10-DN100, various controller can be configured. HX-S type HX-Q type Membrane diaphragm Diaphragm divert seal valve can bear pressure ≤ 30bar, shorter direct seat valve length, stainles steel actuator. -

STUDIES in the ARCHAEOLOGY of the VALLEY of the KINGS, With

STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies (Volumes I-II) Volume II: Notes to Text by Carl Nicholas Reeves Thesis submitted for the degree of Doctor of Philosophy School of Oriental Studies University of Durham 1984 The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged. ) 'IV • -‘(- t• CONTENTS OF VOLUME II Notes to preface 1 Notes to introduction 2 Notes to chapter 1 7 Notes to chapter 2 21 Notes to chapter 3 43 Notes to chapter 4 65 Notes to chapter 5 72 Notes to chapter 6 77 Notes to chapter 7 85 Notes to chapter 8 90 Notes to chapter 9 108 Notes to chapter 10 114 Notes to chapter 11 131 Notes to chapter 12 138 Notes to conclusions 152 Notes to appendices 156 Preface 1 Notes 1) Maspero, New Light, 243. 2) TT1: P-M I 2 /i, 1 ff. 3) TT8: ibid., 17 f. 4) Cf. Rhind, Thebes, 62 ff. and passim. 5) Plato, Republic IV, 436a. 6) Cf. Ayrton & Loat, Mahasna, 1 f.; Caminos, in LA II, 866, n. 16. Introduction 2 Notes 1) Following Peet's restoration of the year: Tomb- Robberies, 37. 2) P. Abbott, 2, 1 ff.: ibid., pl. 1. 3) tern7's opinion (cited P-M I 2/ii, 599), that the tomb of Amenophis I has yet to be found, was based upon an identification of the 'house of Amenophis 1.p.h.