2021 Edition

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2021 Transpacific Yacht Race Event Program

TRANSPACTHE FIFTY-FIRST RACE FROM LOS ANGELES 2021 TO HONOLULU 2 0 21 JULY 13-30, 2021 Comanche: © Sharon Green / Ultimate Sailing COMANCHE Taxi Dancer: © Ronnie Simpson / Ultimate Sailing • Hamachi: © Team Hamachi HAMACHI 2019 FIRST TO FINISH Official race guide - $5.00 2019 OVERALL CORRECTED TIME WINNER P: 808.845.6465 [email protected] F: 808.841.6610 OFFICIAL HANDBOOK OF THE 51ST TRANSPACIFIC YACHT RACE The Transpac 2021 Official Race Handbook is published for the Honolulu Committee of the Transpacific Yacht Club by Roth Communications, 2040 Alewa Drive, Honolulu, HI 96817 USA (808) 595-4124 [email protected] Publisher .............................................Michael J. Roth Roth Communications Editor .............................................. Ray Pendleton, Kim Ickler Contributing Writers .................... Dobbs Davis, Stan Honey, Ray Pendleton Contributing Photographers ...... Sharon Green/ultimatesailingcom, Ronnie Simpson/ultimatesailing.com, Todd Rasmussen, Betsy Crowfoot Senescu/ultimatesailing.com, Walter Cooper/ ultimatesailing.com, Lauren Easley - Leialoha Creative, Joyce Riley, Geri Conser, Emma Deardorff, Rachel Rosales, Phil Uhl, David Livingston, Pam Davis, Brian Farr Designer ........................................ Leslie Johnson Design On the Cover: CONTENTS Taxi Dancer R/P 70 Yabsley/Compton 2019 1st Div. 2 Sleds ET: 8:06:43:22 CT: 08:23:09:26 Schedule of Events . 3 Photo: Ronnie Simpson / ultimatesailing.com Welcome from the Governor of Hawaii . 8 Inset left: Welcome from the Mayor of Honolulu . 9 Comanche Verdier/VPLP 100 Jim Cooney & Samantha Grant Welcome from the Mayor of Long Beach . 9 2019 Barndoor Winner - First to Finish Overall: ET: 5:11:14:05 Welcome from the Transpacific Yacht Club Commodore . 10 Photo: Sharon Green / ultimatesailingcom Welcome from the Honolulu Committee Chair . 10 Inset right: Welcome from the Sponsoring Yacht Clubs . -

Northern Paiute and Western Shoshone Land Use in Northern Nevada: a Class I Ethnographic/Ethnohistoric Overview

U.S. DEPARTMENT OF THE INTERIOR Bureau of Land Management NEVADA NORTHERN PAIUTE AND WESTERN SHOSHONE LAND USE IN NORTHERN NEVADA: A CLASS I ETHNOGRAPHIC/ETHNOHISTORIC OVERVIEW Ginny Bengston CULTURAL RESOURCE SERIES NO. 12 2003 SWCA ENVIROHMENTAL CON..·S:.. .U LTt;NTS . iitew.a,e.El t:ti.r B'i!lt e.a:b ~f l-amd :Nf'arat:1.iern'.~nt N~:¥G~GI Sl$i~-'®'ffl'c~. P,rceP,GJ r.ei l l§y. SWGA.,,En:v,ir.e.m"me'Y-tfol I €on's.wlf.arats NORTHERN PAIUTE AND WESTERN SHOSHONE LAND USE IN NORTHERN NEVADA: A CLASS I ETHNOGRAPHIC/ETHNOHISTORIC OVERVIEW Submitted to BUREAU OF LAND MANAGEMENT Nevada State Office 1340 Financial Boulevard Reno, Nevada 89520-0008 Submitted by SWCA, INC. Environmental Consultants 5370 Kietzke Lane, Suite 205 Reno, Nevada 89511 (775) 826-1700 Prepared by Ginny Bengston SWCA Cultural Resources Report No. 02-551 December 16, 2002 TABLE OF CONTENTS List of Figures ................................................................v List of Tables .................................................................v List of Appendixes ............................................................ vi CHAPTER 1. INTRODUCTION .................................................1 CHAPTER 2. ETHNOGRAPHIC OVERVIEW .....................................4 Northern Paiute ............................................................4 Habitation Patterns .......................................................8 Subsistence .............................................................9 Burial Practices ........................................................11 -

Discovering the Lost Race Story: Writing Science Fiction, Writing Temporality

Discovering the Lost Race Story: Writing Science Fiction, Writing Temporality This thesis is presented for the degree of Doctor of Philosophy of The University of Western Australia 2008 Karen Peta Hall Bachelor of Arts (Honours) Discipline of English and Cultural Studies School of Social and Cultural Studies ii Abstract Genres are constituted, implicitly and explicitly, through their construction of the past. Genres continually reconstitute themselves, as authors, producers and, most importantly, readers situate texts in relation to one another; each text implies a reader who will locate the text on a spectrum of previously developed generic characteristics. Though science fiction appears to be a genre concerned with the future, I argue that the persistent presence of lost race stories – where the contemporary world and groups of people thought to exist only in the past intersect – in science fiction demonstrates that the past is crucial in the operation of the genre. By tracing the origins and evolution of the lost race story from late nineteenth-century novels through the early twentieth-century American pulp science fiction magazines to novel-length narratives, and narrative series, at the end of the twentieth century, this thesis shows how the consistent presence, and varied uses, of lost race stories in science fiction complicates previous critical narratives of the history and definitions of science fiction. In examining the implicit and explicit aspects of temporality and genre, this thesis works through close readings of exemplar texts as well as historicist, structural and theoretically informed readings. It focuses particularly on women writers, thus extending previous accounts of women’s participation in science fiction and demonstrating that gender inflects constructions of authority, genre and temporality. -

Store 3 Catalog

LOCATION PRODUCT CODE DESCRIPTION PRODUCT SIZE PRICE STORE #3 705819 10 BARREL CRUSH SOUR MIX 12C 17.49 STORE #3 703556 10 BARREL RASPBERRY SOUR 6C 10.49 STORE #3 704465 10,000 DROPS SPICED RUM 750ML 33.99 STORE #3 700940 1000 STORIES ZINFANDEL * 750ML 19.99 STORE #3 701150 12 CIDER HOUSE BLCK CURRANT 1B 12.99 STORE #3 701820 12 CIDER HOUSE CHESTNUT 1B 11.49 STORE #3 6414 123 TRES ANEJO TEQUILA 750ML 61.99 STORE #3 704020 13 CELSIUS P GRIGIO 750ML 10.99 STORE #3 4556 13 CELSIUS SAUV BLANC 750ML 10.99 STORE #3 7980 14 HANDS CAB 750ML 14.49 STORE #3 8579 14 HANDS HOT TO TROT RED 750ML 11.49 STORE #3 7981 14 HANDS MERLOT 750ML 14.49 STORE #3 7973 14 HANDS MOSCATO 750ML 11.49 STORE #3 7975 14 HANDS PINOT GRIGIO 750ML 11.49 STORE #3 7917 14 HANDS RIESLING 750ML 11.49 STORE #3 706784 1776 JAMES E PEPPER BOUR 750ML 34.99 STORE #3 706785 1776 JAMES E PEPPER RYE 750ML 34.99 STORE #3 703989 1792 BOURBON BOND 750ML 54.99 STORE #3 703566 1792 FULL PROOF SINGLE BAR 750ML 47.99 STORE #3 701887 1792 SINGLE BARREL BOURBON 750ML 47.99 STORE #3 17266 1792 SMALL BATCH BOURBON 750ML 30.99 STORE #3 6252 1800 REPOSADO 375 ML 15.99 STORE #3 6219 1800 REPOSADO 750ML 27.99 STORE #3 700280 1800 SILVER 375 ML 14.99 STORE #3 705486 1800 SILVER 50 ML 3.49 STORE #3 6222 1800 SILVER 750ML 27.99 STORE #3 6253 1800 SILVER TEQUILA 1.75 L 43.99 STORE #3 2958 1809 BERLINER WEISSE 1B 6.99 STORE #3 702967 1865 CABERNET SAUVIGNON 750ML 19.97 STORE #3 700832 19 CRIMES CAB 750ML 11.99 STORE #3 400000009919 19 CRIMES CALI RED 750ML 14.49 STORE #3 400000011639 19 CRIMES CHARD 375ML -

Board Certified Fellows

AMERICAN BOARD OF MEDICOLEGAL DEATH INVESTIGATORS Certificant Directory As of September 30, 2021 BOARD CERTIFIED FELLOWS Addison, Krysten Leigh (Inactive) BC2286 Allmon, James L. BC855 Travis County Medical Examiner's Office Sangamon County Coroner's Office 1213 Sabine Street 200 South 9th, Room 203 PO Box 1748 Springfield, IL 62701 Austin, TX 78767 Amini, Navid BC2281 Appleberry, Sherronda BC1721 Olmsted Medical Examiner's Office Adams and Broomfield County Office of the Coroner 200 1st Street Southwest 330 North 19th Avenue Rochester, MN 55905 Brighton, CO 80601 Applegate, MD, David T. BC1829 Archer, Meredith D. BC1036 Union County Coroner's Office Mohave County Medical Examiner 128 South Main Street 1145 Aviation Drive Unit A Marysville, OH 43040 Lake Havasu, AZ 86404 Bailey, Ted E. (Inactive) BC229 Bailey, Sanisha Renee BC1754 Gwinnett County Medical Examiner's Office Virginia Office of the Chief Medical Examiner 320 Hurricane Shoals Road, NE Central District Lawrenceville, GA 30046 400 East Jackson Street Richmond, VA 23219 Balacki, Alexander J BC1513 Banks, Elsie-Kay BC3039 Montgomery County Coroner's Office Maine Office of the Chief Medical Examiner 1430 Dekalb Street 30 Hospital Street PO Box 311 Augusta, ME 04333 Norristown, PA 19404 Bautista, Ian BC2185 Bayer, Lindsey A. BC875 New York City Office of Chief Medical Examiner District 5 and 24 Medical Examiner Office 421 East 26th Street 809 Pine Street New York, NY 10016 Leesburg, FL 34756 Beck, Shari L BC327 Beckham, Phinon Phillips BC2305 Sedgwick Co Reg. Forensic Science Center Virginia Office of the Chief Medical Examiner 1109 N. Minneapolis Northern District Wichita, KS 67214 10850 Pyramid Place, Suite 121 Manassas, VA 20110 Bednar Keefe, Gale M. -

LPIB Issue 164 (April 2021)

THE CHICXULUB IMPACT CRATER: Producing a Cradle of Life in the Midst of a Global Calamity Featured Story | From the Desk of Lori Glaze | Meeting Highlights | News from Space | Spotlight on Education In Memoriam | Milestones | New and Noteworthy | Calendar LUNAR AND PLANETARY INFORMATION BULLETIN April 2021 Issue 164 FEATURED STORY THE CHICXULUB IMPACT CRATER: Producing a Cradle of Life in the Midst of a Global Calamity DAVID A. KRING, LUNAR AND PLANETARY INSTITUTE Expedition 364 mission patch Introduction when the International Ocean Discov- an area that had been a stable sediment ery Program (IODP) and International catchment for over 100 million years? Strategically located scientific drilling Continental Scientific Drilling Program Clues began to emerge when the core can be used to tap the Earth for evi- (ICDP) initiated a new campaign with was analyzed. Logging revealed chem- dence of evolutionary upheavals that the call sign Expedition 364. Drilling ical and petrological variations on the transformed the planet. A good example from a marine platform a few meters granitic theme, plus felsite and dolerite is the Yucatán-6 borehole in Mexico above the sea surface, the new borehole intrusions, in a granitoid rock sequence that recovered rock samples from 1.2 reached a depth of 1335 meters be- that represented continental crust that and 1.3 kilometers beneath Earth’s neath the sea floor (mbsf). The borehole had been assembled through a series of surface. I used those samples 30 years penetrated seafloor sediments that bury tectonic events over more than a billion ago to show that a buried, geophysical- the crater, finally reaching impactites at years. -

Summary of Sexual Abuse Claims in Chapter 11 Cases of Boy Scouts of America

Summary of Sexual Abuse Claims in Chapter 11 Cases of Boy Scouts of America There are approximately 101,135sexual abuse claims filed. Of those claims, the Tort Claimants’ Committee estimates that there are approximately 83,807 unique claims if the amended and superseded and multiple claims filed on account of the same survivor are removed. The summary of sexual abuse claims below uses the set of 83,807 of claim for purposes of claims summary below.1 The Tort Claimants’ Committee has broken down the sexual abuse claims in various categories for the purpose of disclosing where and when the sexual abuse claims arose and the identity of certain of the parties that are implicated in the alleged sexual abuse. Attached hereto as Exhibit 1 is a chart that shows the sexual abuse claims broken down by the year in which they first arose. Please note that there approximately 10,500 claims did not provide a date for when the sexual abuse occurred. As a result, those claims have not been assigned a year in which the abuse first arose. Attached hereto as Exhibit 2 is a chart that shows the claims broken down by the state or jurisdiction in which they arose. Please note there are approximately 7,186 claims that did not provide a location of abuse. Those claims are reflected by YY or ZZ in the codes used to identify the applicable state or jurisdiction. Those claims have not been assigned a state or other jurisdiction. Attached hereto as Exhibit 3 is a chart that shows the claims broken down by the Local Council implicated in the sexual abuse. -

2019 National Tournament Results Sunday June 16Th – Friday June

2019 National Tournament Results Sunday June 16th – Friday June 21st, 2019 Hosted in Dallas, TX 2019 National Speech & Debate Tournament Bruno E. Jacob / Pi Kappa Delta Trophy 1 1884 Apple Valley HS MN 2 1867 Eagan HS MN 3 1828 Bellarmine College Preparatory CA 4 1812 James Logan HS CA 5 1781 Plano Senior TX 6 1750 Regis High School NY 7 1670 Albuquerque Academy NM 8 1680 Glenbrook North HS IL 9 1661 Iowa City West IA 10 1636 Dowling Catholic HS IA 2019 National Speech & Debate Tournament Senator Karl E. Mundt Sweepstakes Trophy In Congressional Debate 1 243 Bellaire TX 2 228 Riverside HS SC 3 221 Asheville HS NC 4 220 Adlai E Stevenson High School IL 5 208 Western High School FL 2019 National Speech & Debate Tournament Schools of Outstanding Distinction Archbishop Mitty High School (CA) Bellarmine College Prep (CA) Cypress Bay HS (FL) Eagan HS (MN) George Washington (CO) King HS (FL) The Harker School (CA) Plano West (TX) Monte Vista (CA) Valley International Prep (CA) 2019 National Speech & Debate Tournament Schools of Excellence in Speech Apple Valley HS (MN) Belleville West HS (IL) Blue Springs HS (MO) Comeaux HS (LA) Danville HS (KY) Eastview HS (MN) Gabrielino HS (CA) Harlingen HS South (TX) J Frank Dobie HS (TX) James Logan HS (CA) Jasper HS (TX) Lakeville North HS (MN) Millard North HS (NE) Miramar High School (FL) Moorhead HS (MN) Perry HS (OH) Phoenix Country Day School (AZ) Shrewsbury (MA) Theodore Roosevelt High School (IA) Westmoore HS (OK) Woodbury HS (MN) 2019 National Speech & Debate Tournament Schools of Honor in Speech -

Comparison of Central Peak Craters on the Moon and Ganymede

Meteoritics & Planetary Science 43, Nr 12, 1–crossref to last page (2008) AUTHOR’S Abstract available online at http://meteoritics.org PROOF The effect of target properties on crater morphology: Comparison of central peak craters on the Moon and Ganymede Veronica J. BRAY1, 3*, Gareth S. COLLINS1, Joanna V. MORGAN1, and Paul M. SCHENK2 1Earth Science and Engineering Department, Imperial College London, Exhibition Road, London, SW7 2BP, UK 2Lunar and Planetary Institute, 3600 Bay Area Blvd., Houston, Texas, 77058, USA 3Lunar and Planetary Laboratory, University of Arizona, Tucson, Arizona, 85721, USA *Corresponding author. E-mail: [email protected] (Received 23 March 2008; revision accepted 01 December 2008) Abstract–We examine the morphology of central peak craters on the Moon and Ganymede in order to investigate differences in the near-surface properties of these bodies. We have extracted topographic profiles across craters on Ganymede using Galileo images, and use these data to compile scaling trends. Comparisons between lunar and Ganymede craters show that crater depth, wall slope and amount of central uplift are all affected by material properties. We observe no major differences between similar-sized craters in the dark and bright terrain of Ganymede, suggesting that dark terrain does not contain enough silicate material to significantly increase the strength of the surface ice. Below crater diameters of ∼12 km, central peak craters on Ganymede and simple craters on the Moon have similar rim heights, indicating comparable amounts of rim collapse. This suggests that the formation of central peaks at smaller crater diameters on Ganymede than the Moon is dominated by enhanced central floor uplift rather than rim collapse. -

Natural Resource Condition Assessment

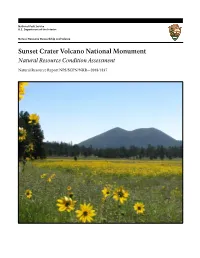

National Park Service U.S. Department of the Interior Natural Resource Stewardship and Science Sunset Crater Volcano National Monument Natural Resource Condition Assessment Natural Resource Report NPS/SCPN/NRR—2018/1837 ON THIS PAGE Desert globemallow. Photo Credit: NPS ON THE COVER A view of yellow sunflowers with Sunset Crater Volcano in the background. Photo Credit: NPS Sunset Crater Volcano National Monument Natural Resource Condition Assessment Natural Resource Report NPS/SCPN/NRR—2018/1837 Author Name(s) Lisa Baril1, Patricia Valentine-Darby1, Kimberly Struthers1, Paul Whitefield2 , Kirk Anderson3, Mark Brunson1 1Utah State University Department of Environment and Society Logan, Utah 2National Park Service Flagstaff Area National Monuments Flagstaff, Arizona 3Museum of Northern Arizona Flagstaff, Arizona Editing and Design Kimberly Struthers1 December 2018 U.S. Department of the Interior National Park Service Natural Resource Stewardship and Science Fort Collins, Colorado The National Park Service, Natural Resource Stewardship and Science office in Fort Collins, Colorado, publishes a range of reports that address natural resource topics. These reports are of interest and applicability to a broad audience in the National Park Service and others in natural resource management, including scientists, conservation and environmental constituencies, and the public. The Natural Resource Report Series is used to disseminate comprehensive information and analysis about natural resources and related topics concerning lands managed by the National Park Service. The series supports the advancement of science, informed decision-making, and the achievement of the National Park Service mission. The series also provides a forum for presenting more lengthy results that may not be accepted by publications with page limitations. -

1 the Lifecycle of Hollows on Mercury

The Lifecycle of Hollows on Mercury: An Evaluation of Candidate Volatile Phases and a Novel Model of Formation. 1 1 2 3 M. S. Phillips , J. E. Moersch , C. E. Viviano , J. P. Emery 1Department of Earth and Planetary Sciences, University of Tennessee, Knoxville 2Planetary Exploration Group, Johns Hopkins University Applied Physics Laboratory 3Department of Astronomy and Planetary Sciences, Northern Arizona University Corresponding author: Michael Phillips ([email protected]) Keywords: Mercury, hollows, thermal model, fumarole. Abstract On Mercury, high-reflectance, flat-floored depressions called hollows are observed nearly globally within low-reflectance material, one of Mercury’s major color units. Hollows are thought to be young, or even currently active, features that form via sublimation, or a “sublimation-like” process. The apparent abundance of sulfides within LRM combined with spectral detections of sulfides associated with hollows suggests that sulfides may be the phase responsible for hollow formation. Despite the association of sulfides with hollows, it is still not clear whether sulfides are the hollow-forming phase. To better understand which phase(s) might be responsible for hollow formation, we calculated sublimation rates for 57 candidate hollow-forming volatile phases from the surface of Mercury and as a function of depth beneath regolith lag deposits of various thicknesses. We found that stearic acid (C18H36O2), fullerenes (C60, C70), and elemental sulfur (S) have the appropriate thermophysical properties to explain hollow formation. Stearic acid and fullerenes are implausible hollow-forming phases because they are unlikely to have been delivered to or generated on Mercury in high enough volume to account for hollows. -

2021 Finalist Directory

2021 Finalist Directory April 29, 2021 ANIMAL SCIENCES ANIM001 Shrimply Clean: Effects of Mussels and Prawn on Water Quality https://projectboard.world/isef/project/51706 Trinity Skaggs, 11th; Wildwood High School, Wildwood, FL ANIM003 Investigation on High Twinning Rates in Cattle Using Sanger Sequencing https://projectboard.world/isef/project/51833 Lilly Figueroa, 10th; Mancos High School, Mancos, CO ANIM004 Utilization of Mechanically Simulated Kangaroo Care as a Novel Homeostatic Method to Treat Mice Carrying a Remutation of the Ppp1r13l Gene as a Model for Humans with Cardiomyopathy https://projectboard.world/isef/project/51789 Nathan Foo, 12th; West Shore Junior/Senior High School, Melbourne, FL ANIM005T Behavior Study and Development of Artificial Nest for Nurturing Assassin Bugs (Sycanus indagator Stal.) Beneficial in Biological Pest Control https://projectboard.world/isef/project/51803 Nonthaporn Srikha, 10th; Natthida Benjapiyaporn, 11th; Pattarapoom Tubtim, 12th; The Demonstration School of Khon Kaen University (Modindaeng), Muang Khonkaen, Khonkaen, Thailand ANIM006 The Survival of the Fairy: An In-Depth Survey into the Behavior and Life Cycle of the Sand Fairy Cicada, Year 3 https://projectboard.world/isef/project/51630 Antonio Rajaratnam, 12th; Redeemer Baptist School, North Parramatta, NSW, Australia ANIM007 Novel Geotaxic Data Show Botanical Therapeutics Slow Parkinson’s Disease in A53T and ParkinKO Models https://projectboard.world/isef/project/51887 Kristi Biswas, 10th; Paxon School for Advanced Studies, Jacksonville,