Datasheet Search Site

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

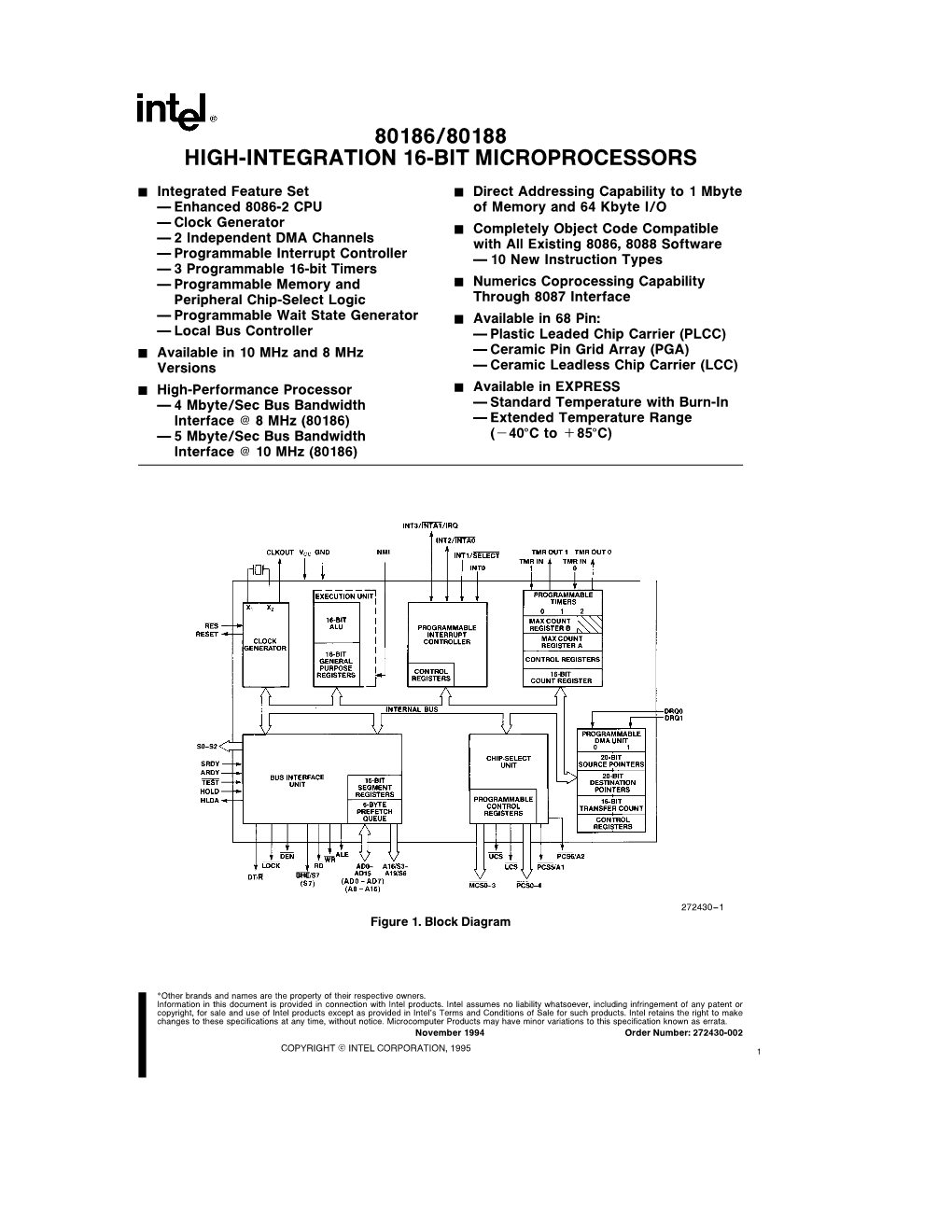

CISC Processor - Intel X86

Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO CISC Processor - Intel x86 This chapter will introduce the CISC processors evolution. We will try to illustrate the history on one typical processor, because the comparison of multiple processors simultaneously would not be clear for readers. But the selection of one typical processor is complicated due to a variety of products and manufactures in the past 30 years. We have decided to describe in this presentation one of the best- known and longest mass-produced processors in existence. We definitely do not want to say that it is the best technology or that these are processors with the highest performance! The Intel x86 processors are the selected product line. Intel 8080 (Year-Technology-Transistors-Frequency-Data bus-Address Bus) Y: 1974 T: NMOS 6μm Tr: 6000 F: 2MHz D: 8b A: 16b This 8 bit processor is not directly the first member of x86 series, but it can not be skipped. It is one of the first commercially successful microprocessors. This microprocessor became the basis for a number of the first single-board computers and its instruction set inspired other manufacturers to develop 8-bit processors. -

Computing :: Operatingsystems :: DOS Beyond 640K 2Nd

DOS® Beyond 640K 2nd Edition DOS® Beyond 640K 2nd Edition James S. Forney Windcrest®/McGraw-Hill SECOND EDITION FIRST PRINTING © 1992 by James S. Forney. First Edition © 1989 by James S. Forney. Published by Windcrest Books, an imprint of TAB Books. TAB Books is a division of McGraw-Hill, Inc. The name "Windcrest" is a registered trademark of TAB Books. Printed in the United States of America. All rights reserved. The publisher takes no responsibility for the use of any of the materials or methods described in this book, nor for the products thereof. Library of Congress Cataloging-in-Publication Data Forney, James. DOS beyond 640K / by James S. Forney. - 2nd ed. p. cm. Rev. ed. of: MS-DOS beyond 640K. Includes index. ISBN 0-8306-9717-9 ISBN 0-8306-3744-3 (pbk.) 1. Operating systems (Computers) 2. MS-DOS (Computer file) 3. PC -DOS (Computer file) 4. Random access memory. I. Forney, James. MS-DOS beyond 640K. II. Title. QA76.76.063F644 1991 0058.4'3--dc20 91-24629 CIP TAB Books offers software for sale. For information and a catalog, please contact TAB Software Department, Blue Ridge Summit, PA 17294-0850. Acquisitions Editor: Stephen Moore Production: Katherine G. Brown Book Design: Jaclyn J. Boone Cover: Sandra Blair Design, Harrisburg, PA WTl To Sheila Contents Preface Xlll Acknowledgments xv Introduction xvii Chapter 1. The unexpanded system 1 Physical limits of the system 2 The physical machine 5 Life beyond 640K 7 The operating system 10 Evolution: a two-way street 12 What else is in there? 13 Out of hiding 13 Chapter 2. -

Communication Theory II

Microprocessor (COM 9323) Lecture 2: Review on Intel Family Ahmed Elnakib, PhD Assistant Professor, Mansoura University, Egypt Feb 17th, 2016 1 Text Book/References Textbook: 1. The Intel Microprocessors, Architecture, Programming and Interfacing, 8th edition, Barry B. Brey, Prentice Hall, 2009 2. Assembly Language for x86 processors, 6th edition, K. R. Irvine, Prentice Hall, 2011 References: 1. Computer Architecture: A Quantitative Approach, 5th edition, J. Hennessy, D. Patterson, Elsevier, 2012. 2. The 80x86 Family, Design, Programming and Interfacing, 3rd edition, Prentice Hall, 2002 3. The 80x86 IBM PC and Compatible Computers, Assembly Language, Design, and Interfacing, 4th edition, M.A. Mazidi and J.G. Mazidi, Prentice Hall, 2003 2 Lecture Objectives 1. Provide an overview of the various 80X86 and Pentium family members 2. Define the contents of the memory system in the personal computer 3. Convert between binary, decimal, and hexadecimal numbers 4. Differentiate and represent numeric and alphabetic information as integers, floating-point, BCD, and ASCII data 5. Understand basic computer terminology (bit, byte, data, real memory system, protected mode memory system, Windows, DOS, I/O) 3 Brief History of the Computers o1946 The first generation of Computer ENIAC (Electrical and Numerical Integrator and Calculator) was started to be used based on the vacuum tube technology, University of Pennsylvania o1970s entire CPU was put in a single chip. (1971 the first microprocessor of Intel 4004 (4-bit data bus and 2300 transistors and 45 instructions) 4 Brief History of the Computers (cont’d) oLate 1970s Intel 8080/85 appeared with 8-bit data bus and 16-bit address bus and used from traffic light controllers to homemade computers (8085: 246 instruction set, RISC*) o1981 First PC was introduced by IBM with Intel 8088 (CISC**: over 20,000 instructions) microprocessor oMotorola emerged with 6800. -

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS48, MCS51, 80X86 up To

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS-48, MCS-51, 80x86 up to 80386, 80860, 80960, SA-110 Intel 80486: 80486, 80486 overdrive Intel Pentium: Pentium, Pentium MMX, Pentium Overdrive, Mobile Pentium Intel Pentium II: Boxed Pentium II, Boxed Pentium Pro, Mobile Pentium II and Celeron modules Intel Pentium III: Pentium III markings, Mobile Pentium III and Celeron modules Intel modern CPUs: Pentium II, Pentium III, Pentium 4, Core Duo, Core Solo, Core 2 Duo, Core 2 Quad, Core 2 Extreme, Xeon, Pentium Dual Core, Celeron, Celeron D, Celeron Dual Core Intel 287 adapter Intel 3002 Intel 478-pin FC-PGA Thermal Sample Intel 80188 Intel 80486 Mech sample Intel 8080A Intel 80P23T-25 Intel A100 UM80536UC600512 Intel A110 UM80536UC800512 Intel A80186 Intel A80186-10 Intel A80188 Intel A80188-10 Intel A80286-10 Intel A80286-12 Intel A80286-8 Intel A80376-16 Intel A80376-20 Intel A80386-16 Intel A80386-20 Intel A80386-25 Intel A80386DX-16 Intel A80386DX-16 IV Intel A80386DX-20 Intel A80386DX-20 IV Intel A80386DX-25 Intel A80386DX-25 IV Intel A80386DX-33 IV Intel A80386DX16 Intel A80386EXI Intel A80387-16 Intel A80387-20 Intel A80387-20B Intel A80387-25 Intel A80387DX-16 (with logo) Intel A80387DX-16-33 Intel A80387DX-20 Intel A80387DX-25 Intel A80387DX-33 Intel A80486DX-33 Intel A80486DX-50 Intel A80486DX2-50 Intel A80486DX2-66 Intel A80486DX4-100 Intel A80486DX4-75 Intel A80486SX-16 Intel A80486SX-20 Intel A80486SX-25 Intel A80486SX-33 Intel A80486SX2-50 Intel A80487SX Intel A80860XP-40 Intel A80860XP-50 Intel A80860XR-25 Intel A80860XR-33 Intel -

Mikroişlemcilerin Tarihi

D9 Mikroişlemcilerin Tarihi 1 D9 Mikroişlemcilerin Tarihi Mikroişlemcili sistemlerin kalbi olarak kabul edilen mikroişlemciler, genel amaçlı elemanlardır ve farklı uygulamalarda amaca uygun olarak kullanılırlar. Kullandığımız bilgisayarlar ister masaüstü, ister sunucu isterse de dizüstü bilgisayar olsun tüm cihazlarda temel eleman mikroişlemcidir. 2 D9 Mikroişlemcilerin Tarihi Diğer taraftan kullandığımız mikroişlemci bir Pentium, Athlon, PowerPC, SPARC veya Alpha yada herhangi bir marka olabilir, ancak tüm işlemciler benzer yöntemlerle benzer işler gerçekleştirir. İşlemleri yerine getirmede mantıksal devreleri kullanan mikroişlemcilerde temel elektronik eleman olarak transistörler kullanılır. 3 D9 Mikroişlemcilerin Tarihi Mikroişlemcili sistemlerin ve bilgisayarların en önemli parçası olan bu eleman başlangıçtan günümüze kadar hızlı bir gelişim süreci sergilemiştir. 8086 işlemcisiyle beraber Intel ailesinin mikroişlemcilerde kullandığı mimariye Intel Mimarisi (Intel Architecture-IA) denilmiştir. 4 D9 Mikroişlemcilerin Tarihi Mikroişlemcileri bir kerede işleyebildikleri bit sayısına göre sınıflandırmaya tabi tutarsak; – 8 bitlik mikroişlemciler – 16 bitlik mikroişlemciler – 32 bitlik mikroişlemciler – 64 bitlik mikroişlemciler Şeklinde sınıflama yapabiliriz. 5 D9 Birinci Kuşak Mikroişlemciler Bu kuşak mikroişlemciler eski orijinal IBM PC, XT tipi ve benzer makinalarda kullanılmıştır. O günlerin şartlarına göre mükemmel fakat günümüze göre oldukça sınırlı yeteneklere sahip bu makinelerle günümüz makineleri kıyaslanırsa çok ilkel -

Prozessorenliste

Fach Bezeichnung Stepping Taktfrequenz Anmerkung 1A Intel C4001 7347 0,74 MHz ROM Intel P4002-1 0488D RAM Intel D4002-2 X1191128 RAM Intel P4003 F8956 Shift Register Intel P4004 5199W Prozessor Intel P1101A 7485 MOS SRAM 1B Intel D8008 I1220098 Intel P4040 5869W 1C Intel D3001 I3320035 Intel D3002 I3370036 1D Intel P8259A-2 L8360894 10 MHz PIC Intel P8254-2 L0421586 10 MHz PIT 1E Intel P8080A 2194B 2 MHz Intel P8086-2 L4151756B 5 MHz 1F Intel P8088 L5500345 5 MHz Intel C8087 L5380043 Math. CP 1G Intel P8031 L61100346 12 MHz Intel P8085 L5500055 3 MHz 1H Intel 8237A L0311554 5 MHz DMA Contr. Intel P8274 L7440107 MPSC Intel D8742 U2420277 12 MHz 8 Bit SMC 2A AMD N80186, N80186 91939DFE7 10 MHz, 12 MHz 335BCWD AMD 80286, Intel 80188 918KPSC L5322539 2B Intel 80286, 80286 L8500401 6, 12 MHz L9080860 2C Intel 80287 L9190444 10 MHz Math. CP 2D Intel 80286 L2140286 6 MHz Harris 80286 F3360 16MHz 2E Intel NG80386SX L1121576 16 MHz 2F Intel A82596SX SZ649 20 MHz 2G Intel 80486SX SX676 25 MHz 2H Intel A80501 SX835 60 MHz FDIV Bug 3A Intel Pentium II SL357 400 MHz Deschutes 3B Intel 80386DX SX366 33 MHz IIT 3C87 KY9220 40 MHz Math. CP 3C IT´s ST 80486DX4 100 MHz 3D UMC GREEN CPU U5S 9439K 33 MHz Not for US Sale 3E Intel 80386DX/DXL SX218 25 MHz IIT 3C87 ID9143.8 33MHz Math. CP 3F M27128AFI 88723S EPROM 3G Intel Pentium 4 SL79L 3,0 GHz Prescott Intel Pentium 4 SL6RZ 2,4 GHz Nortwood 3H Intel Celeron SL2WM 300 MHz Mendocino 4A Intel Pentium II SL357 400 MHz Deschutes 4B Intel i80960 L8373305B0 33 MHz RISC 4C Intel i80860XR SX438 40 MHz RISC 4D Intel -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

Evolution of the Pentium

Chapter 7B – The Evolution of the Intel Pentium This chapter attempts to trace the evolution of the modern Intel Pentium from the earliest CPU chip, the Intel 4004. The real evolution begins with the Intel 8080, which is an 8–bit design having features that permeate the entire line. Our discussion focuses on three organizations. IA–16 The 16–bit architecture found in the Intel 8086 and Intel 80286. IA–32 The 32–bit architecture found in the Intel 80386, Intel 80486, and most variants of the Pentium design. IA–64 The 64–bit architecture found in some high–end later model Pentiums. The IA–32 has evolved from an early 4–bit design (the Intel 4004) that was first announced in November 1971. At that time, memory came in chips no larger than 64 kilobits (8 KB) and cost about $1,600 per megabyte. Before moving on with the timeline, it is worth recalling the early history of Intel. Here, we quote extensively from Tanenbaum [R002]. “In 1968, Robert Noyce, inventor of the silicon integrated circuit, Gordon Moore, of Moore’s law fame, and Arthur Rock, a San Francisco venture capitalist, formed the Intel Corporation to make memory chips. In the first year of operation, Intel sold only $3,000 worth of chips, but business has picked up since then.” “In September 1969, a Japanese company, Busicom, approached Intel with a request for it to manufacture twelve custom chips for a proposed electronic calculator. The Intel engineer assigned to this project, Ted Hoff, looked at the plan and realized that he could put a 4–bit general–purpose CPU on a single chip that would do the same thing and be simpler and cheaper as well. -

Dstni-LX Data Book

DSTni-LX Data Book Revision F Part Number GC-900-252 Copyright and Trademark © 2003 Grid Connect, Inc. All rights reserved. No part of this manual may be reproduced or transmitted in any form for any purpose other than the purchaser's personal use, without the express written permission of Grid Connect, Inc. Grid Connect, Inc. has made every effort to provide completeness and accuracy of this material, but makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability or fitness for a particular purpose. In no event shall Grid Connect, Inc. be liable for any incidental, special, indirect, or consequential damages whatsoever included but not limited to lost profits arising out of errors or omissions in this manual or the information contained herein. Grid Connect, Inc. products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of a Grid Connect, Inc. product could create a situation where personal injury, death, or severe property or environmental damage may occur. Grid Connect, Inc. reserves the right to discontinue or make changes to its products at any time without notice. Grid Connect and the Grid Connect logo, and combinations thereof are registered trademarks of Grid Connect, Inc. DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered trademark of Xerox Corporation. Am186 is a trademark of Advanced Micro Devices, Inc. -

Μc/OS-II User's Manual 1

µC/OS-II TM The Real-Time Kernel User’s Manual Jean J. Labrosse Weston, FL 33326 µC/OS-II User's Manual 1. µC/OS-II User Manual . 2 1.1 Preface . 3 1.2 Getting Started with µC/OS-II . 8 1.3 Real-Time Systems Concepts . 45 1.4 Kernel Structure . 94 1.5 Task Management . 151 1.6 Time Management . 183 1.7 Timer Management . 193 1.8 Event Control Blocks . 205 1.9 Semaphore Management . 219 1.10 Mutual Exclusion Semaphores . 235 1.11 Event Flag Management . 256 1.12 Message Mailbox Management . 285 1.13 Message Queue Management . 305 1.14 Memory Management . 333 1.15 Porting µC/OS-II . 350 1.16 80x86 Port with Emulated FP Support . 413 1.17 80x86 Port with Hardware FP Support . 460 1.18 Thread Safety of the Compiler’s Run-Time Library . 492 1.19 µC/OS-II API Reference . 500 1.20 µC/OS-II Configuration Manual . 670 1.21 PC Services . 697 1.22 C Coding Conventions . 724 1.23 Licensing Policy for µC/OS-II . 739 1.24 µC/OS-II Quick Reference . 740 1.25 TO Utility . 750 1.26 Bibliography . 752 µC/OS-II User Manual µC/OS-II User's Manual µC/OS-II User Manual This book describes the design and implementation of µC/OS-II (pronounced “Micro C O S 2”), which stands for Micro-Controller Operating System Version 2. µC/OS-II is a completely portable, ROMable, scalable, preemptive, real-time, multitasking kernel. µC/OS-II is written in ANSI C and contains a small portion of assembly language code to adapt it to different processor architectures. -

![CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU](https://docslib.b-cdn.net/cover/8530/cpu-history-tualatin-banias-dothan-yonah-jonah-conroe-allendale-yorkfield-xe-intel-created-pentium-from-quad-core-cpu-3058530.webp)

CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU

2nd Generation 4th Generation 5th Generation 6th Generation 7th Generation 3rd Generation Intel Pentium III-S Intel Pentium-M (Centrino) Intel Pentium-M (Centrino) Intel Core Duo (Viiv) Intel Core 2 Duo (Viiv)/Xeon Intel Core 2 Duo (Viiv) Intel Core 2 Extreme (Viiv) Intel had the first consumer CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel created Pentium (from quad-core CPU. x86/CISC Microprocessors Greek penta which means (2001) (2003) (2004) (2006) (2006) (2007) (2007) 1st Generation Intel Pentium II Xeon Intel Pentium III Xeon Centrino is not a CPU; it is Begin Core five) to distinguish the Intel [P6] [Tanner] a mobile Intel CPU paired nomeclature brand from clones. Names (1998) (1999) Intel Celeron with an Intel Wi-Fi adapter. Intel Celeron Intel Core Solo can be copyrighted, product [Tualeron] [Dothan-1024] Intel Xeon LV Intel Celeron Intel Celeron [Yonah] ID's cannot. (2001) (2004) [Sossaman] [Banias-512] [Shelton (Banias-0)] (2006) (2006) Intel Core 2 Duo Intel Core 2 Extreme Intel Celeron Intel 80386 DX Intel 80486 DX Intel Pentium Intel Pentium Pro Intel Pentium II Intel Pentium II Intel Pentium III Intel Pentium III Intel Pentium 4 Intel Pentium 4 (2004) (2004) Intel Pentium 4 Intel Pentium 4 Intel 4004 Intel 8008 Intel 8086 Intel 80286 [Conroe XE] [Conroe-L] [P3] [P4] [P5/P54/P54C] [P6] [Klamath] [Deuschutes] [Katmai] [Coppermine] [Williamette] [Northwood] [Prescott] [Cedar Mill] END-OF-LINE (Centrino Duo) (1971) (1972) (1978) (1982) (2006) (2007) (1985) (1989) (1993) (1995) (1997) (1998) (1999) (1999) (2000) (2002) (2004) (2006) [Merom] (2006) Yonah is Hebrew for Jonah. -

Uma Abordagem De Escalonamento Heterogêneo Preemptivo E Não Preemptivo Para Sistemas De Tempo Real Com Garantia Em Multiprocessadores

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Repositório Institucional da UFSC UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE AUTOMAÇÃO E SISTEMAS Renan Augusto Starke UMA ABORDAGEM DE ESCALONAMENTO HETEROGÊNEO PREEMPTIVO E NÃO PREEMPTIVO PARA SISTEMAS DE TEMPO REAL COM GARANTIA EM MULTIPROCESSADORES Florianópolis 2012 Renan Augusto Starke UMA ABORDAGEM DE ESCALONAMENTO HETEROGÊNEO PREEMPTIVO E NÃO PREEMPTIVO PARA SISTEMAS DE TEMPO REAL COM GARANTIA EM MULTIPROCESSADORES Dissertação submetida ao programa de Pós- Graduação em Engenharia de Automação e Sistemas para a obtenção do Grau de Mestre em Engenharia de Automação e Sis- temas. Orientador: Rômulo Silva de Oliveira, Dr. Florianópolis 2012 Catalogação na fonte pela Biblioteca Universitária da Universidade Federal de Santa Catarina S795a Starke, Renan Augusto Uma abordagem de escalonamento heterogêneo preemptivo e não preemptivo para sistemas de tempo real com garantia em multiprocessadores [dissertação] / Renan Augusto Starke ; orientador, Rômulo Silva de Oliveira. - Florianópolis, SC, 2012. 200 p.: il., grafs., tabs. Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia de Automação e Sistemas. Inclui referências 1. Engenharia. de sistemas. 2. Automação. 3. Multiprocessadores. 4. Escalonamento. 5. Memória cache. I. Oliveira, Rômulo Silva de. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia de Automação e Sistemas. III. Título. CDU 621.3-231.2(021) Renan Augusto Starke UMA ABORDAGEM DE ESCALONAMENTO HETEROGÊNEO PREEMPTIVO E NÃO PREEMPTIVO PARA SISTEMAS DE TEMPO REAL COM GARANTIA EM MULTIPROCESSADORES Esta Dissertação foi julgada aprovada para a obtenção do Título de “Mestre em Engenharia de Automação e Sistemas”, e aprovada em sua forma final pelo programa de Pós-Graduação em Engenharia de Automação e Siste- mas.