Microprogramming and Its Relationship to Emulation and Technology*

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

A Regression Method

Journal of Automatic Chemistry/Journal of Clinical Laboratory Automation, Volume 8, Number (January-March 1986), pages 28-31 Treatment of super oxide dismutase assay by a regression method Ph. Nirde for the solution of systems of non-singular homogenous Centre d'immunologie & de biologie parasitaire, Unit[ mixte INSERM U167, linear equations. The 'MAT INV' matrix statement CNRS 624, Institute Pasteur, BP 245, 59019 Lille Cedex, France causes matrix inversion by the Gauss-Jordan elimination method. A matrix can be inverted in a significantly shorter time than is possible with BASIC programs. Introduction Indeed, whereas other minicomputers store their pro- gram text exactly as it is entered by the programmer, the The superoxide dismutase (SOD, EC 1.15.1.1) is a widely WANG BASIC interpreter converts into one-byte 'text distributed enzyme in all aerobic cells [1 and 2]. It is the atom' each word of the text program. Thus, the atomized principal protective enzyme against oxygen toxicity and lines permit faster program executionnlines are more acts by catalysing the removal of superoxide radical compact and can be more rapidly scanned, for example, (02--) [3 and 4]. The assay of SOD using Xanthine- inverting a 7 x 7 matrix requires 0"20 s. Because no files Xanthine oxidase-Ferricytochrome C was described by are used for this logiciel, this program can be easily McCord and Fridovich in 1969 [5]. Since, this spectro- adapted to BASIC microsoft language. scopic method has been in use for SOD studies in both the medicine and biology. The assay is based on the rate of reduction of ferricyto- Mathematical expressions chrome C measured spectrophotometrically, but this rate of reduction is not proportional to the amount of enzyme Rate of reduction offerricytochrome C: least squares estimation added. -

Toy BASIC Reference Manual

Toy BASIC Reference Manual Steve Toner Revision 1.0 June 2017 Copyright © 2017 by Stephen G. Toner [email protected] All rights reserved. This book or any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of the publisher except for the use of brief quotations in a book review or scholarly journal. Conventions The following conventions are used in this document: Literal text (e.g., a keyword or command) is shown in ALL CAPS. Some command or statements fields are shown in angle brackets: <line> is a line number, from 1-9999 <expr> is a numeric expression <progname> is a program name <svar> is a (scalar) variable name from A-Z <avar> is an array variable name from A-Z <var> is either a scalar variable, <var>, or an array reference, <avar>(<expr>) <val> is a numeric literal <string> is a string literal enclosed in quotes (“) <text> is a text string NOT enclosed in quotes Optional Fields Optional parameters are enclosed in square brackets: LIST [<line>] Multiple Valid Parameters If there is more than one acceptable option for a field, the valid options are shown in curly braces: FOOBAR {<string>|<expr>} In this example, you must provide either a <string> or an <expr> with the FOOBAR command or statement. Typefaces THIS TYPEFACE IS USED TO SHOW USER INPUT THIS TYPEFACE IS USED TO SHOW OUTPUT Keyboard Input Pressing the ENTER or RETURN key is shown as: Pressing the Backspace or Delete key is shown as: ← Holding down the Control key while pressing a key is shown as: ctrl-S -

Open PDF in New Window

BEST AVAILABLE COPY i The pur'pose of this DIGITAL COMPUTER Itop*"°a""-'"""neesietter' YNEWSLETTER . W OFFICf OF NIVAM RUSEARCMI • MATNEMWTICAL SCIENCES DIVISION Vol. 9, No. 2 Editors: Gordon D. Goldstein April 1957 Albrecht J. Neumann TABLE OF CONTENTS It o Page No. W- COMPUTERS. U. S. A. "1.Air Force Armament Center, ARDC, Eglin AFB, Florida 1 2. Air Force Cambridge Research Center, Bedford, Mass. 1 3. Autonetics, RECOMP, Downey, Calif. 2 4. Corps of Engineers, U. S. Army 2 5. IBM 709. New York, New York 3 6. Lincoln Laboratory TX-2, M.I.T., Lexington, Mass. 4 7. Litton Industries 20 and 40 DDA, Beverly Hills, Calif. 5 8. Naval Air Test Centcr, Naval Air Station, Patuxent River, Maryland 5 9. National Cash Register Co. NC 304, Dayton, Ohio 6 10. Naval Air Missile Test Center, RAYDAC, Point Mugu, Calif. 7 11. New York Naval Shipyard, Brooklyn, New York 7 12. Philco, TRANSAC. Philadelphia, Penna. 7 13. Western Reserve Univ., Cleveland, Ohio 8 COMPUTING CENTERS I. Univ. of California, Radiation Lab., Livermore, Calif. 9 2. Univ. of California, SWAC, Los Angeles, Calif. 10 3. Electronic Associates, Inc., Princeton Computation Center, Princeton, New Jersey 10 4. Franklin Institute Laboratories, Computing Center, Philadelphia, Penna. 11 5. George Washington Univ., Logistics Research Project, Washington, D. C. 11 6. M.I.T., WHIRLWIND I, Cambridge, Mass. 12 7. National Bureau of Standards, Applied Mathematics Div., Washington, D.C. 12 8. Naval Proving Ground, Naval Ordnance Computation Center, Dahlgren, Virgin-.a 12 9. Ramo Wooldridge Corp., Digital Computing Center, Los Angeles, Calif. -

TCD-SCSS-T.20121208.032.Pdf

AccessionIndex: TCD-SCSS-T.20121208.032 Accession Date: 8-Dec-2012 Accession By: Prof.J.G.Byrne Object name: Burroughs 1714 Vintage: c.1972 Synopsis: Commercial zero-instruction-set computer used by the Dept.Computer Science from 1973-1979. Just two prototyping boards survive. Description: The Burroughs 1714 was one of their B1700 family, introduced in 1972 to compete with IBM's System/3. The original research for the B1700 series, initially codenamed the Proper Language Processor or Program Language Processor (PLP) was done at the Burroughs Pasadena plant. The family were known as the Burroughs Small Systems, as distinct from the Burroughs Medium Systems (B2000, etc) and the Burroughs Large Systems (B5000, etc). All the Burroughs machines had high-level language architectures. The large were ALGOL machines, the medium COBOL machines, but the small were universal machines. The principal designer of the B1700 family was Wayne T. Wilner. He designed the architecture as a zero-instruction-set computer, an attempt to bridge the inefficient semantic gap between the ideal solution to a particular programming problem and the real physical hardware. The B1700 architecture executed idealized virtual machines for any language from virtual memory. It achieved this feat by microprogramming, see the microinstruction set further below. The Burroughs MCP (Master Control Program) would schedule a particular job to run, then preload the interpreter for whatever language was required into a writeable control store, allowing the machine to emulate the desired virtual machine. The hardware was optimised for this. It had bit-addressable memory, a variable-width ALU, could OR in data from a register into the instruction register (for very efficient instruction parsing), and the output of the ALU was directly addressable as X+Y or X-Y read-only registers. -

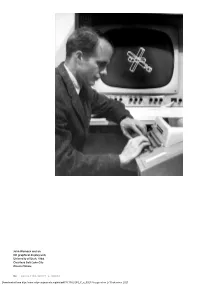

Hereby the Screen Stands in For, and Thereby Occludes, the Deeper Workings of the Computer Itself

John Warnock and an IDI graphical display unit, University of Utah, 1968. Courtesy Salt Lake City Deseret News . 24 doi:10.1162/GREY_a_00233 Downloaded from http://www.mitpressjournals.org/doi/pdf/10.1162/GREY_a_00233 by guest on 27 September 2021 The Random-Access Image: Memory and the History of the Computer Screen JACOB GABOURY A memory is a means for displacing in time various events which depend upon the same information. —J. Presper Eckert Jr. 1 When we speak of graphics, we think of images. Be it the windowed interface of a personal computer, the tactile swipe of icons across a mobile device, or the surreal effects of computer-enhanced film and video games—all are graphics. Understandably, then, computer graphics are most often understood as the images displayed on a computer screen. This pairing of the image and the screen is so natural that we rarely theorize the screen as a medium itself, one with a heterogeneous history that develops in parallel with other visual and computa - tional forms. 2 What then, of the screen? To be sure, the computer screen follows in the tradition of the visual frame that delimits, contains, and produces the image. 3 It is also the skin of the interface that allows us to engage with, augment, and relate to technical things. 4 But the computer screen was also a cathode ray tube (CRT) phosphorescing in response to an electron beam, modified by a grid of randomly accessible memory that stores, maps, and transforms thousands of bits in real time. The screen is not simply an enduring technique or evocative metaphor; it is a hardware object whose transformations have shaped the ma - terial conditions of our visual culture. -

BCIS 1305 Business Computer Applications

BCIS 1305 Business Computer Applications BCIS 1305 Business Computer Applications San Jacinto College This course was developed from generally available open educational resources (OER) in use at multiple institutions, drawing mostly from a primary work curated by the Extended Learning Institute (ELI) at Northern Virginia Community College (NOVA), but also including additional open works from various sources as noted in attributions on each page of materials. Cover Image: “Keyboard” by John Ward from https://flic.kr/p/tFuRZ licensed under a Creative Commons Attribution License. BCIS 1305 Business Computer Applications by Extended Learning Institute (ELI) at NOVA is licensed under a Creative Commons Attribution 4.0 International License, except where otherwise noted. CONTENTS Module 1: Introduction to Computers ..........................................................................................1 • Reading: File systems ....................................................................................................................................... 1 • Reading: Basic Computer Skills ........................................................................................................................ 1 • Reading: Computer Concepts ........................................................................................................................... 1 • Tutorials: Computer Basics................................................................................................................................ 1 Module 2: Computer -

Introduction to Computer Data Representation

Introduction to Computer Data Representation Peter Fenwick The University of Auckland (Retired) New Zealand Bentham Science Publishers Bentham Science Publishers Bentham Science Publishers Executive Suite Y - 2 P.O. Box 446 P.O. Box 294 PO Box 7917, Saif Zone Oak Park, IL 60301-0446 1400 AG Bussum Sharjah, U.A.E. USA THE NETHERLANDS [email protected] [email protected] [email protected] Please read this license agreement carefully before using this eBook. Your use of this eBook/chapter constitutes your agreement to the terms and conditions set forth in this License Agreement. This work is protected under copyright by Bentham Science Publishers to grant the user of this eBook/chapter, a non- exclusive, nontransferable license to download and use this eBook/chapter under the following terms and conditions: 1. This eBook/chapter may be downloaded and used by one user on one computer. The user may make one back-up copy of this publication to avoid losing it. The user may not give copies of this publication to others, or make it available for others to copy or download. For a multi-user license contact [email protected] 2. All rights reserved: All content in this publication is copyrighted and Bentham Science Publishers own the copyright. You may not copy, reproduce, modify, remove, delete, augment, add to, publish, transmit, sell, resell, create derivative works from, or in any way exploit any of this publication’s content, in any form by any means, in whole or in part, without the prior written permission from Bentham Science Publishers. 3. The user may print one or more copies/pages of this eBook/chapter for their personal use. -

The An/Fsq-7

291961 RJ3117 (38413) 4/10/81 Computer Science Research Report HISTORY OF THE DESIGN OF THE SAGE COMPUTER - THE AN/FSQ-7 Morton M. Astrahan IBM Research Laboratory San Jose, California 95193 Jonn T. Jacobs MITRE Corporation Bedford, Massachusetts 01/30 LIMITED DISTRIBUTION NOTICE Tns r uort has been submitted for publication outside of IBM and will orobably be cooyrightea if accected for publication. It 3i been -ssued as a Researcn Reoort for early dissemination of :s contents. In view of tde transfer of coovr gnt to the outside iblisner. ts distribution outside of iBM onor to publication ^ncyld be limited ?o oeer communications ana specific r-jauests. After outside oublicouon. reauests sbouid Do *illed only by reonnts or legally obtained cooies of the artic> ie q.. payment of royalties) Research Division Yorktown Heights, New York • S3n Jose. California * Zurich, Switzerland Copies may be requested from IBM Thomas J. Watson Research Center Distribution Services Post Office Box 21 8 Yorktown Heights. New York 10598 RJ3117 (33413) 4/10/81 Computer Science History of the Design of the SAGE Computer- the AN/FSQ-7 Morton M. Astrahan John F. Jacobs IBM Research Laboratory MITRE Corp. San Jose, California 95193 Bedford, Massachusetts 01730 ABSTRACT: This is the story of the development of the SAGE (Semi-Aucomatic Ground Environment) Air Defense Computer, the AN/FSQ-7. At the time of its operational deployment beginning in 1958, the AN/FSQ-7 was the first large-scale, real-time digital control computer supporting a major mili tary mission. The AN/FSQ-7 design, including its architecture, components and computer programs, drew on RSD programs throughout the United States, but it drew mostly on work being done at MIT Project Whirlwind and at IBM. -

Metadefender Core V4.17.3

MetaDefender Core v4.17.3 © 2020 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of MetaDefender Core 14 1. Quick Start with MetaDefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Process Files with MetaDefender Core 21 2. Installing or Upgrading MetaDefender Core 22 2.1. Recommended System Configuration 22 Microsoft Windows Deployments 22 Unix Based Deployments 24 Data Retention 26 Custom Engines 27 Browser Requirements for the Metadefender Core Management Console 27 2.2. Installing MetaDefender 27 Installation 27 Installation notes 27 2.2.1. Installing Metadefender Core using command line 28 2.2.2. Installing Metadefender Core using the Install Wizard 31 2.3. Upgrading MetaDefender Core 31 Upgrading from MetaDefender Core 3.x 31 Upgrading from MetaDefender Core 4.x 31 2.4. MetaDefender Core Licensing 32 2.4.1. Activating Metadefender Licenses 32 2.4.2. Checking Your Metadefender Core License 37 2.5. Performance and Load Estimation 38 What to know before reading the results: Some factors that affect performance 38 How test results are calculated 39 Test Reports 39 Performance Report - Multi-Scanning On Linux 39 Performance Report - Multi-Scanning On Windows 43 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. -

Guide to the Collection of Massachusetts Institute of Technology Computing Projects Subject Collection

Guide to the Collection of Massachusetts Institute of Technology Computing Projects Subject Collection Dates: 1947-1994, bulk 1950-1975 Extent: 9 linear feet in 8 boxes Collection number: X3495.2006 Accession number: 102634702 Processed by: Paula Little, March 2006 MIT Computing Projects Subject Collection X3495.2006 Abstract The Collection of Massachusetts Institute of Technology (MIT) Computing Projects is comprised of technical notes, reports, correspondence and miscellaneous documentation relating to the development of the Whirlwind, TX-0 and T-X2 computers as well as Project MAC (Multiple-Access Computer) at MIT. Included as well are a number of other technical reports relating to computing projects at MIT. The documents span 1947 to 1994. Administrative Information Access Restrictions The collection is open for research. Publication Rights The Computer History Museum (CHM) can only claim physical ownership of the collection. Users are responsible for satisfying any claims of the copyright holder. Permission to copy or publish any portion of the Computer History Museum’s collection must be given by the Computer History Museum. Preferred Citation [Identification of Item], [Item Date], MIT Computing Projects Subject Collection, Lot X3495.2006, Box [#], Folder [#], Computer History Museum. Provenance The provenance is unknown for the MIT Computing Projects Subject Collection. The Collection was originally acquired from a variety of sources in the 1980s and 1990s when the Computer History Museum, then known as The Computer Museum, was located in Boston. At that time, all documents were arranged alphabetically by originating institution or company. Many of the Whirlwind documents most likely were donated to the Museum in 1982 as part of lot X115.82. -

Creative Computing Magazine Is Published Bi-Monthly by Creative Computing

he #1 magazine of computer applicafa *'are raHSJS? sfife a*«uiH O K» » #-. ^ *&> iiD o «» •— "^ Ul JT © O O Ul oo >- at O- X * 3 •O »- •« ^» ^ *© c * c ir — _j «_> o t^ ^ o am z 6 %' 7 * » • • Consumer Computers Buying Guide a/ Paf/i Analysis Electronic Game Reviews Mail Label Programs Someday all terminals will be smart. 128 Functions-software controlled 82 x 16 or 92 x 22 format-plus graphics 7x12 matrix, upper/lower case letters Printer output port 50 to 38,400 baud-selectable "CHERRY" keyboard CT-82 Intelligent Terminal, assembled and tested $795.00 ppd in Cont. U.S. SOUTHWEST TECHNICAL PRODUCTS CORPORATION 219 W. RHAPSODY SAN ANTONIO, TEXAS 78216 CIRCLE 106 ON READER 3ERVICE CARD Give creative Gontpattng to a fHend for " [W*nr fiwter service - call tell free X * • -540-0445] 800-631-8112 InNJ 201 TYPE OF SUBSCRIPTION BOOKS AND MERCHANDISE Foreign Foreign Term USA Surface Air D Gift Send to me 1 2 issues D $ 15 $ 23 $ 39 24 issues D 28 44 76 Gifts cannot be gift wrapped but a 36 issues D 40 64 112 Lifetime D 300 400 600 card with your name will be sent with each order YOUR NAME AND ADDRESS : Quan Cat Descriptions Price Name Address Cittj State Zip- NAME TO APPEAR ON GIFT CARD* SEND GIFT SUBSCRIPTION TO- Name Address Citvf State. .Zip. PAYMENT INFORMATION a Cash , check or 7M.O. enclosed o Visa/BankAmericard") Card no. Books shipping charge SI 00 USA S2 00 Foreign a Master Charge J Exp. NJ Residents add 5% sales lax DPlease bill me ($100 billing fee will be added) be prepaid- TOTAL (magazines and books) Book, orders from individuals must creative computing creative computing Books.