New IBM Intellistation Z Pro Models Feature Intel Itanium Processor and Microsoft Windows XP 64-Bit Edition

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Microcode Revision Guidance August 31, 2019 MCU Recommendations

microcode revision guidance August 31, 2019 MCU Recommendations Section 1 – Planned microcode updates • Provides details on Intel microcode updates currently planned or available and corresponding to Intel-SA-00233 published June 18, 2019. • Changes from prior revision(s) will be highlighted in yellow. Section 2 – No planned microcode updates • Products for which Intel does not plan to release microcode updates. This includes products previously identified as such. LEGEND: Production Status: • Planned – Intel is planning on releasing a MCU at a future date. • Beta – Intel has released this production signed MCU under NDA for all customers to validate. • Production – Intel has completed all validation and is authorizing customers to use this MCU in a production environment. -

The Professional Workstation

The Professional Workstation. The New Seat of Power For those who see the future and give IntelliStation is accredited by the source SDRAM, you’ll get the detailed view with shape to it today…for those who create, you most trust: the companies that true-color 1280x1024 resolution, 24- or reveal and explore…for those in hot provide the software you rely on every 32-bit Z-buffering for precision object pursuit of excellence—take your place at working day. See our Web site for the ordering, Gouraud shading, trilinear the new IBM IntelliStation M Pro. current list of supported applications: texture mapping and support for both www.ibm.com/pc/us/intellistation OpenGL and Heidi. The available This new-generation professional NT Intergraph geometry and lighting workstation from IBM responds with accelerator—supercharged with 14 digital startling speed. Advanced Intel® Pentium® Application-focused graphics signal processors (DSPs)—makes the II processors race at up to 400MHz1 in IBM knows—as you do—that graphics IntelliStation the ultimate 3D environment single or dual SMP configurations, response is a defining criteria for on Windows NT. The IBM IntelliStation’s ramcharged by the 100MHz system bus workstation performance. IntelliStation real-time graphics eliminate the wait and and 512KB of L2 cache. Choose from professional workstations deliver, with a let you create. accelerated 2D/3D graphics solutions. choice of dimensions. For 2D display, the Matrox Millennium II graphics card is the front runner, combining expansive Your competitive edge— Application-focused performance resolutions with high refresh rates for IBM SystemXtra Choosing a Windows® NT® workstation brilliant, flicker-free images. -

IBM Intellistation Z Pro

Extreme performance for peak productivity IBM IntelliStation Z Pro Achieve escape velocity Highlights Boost your workstation expectations into the high-performance orbit of the NEW! Up to 550MHz Intel® Pentium® III Application performance IntelliStation Z Pro. The Z Pro is the ulti- Xeon™ processors IBM has teamed with leading software mate expression of the IBM IntelliStation Ultimate multiprocessing punch at up to vendors to ensure the IntelliStation’s design mandate—to deliver superior 2X 550MHz1 with new dynamic media superior application-focused perfor- Windows NT ® application performance instructions and enhanced floating point mance and compatibility with their with inclusive compatibility—through performance. The IntelliStation™ Z Pro is specialized software in the fields of extreme power and scalability. Clearly, ramcharged with Intel’s 440GX AGPset engineering, electronic design, digital the Z Pro’s technical merits distinguish with full-speed L2 cache, 100MHz sys- content creation, finance, GIS and soft- this premiere workstation. From its tem bus, and support for up to 2GB of ware development. award-winning performance to its cost- 100MHz ECC SDRAM for exemplary saving manageability to the thoughtful application performance and reliability. Universal Manageability details, like tool-free access for upgrades. Save time, money and manpower with But the most compelling advantages— NEW!2D/3D graphics: visual acuity IBM’s Universal Management Agent™ IBM’s meticulous design standard that Choose from leading 2D and 3D graph- (UMA), client software that helps deploy, defies downtime, renowned global sup- ics engines tailored to your tasks. The maintain and protect your systems and port and SystemXtra™ services from industry’s first 256-bit 3D graphics en- valuable data. -

New IBM Intellistation M Pro Models Feature Intel Xeon Processors at 2.8 Ghz

Hardware Announcement September 10, 2002 New IBM IntelliStation M Pro Models Feature Intel Xeon Processors at 2.8 GHz 1 MHz and GHz only measures Overview microprocessor internal clock speed, At a Glance New models of the not application performance. Many factors affect application IntelliStation M Pro workstation performance. New IntelliStation M Pro systems deliver superb graphics and 2 Variable read rate. Actual playback deliver superb technology, high-performance precision to help speed will vary and is often less than high-performance graphics, and you reduce project turnaround times the maximum possible. outstanding service and support. in business, media creation, 3 For copies of the IBM Statement of • 1 engineering, and scientific Limited Warranty, contact your Intel Xeon at 2.8 GHz , single or reseller or calling IBM. In the United dual processor applications. States and Canada, call 800-IBM-SERV (426-7378). Telephone • Graphics: Solid Performance support may be subject to additional − Matrox Millenium G450 DVI • charges. SMP-capable Intel Xeon 4 You may be asked certain diagnostic or NVIDIA Quadro4 200NVS microprocessor at 2.8 GHz with questions before a technician is sent. for performance 2D streaming SIMD extensions, Intel 5 Memory in all models is PC800 ECC 860 core-chipset, and 512 KB L2 RDRAM RIMMs. − ATI Fire GL 8800 for cache 6 GB equals 1,000,000,000 bytes when advanced 3D or NVIDIA referring to HDD capacity; accessible Quadro4 900XGL or 3Dlabs • 5 PC800 ECC Rambus memory capacity may be less. Wildcat III 6110 for extreme • 3D Choice of HDD: Planned Availability Date • − 18.2 GB6 10,000 rpm Ultra160 HDD: September 13, 2002 S.M.A.R.T. -

The Central Processor Unit

Systems Architecture The Central Processing Unit The Central Processing Unit – p. 1/11 The Computer System Application High-level Language Operating System Assembly Language Machine level Microprogram Digital logic Hardware / Software Interface The Central Processing Unit – p. 2/11 CPU Structure External Memory MAR: Memory MBR: Memory Address Register Buffer Register Address Incrementer R15 / PC R11 R7 R3 R14 / LR R10 R6 R2 R13 / SP R9 R5 R1 R12 R8 R4 R0 User Registers Booth’s Multiplier Barrel IR Shifter Control Unit CPSR 32-Bit ALU The Central Processing Unit – p. 3/11 CPU Registers Internal Registers Condition Flags PC Program Counter C Carry IR Instruction Register Z Zero MAR Memory Address Register N Negative MBR Memory Buffer Register V Overflow CPSR Current Processor Status Register Internal Devices User Registers ALU Arithmetic Logic Unit Rn Register n CU Control Unit n = 0 . 15 M Memory Store SP Stack Pointer MMU Mem Management Unit LR Link Register Note that each CPU has a different set of User Registers The Central Processing Unit – p. 4/11 Current Process Status Register • Holds a number of status flags: N True if result of last operation is Negative Z True if result of last operation was Zero or equal C True if an unsigned borrow (Carry over) occurred Value of last bit shifted V True if a signed borrow (oVerflow) occurred • Current execution mode: User Normal “user” program execution mode System Privileged operating system tasks Some operations can only be preformed in a System mode The Central Processing Unit – p. 5/11 Register Transfer Language NAME Value of register or unit ← Transfer of data MAR ← PC x: Guard, only if x true hcci: MAR ← PC (field) Specific field of unit ALU(C) ← 1 (name), bit (n) or range (n:m) R0 ← MBR(0:7) Rn User Register n R0 ← MBR num Decimal number R0 ← 128 2_num Binary number R1 ← 2_0100 0001 0xnum Hexadecimal number R2 ← 0x40 M(addr) Memory Access (addr) MBR ← M(MAR) IR(field) Specified field of IR CU ← IR(op-code) ALU(field) Specified field of the ALU(C) ← 1 Arithmetic and Logic Unit The Central Processing Unit – p. -

Pep8cpu: a Programmable Simulator for a Central Processing Unit J

Pep8CPU: A Programmable Simulator for a Central Processing Unit J. Stanley Warford Ryan Okelberry Pepperdine University Novell 24255 Pacific Coast Highway 1800 South Novell Place Malibu, CA 90265 Provo, UT 84606 [email protected] [email protected] ABSTRACT baum [5]: application, high-order language, assembly, operating This paper presents a software simulator for a central processing system, instruction set architecture (ISA), microcode, and logic unit. The simulator features two modes of operation. In the first gate. mode, students enter individual control signals for the multiplex- For a number of years we have used an assembler/simulator for ers, function controls for the ALU, memory read/write controls, Pep/8 in the Computer Systems course to give students a hands-on register addresses, and clock pulses for the registers required for a experience at the high-order language, assembly, and ISA levels. single CPU cycle via a graphical user interface. In the second This paper presents a software package developed by an under- mode, students write a control sequence in a text window for the graduate student, now a software engineer at Novell, who took the cycles necessary to implement a single instruction set architecture Computer Organization course and was motivated to develop a (ISA) instruction. The simulator parses the sequence and allows programmable simulator at the microcode level. students to single step through its execution showing the color- Yurcik gives a survey of machine simulators [8] and maintains a coded data flow through the CPU. The paper concludes with a Web site titled Computer Architecture Simulators [9] with links to description of the use of the software in the Computer Organiza- papers and internet sources for machine simulators. -

Reverse Engineering X86 Processor Microcode

Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz, Ruhr-University Bochum https://www.usenix.org/conference/usenixsecurity17/technical-sessions/presentation/koppe This paper is included in the Proceedings of the 26th USENIX Security Symposium August 16–18, 2017 • Vancouver, BC, Canada ISBN 978-1-931971-40-9 Open access to the Proceedings of the 26th USENIX Security Symposium is sponsored by USENIX Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz Ruhr-Universitat¨ Bochum Abstract hardware modifications [48]. Dedicated hardware units to counter bugs are imperfect [36, 49] and involve non- Microcode is an abstraction layer on top of the phys- negligible hardware costs [8]. The infamous Pentium fdiv ical components of a CPU and present in most general- bug [62] illustrated a clear economic need for field up- purpose CPUs today. In addition to facilitate complex and dates after deployment in order to turn off defective parts vast instruction sets, it also provides an update mechanism and patch erroneous behavior. Note that the implementa- that allows CPUs to be patched in-place without requiring tion of a modern processor involves millions of lines of any special hardware. While it is well-known that CPUs HDL code [55] and verification of functional correctness are regularly updated with this mechanism, very little is for such processors is still an unsolved problem [4, 29]. known about its inner workings given that microcode and the update mechanism are proprietary and have not been Since the 1970s, x86 processor manufacturers have throughly analyzed yet. -

New IBM Intellistation a Pro Models Introduce New Graphics and New AMD Opteron Processors

Hardware Announcement April 4, 2006 New IBM IntelliStation A Pro models introduce new graphics and new AMD Opteron processors • Choice of S.M.A.R.T. HDDs: Overview At a glance − 73.4 GB5 Ultra320 SCSI at Position yourself for the future of 10,000 rpm 64-bit computing with the The new highly scalable − 160 GB SATA at 7,200 rpm IntelliStation A Pro workstation. IntelliStation A Pro models deliver This workstation features AMD • 530-watt, auto ranging power price-to-performance ratio with the Opteron processors and PCI Express supply latest technologies, graphics and x16 graphics that enable outstanding service and support. simultaneous 32- and 64-bit Compelling graphics • — computing to help optimize AMD Opteron processors performance. The AMD Opteron Your choice of dual-head capable PCI Single or SMP-capable Model processor helps protect your Express graphics: 254 or dual-core Model 285 • Up to 16 GB1 of ECC DDR investment in your current 32-bit • NVIDIA Quadro NVS 285 applications while preparing to SDRAM RDIMM addressable • NVIDIA Quadro FX 1400 memory2 migrate to 64-bit applications when • NVIDIA Quadro FX 3500 • you are ready. PCI Express x16 graphics: • NVIDIA Quadro FX 4500 − NVIDIA Quadro NVS 285 for performance 2D Take advantage of the multitasking, Outstanding support multithreaded application power of − NVIDIA Quadro FX 1400 for the latest IntelliStation A Pro models. The highly reliable IntelliStation A advanced 3D New technologies, including PCI Pro systems feature a three-year − NVIDIA Quadro FX 3500 for Express graphics and dual-core limited warranty on parts and labor. high-advanced 3D processors, contribute to an In the United States and Canada, call − NVIDIA Quadro FX 4500 for outstanding system design to help IBM at 800-IBM-SERV (426-7378). -

Introduction to Microcoded Implementation of a CPU Architecture

Introduction to Microcoded Implementation of a CPU Architecture N.S. Matloff, revised by D. Franklin January 30, 1999, revised March 2004 1 Microcoding Throughout the years, Microcoding has changed dramatically. The debate over simple computers vs complex computers once raged within the architecture community. In the end, the most popular microcoded computers survived for three reasons - marketshare, technological improvements, and the embracing of the principles used in simple computers. So the two eventually merged into one. To truly understand microcoding, one must understand why they were built, what they are, why they survived, and, finally, what they look like today. 1.1 Motivation Strictly speaking, the term architecture for a CPU refers only to \what the assembly language programmer" sees|the instruction set, addressing modes, and register set. For a given target architecture, i.e. the architecture we wish to build, various implementations are possible. We could have many different internal designs of the CPU chip, all of which produced the same effect, namely the same instruction set, addressing modes, etc. The different internal designs could then all be produced for the different models of that CPU, as in the familiar Intel case. The different models would have different speed capabilities, and probably different prices to the consumer. But the same machine languge program, say a .EXE file in the Intel/DOS case, would run on any CPU in the family. When desigining an instruction set architecture, there is a tradeoff between software and hardware. If you provide very few instructions, it takes more instructions to perform the same task, but the hardware can be very simple. -

Intellistation Z Pro Type 6223: User™S Guide

IntelliStation Z Pro Ty pe 6223 User’s Guide IntelliStation Z Pro Ty pe 6223 User’s Guide Note: Before using this information and the product it supports, read the information in Appendix B, “Notices,” on page 105 and the warranty information in the Installation Guide. First Edition (September 2004) © Copyright International Business Machines Corporation 2004. All rights reserved. US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents Safety . vii Chapter 1. Introducing the IntelliStation Z Pro computer. .1 Related documentation . .1 Notices and statements used in this document. .2 Features and specifications . .3 What your computer offers . .4 Software. .4 Preinstalled software . .5 Software on CD . .6 Software available on the World Wide Web . .6 Reliability, availability, and serviceability features . .7 Chapter 2. Operating the computer . .9 Controls, LEDs, and connectors . .9 Turning on the computer . .10 Using preinstalled software . .11 Running the operating-system setup program . .12 Installing other operating systems . .12 Viewing the license agreement . .13 Registering your computer. .13 Creating an emergency recovery-repair diskette in Windows . .13 Creating an IBM Enhanced Diagnostics diskette in Windows . .14 Using video features . .15 Video device drivers . .15 Changing monitor settings . .15 Using audio features . .16 Using security features . .16 Anti-intrusion features . .17 Component protection . .17 Data protection . .17 Locking the keyboard . .17 Updating system programs . .18 Managing your computer . .18 Shutting down the operating system . .19 Turning off the computer . .19 Chapter 3. Configuring the computer . .21 Using the Configuration/Setup Utility program . .22 Starting the Configuration/Setup Utility program . -

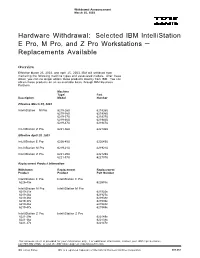

Hardware Withdrawal: Selected IBM Intellistation E Pro, M Pro, and Z Pro Workstations — Replacements Available

Withdrawal Announcement March 25, 2003 Hardware Withdrawal: Selected IBM IntelliStation E Pro, M Pro, and Z Pro Workstations — Replacements Available Overview Effective March 25, 2003, and April 25, 2003, IBM will withdraw from marketing the following machine types and associated models. After these dates, you can no longer obtain these products directly from IBM. You can obtain these products on an as-available basis through IBM Business Partners. Machine Type/ Part Description Model Number Effective March 25, 2003 IntelliStation M Pro 6219-26U 621926U 6219-36U 621936U 6219-37U 621937U 6219-46U 621946U 6219-47U 621947U IntelliStation Z Pro 6221-36U 622136U Effective April 25, 2003 IntelliStation E Pro 6226-45U 622645U IntelliStation M Pro 6219-21U 621921U IntelliStation Z Pro 6221-29U 622129U 6221-37U 622137U Replacement Product Information Withdrawn Replacement Replacement Product Product Part Number IntelliStation E Pro IntelliStation E Pro 6226-45x 622655x IntelliStation M Pro IntelliStation M Pro 6219-21x 621922x 6219-26x 621927x 6219-36x 621938x 6219-37x 621939x 6219-46x 621948x 6219-47x 621949x IntelliStation Z Pro IntelliStation Z Pro 6221-29x 622149x 6221-36x 622138x 6221-37x 622147x This announcement is provided for your information only. For additional information, contact your IBM representative, call 800-IBM-4YOU, or visit the IBM home page at: http://www.ibm.com. IBM United States IBM is a registered trademark of International Business Machines Corporation. 903-057 Reference Information For additional information on the -

ECE 4750 Computer Architecture Topic 1: Microcoding

ECE 4750 Computer Architecture Topic 1: Microcoding Christopher Batten School of Electrical and Computer Engineering Cornell University http://www.csl.cornell.edu/courses/ece4750 slide revision: 2013-09-01-10-42 Instruction Set Architecture Microcoded MIPS Processor Microcoding Discussion & Trends Agenda Instruction Set Architecture IBM 360 Instruction Set MIPS Instruction Set ISA to Microarchitecture Mapping Microcoded MIPS Processor Microcoded MIPS Microarchitecture #1 Microcoded MIPS Microarchitecture #2 Microcoding Discussion and Trends ECE 4750 T01: Microcoding 2 / 45 • Instruction Set Architecture • Microcoded MIPS Processor Microcoding Discussion & Trends Instruction Set Architecture I Contract between software & hardware Application Algorithm I Typically specified as all of the Programming Language programmer-visible state (registers & Operating System memory) plus the semantics of instructions Instruction Set Architecture Microarchitecture that operate on this state Register-Transfer Level IBM 360 was first line of machines to Gate Level I Circuits separate ISA from microarchitecture and Devices implementation Physics ... the structure of a computer that a machine language programmer must understand to write a correct (timing independent) program for that machine. — Amdahl, Blaauw, Brooks, 1964 ECE 4750 T01: Microcoding 3 / 45 • Instruction Set Architecture • Microcoded MIPS Processor Microcoding Discussion & Trends Compatibility Problem at IBM I By early 1960’s, IBM had several incompatible lines of computers! . Defense : 701 . Scientific : 704, 709, 7090, 7094 . Business : 702, 705, 7080 . Mid-Sized Business : 1400 . Decimal Architectures : 7070, 7072, 7074 I Each system had its own: . Instruction set . I/O system and secondary storage (tapes, drums, disks) . Assemblers, compilers, libraries, etc . Market niche ECE 4750 T01: Microcoding 4 / 45 • Instruction Set Architecture • Microcoded MIPS Processor Microcoding Discussion & Trends IBM 360: A General-Purpose Register Machine I Processor State .