Common Base (CB) Amplifier • the Base Terminal Is Biased at a Fixed Voltage; the Input Signal Is Applied to the Emitter, and the Output Signal Sensed at the Collector

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Cascode Amplifiers by Dennis L. Feucht Two-transistor combinations, such as the Darlington configuration, provide advantages over single-transistor amplifier stages. Another two-transistor combination in the analog designer's circuit library combines a common-emitter (CE) input configuration with a common-base (CB) output. This article presents the design equations for the basic cascode amplifier and then offers other useful variations. (FETs instead of BJTs can also be used to form cascode amplifiers.) Together, the two transistors overcome some of the performance limitations of either the CE or CB configurations. Basic Cascode Stage The basic cascode amplifier consists of an input common-emitter (CE) configuration driving an output common-base (CB), as shown above. The voltage gain is, by the transresistance method, the ratio of the resistance across which the output voltage is developed by the common input-output loop current over the resistance across which the input voltage generates that current, modified by the α current losses in the transistors: v R A = out = −α ⋅α ⋅ L v 1 2 β + + + vin RB /( 1 1) re1 RE where re1 is Q1 dynamic emitter resistance. This gain is identical for a CE amplifier except for the additional α2 loss of Q2. The advantage of the cascode is that when the output resistance, ro, of Q2 is included, the CB incremental output resistance is higher than for the CE. For a bipolar junction transistor (BJT), this may be insignificant at low frequencies. The CB isolates the collector-base capacitance, Cbc (or Cµ of the hybrid-π BJT model), from the input by returning it to a dynamic ground at VB. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

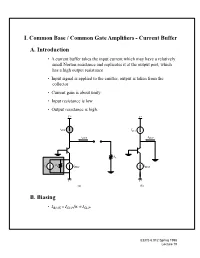

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

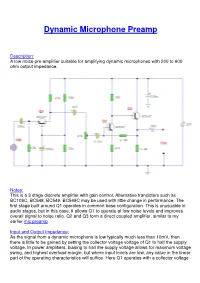

Dynamic Microphone Amplifier

Dynamic Microphone Preamp Description: A low noise pre-amplifier suitable for amplifying dynamic microphones with 200 to 600 ohm output impedance. Notes: This is a 3 stage discrete amplifier with gain control. Alternative transistors such as BC109C, BC548, BC549, BC549C may be used with little change in performance. The first stage built around Q1 operates in common base configuration. This is unusuable in audio stages, but in this case, it allows Q1 to operate at low noise levels and improves overall signal to noise ratio. Q2 and Q3 form a direct coupled amplifier, similar to my earlier mic preamp . Input and Output Impedance: As the signal from a dynamic microphone is low typically much less than 10mV, then there is little to be gained by setting the collector voltage voltage of Q1 to half the supply voltage. In power amplifiers, biasing to half the supply voltage allows for maximum voltage swing, and highest overload margin, but where input levels are low, any value in the linear part of the operating characteristics will suffice. Here Q1 operates with a collector voltage of 2.4V and a low collector current of around 200uA. This low collector current ensures low noise performance and also raises the input impedance of the stage to around 400 ohms. This is a good match for any dynamic microphone having an impedances between 200 and 600 ohms. The output impedance at Q3 is low, the graph of input and output impedance versus frequency is shown below: Gain and Frequency Response: The overall gain of this pre-amplifier is around +39dB or about 90 times. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

Lecture23-Amplifier Frequency Response.Pptx

EE105 – Fall 2014 Microelectronic Devices and Circuits Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) Lecture23-Amplifier Frequency Response 1 Common-Emitter Amplifier – ωH Open-Circuit Time Constant (OCTC) Method At high frequencies, impedances of coupling and bypass capacitors are small enough to be considered short circuits. Open-circuit time constants associated with impedances of device capacitances are considered instead. 1 ωH ≅ m ∑RioCi i=1 where Rio is resistance at terminals of ith capacitor C with all other v ! R $ i R = x = r #1+ g R + L & capacitors open-circuited. µ 0 π 0 m L ix " rπ 0 % For a C-E amplifier, assuming C = 0 L 1 1 ωH ≅ = Rπ 0 = rπ 0 Rπ 0Cπ + Rµ 0Cµ rπ 0CT Lecture23-Amplifier Frequency Response 2 1 Common-Emitter Amplifier High Frequency Response - Miller Effect • First, find the simplified small -signal model of the C-E amp. • Replace coupling and bypass capacitors with short circuits • Insert the high frequency small -signal model for the transistor ! # rπ 0 = rπ "rx +(RB RI )$ Lecture23-Amplifier Frequency Response 3 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) v R r Input gain is found as A = b = in ⋅ π i v R R r r i I + in x + π R || R || (r + r ) r = 1 2 x π ⋅ π RI + R1 || R2 || (rx + rπ ) rx + rπ Terminal gain is vc Abc = = −gm (ro || RC || R3 ) ≅ −gm RL vb Using the Miller effect, we find CeqB = Cµ (1− Abc )+Cπ (1− Abe ) the equivalent capacitance at the base as: = Cµ (1−[−gm RL ])+Cπ (1− 0) = Cµ (1+ gm RL )+Cπ Chap 17-4 Lecture23-Amplifier Frequency Response 4 2 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) ! # • The total equivalent resistance ReqB = rπ 0 = rπ "rx +(RB RI )$ at the base is • The total capacitance and CeqC = Cµ +CL resistance at the collector are ReqC = ro RC R3 = RL • Because of interaction through 1 ω = Cµ, the two RC time constants p1 ! # rπ 0 "Cπ +Cµ (1+ gm RL )$+ RL (Cµ +CL ) interact, giving rise to a dominant pole. -

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Transistor Current Source

PY 452 Advanced Physics Laboratory Hans Hallen Electronics Labs One electronics project should be completed. If you do not know what an op-amp is, do either lab 2 or lab 3. A written report is due, and should include a discussion of the circuit with inserted equations and plots as appropriate to substantiate the words and show that the measurements were taken. The report should not consist of the numbered items below and short answers, but should be one coherent discussion that addresses most of the issues brought out in the numbered items below. This is not an electronics course. Familiarity with electronics concepts such as input and output impedance, noise sources and where they matter, etc. are important in the lab AND SHOULD APPEAR IN THE REPORT. The objective of this exercise is to gain familiarity with these concepts. Electronics Lab #1 Transistor Current Source Task: Build and test a transistor current source, , +V with your choice of current (but don't exceed the transistor, power supply, or R ratings). R1 Rload You may wish to try more than one current. (1) Explain your choice of R1, R2, and Rsense. VCE (a) In particular, use the 0.6 V drop of VBE - rule for current flow to calculate I in R2 VBE Rsense terms of Rsense, and the Ic/Ib rule to estimate Ib hence the values of R1&R2. (2) Try your source over a wide range of Rload values, plot Iload vs. Rload and interpret. You may find it instructive to look at VBE and VCE with a floating (neither side grounded) multimeter. -

Current Source & Source Transformation Notes

EE301 – CURRENT SOURCES / SOURCE CONVERSION Learning Objectives a. Analyze a circuit consisting of a current source, voltage source and resistors b. Convert a current source and a resister into an equivalent circuit consisting of a voltage source and a resistor c. Evaluate a circuit that contains several current sources in parallel Ideal sources An ideal source is an active element that provides a specified voltage or current that is completely independent of other circuit elements. DC Voltage DC Current Source Source Constant Current Sources The voltage across the current source (Vs) is dependent on how other components are connected to it. Additionally, the current source voltage polarity does not have to follow the current source’s arrow! 1 Example: Determine VS in the circuit shown below. Solution: 2 Example: Determine VS in the circuit shown above, but with R2 replaced by a 6 k resistor. Solution: 1 8/31/2016 EE301 – CURRENT SOURCES / SOURCE CONVERSION 3 Example: Determine I1 and I2 in the circuit shown below. Solution: 4 Example: Determine I1 and VS in the circuit shown below. Solution: Practical voltage sources A real or practical source supplies its rated voltage when its terminals are not connected to a load (open- circuited) but its voltage drops off as the current it supplies increases. We can model a practical voltage source using an ideal source Vs in series with an internal resistance Rs. Practical current source A practical current source supplies its rated current when its terminals are short-circuited but its current drops off as the load resistance increases. We can model a practical current source using an ideal current source in parallel with an internal resistance Rs. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration.