First Generation Mainframes

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Weeel for the IBM 704 Data Processing System Reference Manual

aC sicru titi Wane: T| weeel for the IBM 704 Data Processing System Reference Manual FORTRAN II for the IBM 704 Data Processing System © 1958 by International Business Machines Corporation MINOR REVISION This edition, C28-6000-2, is a minor revision of the previous edition, C28-6000-1, but does not obsolete it or C28-6000. The principal change is the substitution of a new discussion of the COMMONstatement. TABLE OF CONTENTS Page General Introduction... ee 1 Note on Associated Publications Le 6 PART |. THE FORTRAN If LANGUAGE , 7 Chapter 1. General Properties of a FORTRAN II Source Program . 9 Types of Statements. 1... 1. ee ee ee we 9 Types of Source Programs. .......... ~ ee 9 Preparation of Input to FORTRAN I Translatorcee es 9 Classification of the New FORTRAN II Statements. 9 Chapter 2. Arithmetic Statements Involving Functions. ....... 10 Arithmetic Statements. .. 1... 2... ew eee . 10 Types of Functions . il Function Names. ..... 12 Additional Examples . 13 Chapter 3. The New FORTRAN II Statements ......... 2 16 CALL .. 16 SUBROUTINE. 2... 6 ee ee te ew eh ee es 17 FUNCTION. 2... 1 ee ee ww ew ew ww ew ew ee 18 COMMON ...... 2. ee se ee eee wee . 20 RETURN. 2... 1 1 ew ee te ee we wt wt wh wt 22 END... «4... ee we ee ce ew oe te tw . 22 PART Il, PRIMER ON THE NEW FORTRAN II FACILITIES . .....0+2«~W~ 25 Chapter 1. FORTRAN II Function Subprograms. 0... eee 27 Purpose of Function Subprograms. .....445... 27 Example 1: Function of an Array. ....... 2 + 6 27 Dummy Variables. -

The Operating System Handbook Or, Fake Your Way Through Minis and Mainframes

The Operating System Handbook or, Fake Your Way Through Minis and Mainframes by Bob DuCharme MVS Table of Contents Chapter 22 MVS: An Introduction.................................................................................... 22.1 Batch Jobs..................................................................................................................1 22.2 Interacting with MVS................................................................................................3 22.2.1 TSO.........................................................................................................................3 22.2.2 ISPF........................................................................................................................3 22.2.3 CICS........................................................................................................................4 22.2.4 Other MVS Components.........................................................................................4 22.3 History........................................................................................................................5 Chapter 23 Getting Started with MVS............................................................................... 23.1 Starting Up.................................................................................................................6 23.1.1 VTAM.....................................................................................................................6 23.1.2 Logging On.............................................................................................................6 -

The PORTHOS Executive System for the IBM 7094

A § 1 " * '& I m I ^ ;/ 1 ^ # **W : : : The Porthos Executive System for the IBM 7O9I+ User ' s Manual Table of Contents Title Sheet Preface Table of Contents 1. The 709^-1^01 Computer Installation 1.1. Description 1.1.1. General 1.1.2. Organization 1.1.3* Equipment 1.2. Programming Services 1.2.1. System Consulting 1.2.2. System Development 1.2.3- Associated Programmers 1.3« Library Services 1.3* 1' Program Documentation 1.3*2. Subroutines I.3. 3« Reference Publications 1.3.1+. The Mailing List 1.3' 5* Information Bulletins Date 5/1/65 Section Contents Page: 1 Change 2 Porthos Manual Digitized by the Internet Archive in 2012 with funding from University of Illinois Urbana-Champaign http://archive.org/details/porthosexecutivesyOOuniv : s 2. Use of the Computing Facility 2.1. Conditions of Use 2.1.1. Policy for Charging for Computer Use 2.1.2. Refunding of IBM 7094 Time Due to System or Machine Failures 2.1.2.1. In-System Jobs 2.1.2.2. Relinquish Jobs 2.2. Application for Use of Equipment 2.2.1. The Form 2.2.2. Submission and Approval 2.2.3. Entries on the Problem Specification Form 2.2.4. Changes in the Problem Specification 2.2.5. Problem Abstracts 2.3- Logging and Control of Computer Time 2.3«1« Accounting for Computer Time 2.3.2. Notices to Users Concerning Lapsing Time 2.3.3. Department Reports 2.3'3-l« Internal Reports 2. 3- 3* 2. The Technical Progress Report 2. -

Big Blue in the Bottomless Pit: the Early Years of IBM Chile

Big Blue in the Bottomless Pit: The Early Years of IBM Chile Eden Medina Indiana University In examining the history of IBM in Chile, this article asks how IBM came to dominate Chile’s computer market and, to address this question, emphasizes the importance of studying both IBM corporate strategy and Chilean national history. The article also examines how IBM reproduced its corporate culture in Latin America and used it to accommodate the region’s political and economic changes. Thomas J. Watson Jr. was skeptical when he The history of IBM has been documented first heard his father’s plan to create an from a number of perspectives. Former em- international subsidiary. ‘‘We had endless ployees, management experts, journalists, and opportunityandlittleriskintheUS,’’he historians of business, technology, and com- wrote, ‘‘while it was hard to imagine us getting puting have all made important contributions anywhere abroad. Latin America, for example to our understanding of IBM’s past.3 Some seemed like a bottomless pit.’’1 However, the works have explored company operations senior Watson had a different sense of the outside the US in detail.4 However, most of potential for profit within the world market these studies do not address company activi- and believed that one day IBM’s sales abroad ties in regions of the developing world, such as would surpass its growing domestic business. Latin America.5 Chile, a slender South Amer- In 1949, he created the IBM World Trade ican country bordered by the Pacific Ocean on Corporation to coordinate the company’s one side and the Andean cordillera on the activities outside the US and appointed his other, offers a rich site for studying IBM younger son, Arthur K. -

The Advent of Recursion in Programming, 1950S-1960S

The Advent of Recursion in Programming, 1950s-1960s Edgar G. Daylight?? Institute of Logic, Language, and Computation, University of Amsterdam, The Netherlands [email protected] Abstract. The term `recursive' has had different meanings during the past two centuries among various communities of scholars. Its historical epistemology has already been described by Soare (1996) with respect to the mathematicians, logicians, and recursive-function theorists. The computer practitioners, on the other hand, are discussed in this paper by focusing on the definition and implementation of the ALGOL60 program- ming language. Recursion entered ALGOL60 in two novel ways: (i) syn- tactically with what we now call BNF notation, and (ii) dynamically by means of the recursive procedure. As is shown, both (i) and (ii) were in- troduced by linguistically-inclined programmers who were not versed in logic and who, rather unconventionally, abstracted away from the down- to-earth practicalities of their computing machines. By the end of the 1960s, some computer practitioners had become aware of the theoreti- cal insignificance of the recursive procedure in terms of computability, though without relying on recursive-function theory. The presented re- sults help us to better understand the technological ancestry of modern- day computer science, in the hope that contemporary researchers can more easily build upon its past. Keywords: recursion, recursive procedure, computability, syntax, BNF, ALGOL, logic, recursive-function theory 1 Introduction In his paper, Computability and Recursion [41], Soare explained the origin of computability, the origin of recursion, and how both concepts were brought to- gether in the 1930s by G¨odel, Church, Kleene, Turing, and others. -

IBM Global Services: a Brief History

IBM Global Services: A Brief History IBM Corporate Archives May 2002 2405SH01 2 OVERVIEW Background In 1991 IBM was a $64.8 billion company, of which less than $6 billion was derived from non-maintenance services. Ten short years later, the business of information technology (IT) services alone generated more than 40 percent of IBM’s $86 billion in sales and had become the single largest source of revenue in IBM’s portfolio. How did that happen? It was partly the result of old-fashioned hard work and serious commitment: growing customer by customer; building disciplined management and financial systems; and investing to hire and train experts in everything from IT consulting to systems architecture and Web services. IBM used its financial strength to fund the expensive push into outsourcing, and the company placed informed bets on the future in areas such as IT utility services (“e-business on demand”) and hosted storage. But most important, the success of IBM Global Services came from something very simple: a clear understanding of customers’ needs. IBM saw that technology and business were converging to create something new and challenging for every kind of enterprise. And IBM had the deep experience in both areas to help its customers bring them together most effectively. The following pages offer a brief look at the history and growth of the organization that is today IBM’s top revenue generator. Definitions What are “services?” In the IT world, that broad term has encompassed dozens of offerings and meanings, including consulting, custom programming, systems integration (designing, building and installing complex information systems), systems operations (in which a vendor runs part or all of a company’s information systems), business innovation services (such as supply chain management), strategic outsourcing, application management services, integrated technology services (such as business recovery), networking services, learning services, security services, storage services and wireless services. -

Details Von Neumann/Turing Structure of Von Nuemann Machine

ENIAC - background 168 420 Computer Architecture ] Electronic Numerical Integrator And Computer ] Eckert and Mauchly Chapter 2 ] University of Pennsylvania Computer Evolution and ] Trajectory tables for weapons Performance ] Started 1943 ] Finished 1946 \ Too late for war effort ] Used until 1955 ENIAC - details ENIAC ] Decimal (not binary) ] 20 accumulators of 10 digits ] Programmed manually by switches ] 18,000 vacuum tubes ] 30 tons ] 15,000 square feet ] 140 kW power consumption ] 5,000 additions per second Structure of von Nuemann von Neumann/Turing machine ] Stored Program concept ] Main memory storing programs and data Arithmetic and Logic Unit ] ALU operating on binary data ] Control unit interpreting instructions from Input Output Main memory and executing Equipment Memory ] Input and output equipment operated by control unit ] Princeton Institute for Advanced Studies Program Control Unit \ IAS ] Completed 1952 1 IAS - details Structure of IAS - detail ] 1000 x 40 bit words Central Processing Unit Arithmetic and Logic Unit \ Binary number Accumulator MQ \ 2 x 20 bit instructions ] Set of registers (storage in CPU) Arithmetic & Logic Circuits \ Memory Buffer Register Input MBR Output Instructions \ Memory Address Register Main Equipment & Data \ Instruction Register Memory \ Instruction Buffer Register IBR PC MAR \ Program Counter IR Control \ Accumulator Circuits Address \ Multiplier Quotient Program Control Unit IAS Commercial Computers ] 1947 - Eckert-Mauchly Computer Corporation ] UNIVAC I (Universal Automatic Computer) ] -

The Largest Project in IT History New England Db2 Users Group Meeting Old Sturbridge Village, 1 Old Sturbridge Village Road, Sturbridge, MA 01566, USA

The Largest Project in IT History New England Db2 Users Group Meeting Old Sturbridge Village, 1 Old Sturbridge Village Road, Sturbridge, MA 01566, USA Milan Babiak Client Technical Professional + Mainframe Evangelist IBM Canada [email protected] Thursday September 26, AD2019 © 2019 IBM Corporation The Goal 2 © 2019 IBM Corporation AGENDA 1. IBM mainframe history overview 1952-2019 2. The Largest Project in IT History: IBM System/360 3. Key Design Principles 4. Key Operational Principles 5. Dedication 3 © 2019 IBM Corporation The Mainframe Family tree – 1952 to 1964 • Several mainframe families announced, designed for different applications • Every family had a different, incompatible architecture • Within families, moving from one generation to the next was a migration Common compilers made migration easier: FORTRAN (1957) 62 nd anniversary in 2019 COBOL (1959) 60 th anniversary in 2019 4 © 2019 IBM Corporation The Mainframe Family tree – 1952 to 1964 1st generation IBM 701 – 1952 IBM 305 RAMAC – 1956 2nd generation IBM 1401 – 1959 IBM 1440 – 1962 IBM 7094 – 1962 5 © 2019 IBM Corporation The April 1964 Revolution - System 360 3rd generation • IBM decided to implement a wholly new architecture • Specifically designed for data processing • IBM invested $5B to develop System 360 announced on April 7, 1964 IBM Revenue in 1964: $3.23B 6 © 2019 IBM Corporation Data Processing Software in Historical Perspective System 360 1964 IMS 1968 VSAM 1970s ADABAS by Software AG 1971 Oracle database by Oracle Corporation 1977 SMF/RMF system data 1980s -

IBM 1401 System Summary

File No. 1401-00 Form A24-1401-1 Systems Reference Library IBM 1401 System Summary This reference publication contains brief descriptions of the machine features, components, configurations, and special features. Also included is a section on pro grams and programming systems. Publications providing detailed information on sub jects discussed in this summary are listed in IB~I 1401 and 1460 Bibliography, Form A24-1495. Major Revision (September 1964) This publication, Form A24-1401-1, is a major revision of and obsoletes Form A24-1401-0. Significant changes have been made throughout the publication. Reprinted April 1966 Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the content of this publication to IBM Product Publications, Endicott, New York 13764. Contents IBM 1401 System Summary . ........... 5 System Concepts . ................ 6 Card-Oriented System .... ......... 11 Physical Features. 11 Interleaving. .. .................................... 14 Data Flow.... ... ... ... ... .. ... ... .. ................... 14 Checking ................................................... 15 Word Mark.. ... ... ... ... ... ... .. ... ... ... ........... 15 Stored-Program Instructions. .................. 15 Operation Codes . .. 18 Editing. .. ............ 18 IBM 1401 Console ............................................ 19 IBM 1406 Storage Unit. ........................... 20 Magnetic-Tape-Oriented System . ........................... 22 Data Flow ................................................. -

Computing Science Technical Report No. 99 a History of Computing Research* at Bell Laboratories (1937-1975)

Computing Science Technical Report No. 99 A History of Computing Research* at Bell Laboratories (1937-1975) Bernard D. Holbrook W. Stanley Brown 1. INTRODUCTION Basically there are two varieties of modern electrical computers, analog and digital, corresponding respectively to the much older slide rule and abacus. Analog computers deal with continuous information, such as real numbers and waveforms, while digital computers handle discrete information, such as letters and digits. An analog computer is limited to the approximate solution of mathematical problems for which a physical analog can be found, while a digital computer can carry out any precisely specified logical proce- dure on any symbolic information, and can, in principle, obtain numerical results to any desired accuracy. For these reasons, digital computers have become the focal point of modern computer science, although analog computing facilities remain of great importance, particularly for specialized applications. It is no accident that Bell Labs was deeply involved with the origins of both analog and digital com- puters, since it was fundamentally concerned with the principles and processes of electrical communication. Electrical analog computation is based on the classic technology of telephone transmission, and digital computation on that of telephone switching. Moreover, Bell Labs found itself, by the early 1930s, with a rapidly growing load of design calculations. These calculations were performed in part with slide rules and, mainly, with desk calculators. The magnitude of this load of very tedious routine computation and the necessity of carefully checking it indicated a need for new methods. The result of this need was a request in 1928 from a design department, heavily burdened with calculations on complex numbers, to the Mathe- matical Research Department for suggestions as to possible improvements in computational methods. -

MTS on Wikipedia Snapshot Taken 9 January 2011

MTS on Wikipedia Snapshot taken 9 January 2011 PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sun, 09 Jan 2011 13:08:01 UTC Contents Articles Michigan Terminal System 1 MTS system architecture 17 IBM System/360 Model 67 40 MAD programming language 46 UBC PLUS 55 Micro DBMS 57 Bruce Arden 58 Bernard Galler 59 TSS/360 60 References Article Sources and Contributors 64 Image Sources, Licenses and Contributors 65 Article Licenses License 66 Michigan Terminal System 1 Michigan Terminal System The MTS welcome screen as seen through a 3270 terminal emulator. Company / developer University of Michigan and 7 other universities in the U.S., Canada, and the UK Programmed in various languages, mostly 360/370 Assembler Working state Historic Initial release 1967 Latest stable release 6.0 / 1988 (final) Available language(s) English Available programming Assembler, FORTRAN, PL/I, PLUS, ALGOL W, Pascal, C, LISP, SNOBOL4, COBOL, PL360, languages(s) MAD/I, GOM (Good Old Mad), APL, and many more Supported platforms IBM S/360-67, IBM S/370 and successors History of IBM mainframe operating systems On early mainframe computers: • GM OS & GM-NAA I/O 1955 • BESYS 1957 • UMES 1958 • SOS 1959 • IBSYS 1960 • CTSS 1961 On S/360 and successors: • BOS/360 1965 • TOS/360 1965 • TSS/360 1967 • MTS 1967 • ORVYL 1967 • MUSIC 1972 • MUSIC/SP 1985 • DOS/360 and successors 1966 • DOS/VS 1972 • DOS/VSE 1980s • VSE/SP late 1980s • VSE/ESA 1991 • z/VSE 2005 Michigan Terminal System 2 • OS/360 and successors -

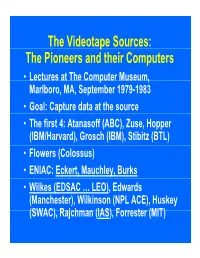

P the Pioneers and Their Computers

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA..