Operational Highlights

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Apple U1 Ultra Wideband (UWB) Analysis

Apple U1 Ultra Wideband (UWB) Analysis Product Brief – October 2019 techinsights.com All content © 2019. TechInsights Inc. All rights reserved. GLOBAL LEADER IN IP & TECHNOLOGY INTELLIGENCE By revealing the innovation others can’t inside advanced technology products, we prove patent value and drive the best Intellectual Property (IP) and technology investment decisions Technology Intelligence Intellectual Property Services We help decision makers in semiconductor, system, financial, We help IP Professionals in global technology companies, and communication service provider companies: licensing entities and legal firms to: • Discover what products are winning in the highest- • Build higher quality, more effective patents growth markets and why • Identify patents of value and gather evidence of use to • Spot or anticipate disruptive events, including the demonstrate this value entrance of new players • Obtain accurate data for planning a potential defensive • Understand state-of-the-art technology strategy or assertion case through independent, objective analysis • Make better portfolio management decisions to invest, • Make better, faster product decisions with greater abandon, acquire or divest confidence • Understand their competition, identify strategic partners, • Understand product costs and bill of materials acquisition targets and business threats 2 All content © 2019. TechInsights Inc. All rights reserved. TechInsights has been publishing technology analysis for 30 years, enabling our customers to advance their intellectual property -

TSMC Integrated Fan-Out (Info) Package Apple A10

Electronic Costing & Technology Experts 21 rue la Nouë Bras de Fer 44200 Nantes – France Phone : +33 (0) 240 180 916 email : [email protected] www.systemplus.fr September 2016 – Version 1 – Written by Stéphane ELISABETH DISCLAIMER : System Plus Consulting provides cost studies based on its knowledge of the manufacturing and selling prices of electronic components and systems. The given values are realistic estimates which do not bind System Plus Consulting nor the manufacturers quoted in the report. System Plus Consulting is in no case responsible for the consequences related to the use which is made of the contents of this report. The quoted trademarks are property of their owners. © 2016 by SYSTEM PLUS CONSULTING, all rights reserved. 1 Return to TOC Glossary 1. Overview / Introduction 4 – A10 Die Analysis 57 – Executive Summary – A10 Die View, Dimensions & Marking – Reverse Costing Methodology – A10 Die Cross-Section – A10 Die Process Characteristics 2. Company Profile 7 – Comparison with previous generation 65 – Apple Inc. – A9 vs. A10 PoP – Apple Series Application processor – A9 vs. A10 Process – Fan-Out Packaging – TSMC Port-Folio 4. Manufacturing Process Flow 70 – TSMC inFO packaging – Chip Fabrication Unit – Packaging Fabrication Unit 3. Physical Analysis 15 – inFO Reconstitution Flow – Physical Analysis Methodology – iPhone 7 Plus Teardown 17 5. Cost Analysis 81 – A10 Die removal – Synthesis of the cost analysis – A10 Package-on-Package Analysis 23 – Main steps of economic analysis – A10 Package View, Dimensions – Yields Hypotheses – A10 Package XRay View – Die Cost Analysis 86 – A10 Package Opening – Wafer Cost – A10 Package Marking – Die Cost – A10 Package Cross-Section – inFO Packaging Cost Analysis 90 – A10 Package Cross-Section – Adhesive & Passivation – Packaging Wafer Cost – A10 package cross-Section - TIVs – Packaging Cost per process Steps – A10 package cross-Section – Solder Balls – Component Cost – A10 package cross-Section – RDL – Land-Side Decoupling Capacitor Analysis 48 6. -

TSMC Investement in Arizona

Michael R. Splinter Chairman of the Board Senator Robert Menendez Senator Lisa A. Murkowski Honorary Co-Chair Honorary Co-Chair Rupert J. Hammond-Chambers President INTERNAL COMMENTARY: THE STRATEGIC IMPORTANCE OF THE TSMC ARIZONA INVESTMENT MAY 15, 2020 RUPERT J. HAMMOND-CHAMBERS PRESIDENT Taiwan Semiconductor Manufacturing Company (TSMC) is the world’s largest contract chip manufacturer. A key link in the global technology supply chain, it is the most important company most people have never heard of. TSMC, based in Taiwan, is now doubling down on its relationship with the United States in a big way. On Friday, May 15, 2020 TSMC announced the most important technology news of the year; the company committed to building a cutting-edge 5nm fabrication plant (fab) to produce semiconductor chips in Arizona. Its U.S. customers for the chips produced here will not only include U.S. tech companies, but will also include the Pentagon, defense contractors, and the national security community. The visionary founder of TSMC, Morris Chang, imagined a world where fabless semiconductor companies would absorb the financial burden of designing chips, but would outsource their actual production to his TSMC. His vision created a monster that dominates the sector he created - the foundry manufacturing sector – making almost 50% of all chips produced by foundries globally. TSMC’s state-of-the-art process technology and CAPEX investment of approximately US$15 billion/year ensures that it has few, if any, peers. Successive Taiwan governments have continued to nurture TSMC through prioritized access to land, power, and water, thereby allowing it to serve as the beating heart of Taiwan’s technology miracle. -

Semiconductors: a Changing of the Guard

Semiconductors: A Changing of the Guard Richard Spalton MA, CFA Investment Manager Semiconductors: A Changing of the Guard “While an early chip from the 1970s could fit thousands of micrometre-sized transistors, today’s most advanced chips are a complex web of billions of transistors, the smallest of which are just 10nm. To get some idea of how small that is: your fingernails grew 10nm in the time it took to read the previous sentence.”1 Background One of the key enablers of technological progress has been the constantly shrinking size of the transistors on semiconductor chips. Smaller transistors mean that the same number of computations can be completed faster, more efficiently and at lower cost. This concept was famously outlined by Gordon Moore, co-founder of Intel, who in 1965 wrote what became known as Moore’s Law. The manufacturing process for a particular size of transistor is called a process node. Shifting to a new node is highly complex and involves significant capital expenditure. In July 2020 Intel announced that their transition to the 7 nanometre node was running a year behind schedule. This delay will have a significant impact on Intel and its competitors. This announcement marks a changing of the guard in the semiconductor market, with leadership shifting away from Intel towards Taiwan Semiconductor Manufacturing Company (TSMC) and Samsung Electronics. Scale Matters Assessing the future prospects of a company requires an assessment of its industry. Manufacturing semiconductors is highly capital intensive – the industry spends USD 100bn per annum on capital expenditure. Companies also need to spend substantial amounts on R&D because each process node is more complex than the last. -

Needham's Semiconductor Expertise What Does The

The Growth Factor - Commentary by John Barr, [email protected] June 23, 2021 - Vol. 32 The Opportunity We See in Semiconductor Manufacturing (6 minute read) 2020 brought an unprecedented economic shutdown. The pandemic accelerated trends that we have been focused on for a long me; we call this the Great Digital and Life Sciences Acceleration. I would like to zero in on the opportunities in semiconductor manufacturing. I’ve long felt the semiconductor industry has moved beyond a cyclical, PC-driven industry to one of strategic importance. The confluence of manufacturing semiconductors for automotive, data center, machine learning, and remote work electronic systems; remaking the supply chain, and securing supplies for geopolitical needs have created a positive scenario for semiconductor manufacturing technology companies. Needham's Semiconductor Expertise Needham Funds have been owners of semiconductor manufacturing companies since our start in 1996. Needham Funds are an affiliate of Needham & Company, which has completed over 580 underwritings and M&A transactions for semiconductor companies since 1985. Addionally, prior to my Wall Street career, I spent 12 years in sales and markeng for Electronic Design Automaon companies, selling to semiconductor and electronic systems companies. I also spent 8 years as a sell-side senior research analyst following semiconductor design and technical soware companies. I served on the board of directors of venture capital-backed Coventor, Inc., which provided simulaon and modeling soluons for semiconductor process technology and was sold to Lam Research, Inc. in 2017. What Does the Opportunity in Semiconductor Manufacturing Mean for Needham Funds? Growth in advanced semiconductor manufacturing has been a dominant investment theme for Needham Funds for over 10 years. -

Annual Report 2002 TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY LTD

TSE: 2330 NYSE: TSM Taiwan Semiconductor Manufacturing Company, Ltd. Taiwan Semiconductor Manufacturing Company, Ltd. Semiconductor Manufacturing Company, Taiwan Annual Report 2002 121, Park Ave. 3, Science-Based Industrial Park, Hsin-Chu, Taiwan 300-77, R.O.C. Tel: 886-3-578-0221 Fax: 886-3-578-1546 http://www.tsmc.com Taiwan Semiconductor Manufacturing Company, Ltd. Annual Report 2002 • Taiwan Stock Exchange Market Observation Post System: http://mops.tse.com.tw • TSMC annual report is available at http://www.tsmc.com/english/tsmcinfo/c0203.htm Morris Chang, Chairman Printed on March 12, 2003 TABLE OF CONTENTS 3 LETTER TO THE SHAREHOLDERS 7 A BRIEF INTRODUCTION TO TSMC 7 Company Profile 8 Market Overview MAJOR FACILITIES TSMC SPOKESPERSON 9 Organization Corporate Headquarters & FAB 2, FAB 5 Name: Harvey Chang 18 Capital & Shares 121, Park Ave. 3 Title: Senior Vice President & CFO 22 Issuance of Corporate Bonds Science-Based Industrial Park Tel: 886-3-563-6688 Fax: 886-3-563-7000 23 Preferred Shares Hsin-Chu, Taiwan 300-77, R.O.C. Email: [email protected] 24 Issuance of American Depositary Shares Tel: 886-3-578-0221 Fax: 886-3-578-1546 26 Status of Employee Stock Option Plan (ESOP) Acting Spokesperson 26 Status of Mergers and Acquisitions FAB 3 Name: J.H. Tzeng 26 Corporate Governance 9, Creation Rd. 1 Title: Public Relations Department Manager 30 Social Responsibility Information Science-Based Industrial Park Tel: 886-3-563-6688 Fax: 886-3-567-0121 Hsin-Chu, Taiwan 300-77, R.O.C. Email: [email protected] 32 OPERATIONAL HIGHLIGHTS Tel: 886-3-578-1688 Fax: 886-3-578-1548 32 Business Activities AUDITORS 34 Customers FAB 6 Company: T N SOONG & CO 34 Raw Material Supply 1, Nan-Ke North Rd. -

TSMC'schipdominanceis Expectedtocontinueasit Plans$100Bexpansion

JUN 21 Gadjo Sevilla TSMC’s chip dominance is expected to continue as it plans $100B expansion Article The news: As most of the world relies on chip production from TSMC, the global shortage and the lack of a diversified semiconductor supply chain pose risks to the global economy, per The Wall Street Journal. How we got here: TSMC’s microchips are in billions of products ranging from iPhones, PCs, smart home devices, and IoT sensors. TSMC produces high-performance processors Copyright © 2021, Insider Intelligence Inc. All rights reserved. Page 1 designed by companies like Apple and Qualcomm for the latest smartphones and computers, but it also dominates the market for less-sophisticated microcontrollers used for automating smart cars and smart home appliances. Heavy reliance on a single chip producer is exposing risks to the global economy, a reality that’s only become clearer amid the global semiconductor shortage and which is resulting in higher costs being shouldered by consumers. Surging demand for electronics during the pandemic overwhelmed the semiconductor industry and led to a global shortage expected to last another 18 months, per CNBC. China, Europe, and the US have started to invest in various chip foundries to satisfy future demand and better diversify supply chains, but these eorts will have no eect on the current shortage. The bigger picture: Several chip manufacturers are building chip factories in the US, the scale of investment pales beside TSMC’s planned expansion, which will cost $100 billion over the next three years. TSMC’s investment is a quarter of the entire industry’s capital spending per VLSI Research. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies Peng Zheng Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2016-189 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-189.html December 1, 2016 Copyright © 2016, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. -

Intel Accelerated 2021 Presentation

Pat Gelsinger Intel CEO the leading provider of silicon globally internal factory external Intel network foundries foundry building a world-class foundry investing in IDM 2.0 strategy Arizona New Mexico Ocotillo campus campus $20B $3.5B IDM 2.0 advantage packaging silicon & process & platforms software at-scale manufacturing Industry Recognizes Node Naming Inconsistency “The picture the semiconductor technology node system paints is false. “We believe Intel 10SF is “Samsung and TSMC have made Most of the critical features of a 7-nm competitive with TSMC 7nm. I it to 7nm — roughly the equivalent transistor are actually considerably would expect Intel 7nm to be of Intel’s 10nm — and both are now larger than 7 nm, and that disconnect competitive with TSMC 3nm and actively pushing to 5nm and 3nm. between nomenclature and physical Intel 5nm to be competitive with But logic density will only carry a reality has been the case for about two TSMC 2nm.” design so far.” decades.” Samuel K. Moore Scotten Jones Ed Sperling “Today these numbers are just numbers. They’re like models in a car... it’s just a designation for the next technology node…. So let’s not confuse the name of the node with what the technology actually offers.” Philip Wong VP of Corporate Research TSMC, Hot Chips 31 Keynote Planar FET FinFET transistor transistor introducing new node naming Intel Intel Intel Intel 10nm SuperFin 7 4 3 20A previously referred to as previously Enhanced SuperFin referred to as 7nm www.Intel.com/ProcessInnovation the angstrom era of semiconductors Dr. Ann Kelleher Senior Vice President & General Manager Technology Development high volume production in Oregon, Arizona and Israel ~10-15% improvement in transistor performance per watt better improved power faster moving electrons energy control delivery Internal estimates, results may vary. -

Supplier Clean Energy April 2019 Program Update

Supplier Clean Energy April 2019 Program Update Apple is committed to addressing climate change and increasing the use of renewable energy. We launched the Supplier Clean Energy Program in October 2015 to advance the use of clean energy in our supply chain. We continue to demonstrate that powering operations with clean energy is good, not just for the environment, but for business, too. That’s why we’ve worked hard to source 100 percent renewable energy for all of Apple’s global facilities. When companies join the Supplier Clean Energy Program, they make a clear statement to Apple and to the broader business community that they share Apple’s beliefs and are ready to lead. Manufacturing is energy intensive and historically has relied heavily on fossil fuels. So we partner with our suppliers to ensure that clean energy is cost competitive and readily accessible in the markets where they operate. These efforts are helping to reduce product-related carbon emissions, create a more resilient supply chain, and contribute to healthier communities—while also paving the way for others to follow. Supplier Clean Energy Program The Supplier Clean Energy Program is integral to reducing Apple’s overall emissions. Manufacturing makes up 74 percent of Apple’s carbon footprint. And most of those emissions are from the electricity used to make the parts in our products. So we’re focused on increasing energy efficiency at supplier facilities, and then on transitioning suppliers to clean, renewable energy. As a first step, we’re partnering with our suppliers to generate and source more than 4 gigawatts of new clean energy in Apple’s global supply chain by 2020. -

Supplier Clean Energy 2021 Program Update FINAL

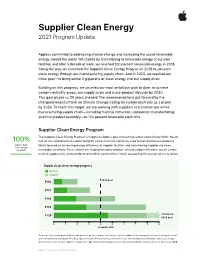

Supplier Clean Energy 2021 Program Update Apple is committed to addressing climate change and increasing the use of renewable energy around the world. We started by transitioning to renewable energy at our own facilities and after a decade of work, we reached 100 percent renewable energy in 2018. Along the way, we launched the Supplier Clean Energy Program in 2015 to advance clean energy through our manufacturing supply chain. And in 2020, we reached our initial goal—to bring online 4 gigawatts of clean energy into our supply chain. Building on this progress, we unveiled our most ambitious plan to date: to achieve carbon neutrality across our supply chain and in our product lifecycle by 2030. This goal places us 20 years ahead of the recommendations put forward by the Intergovernmental Panel on Climate Change calling for carbon neutrality as a planet by 2050. To reach this target, we are working with suppliers to transition our entire manufacturing supply chain—including material extraction, component manufacturing, and final product assembly—to 100 percent renewable electricity. Supplier Clean Energy Program The Supplier Clean Energy Program is integral to Apple’s goal of reaching carbon neutrality by 2030. Nearly 100% half of our comprehensive carbon footprint comes from the electricity used to manufacture our products. supply chain We’re focused on increasing energy efficiency at supplier facilities and transitioning suppliers to clean, clean energy by 2030 renewable electricity. These efforts are helping to reduce product-related carbon emissions, create a more resilient supply chain, and contribute to healthier communities—while also paving the way for others to follow. -

August 25, 2019 GLOBALFOUNDRIES V. TSMC Et Al

GLOBALFOUNDRIES v. TSMC et al Fact Sheet Plaintiffs (2): GLOBALFOUNDRIES US Inc. (U.S. cases) GLOBALFOUNDRIES Dresden Module One Limited Liability Company & Co. KG (German cases) Defendants (20): Foundry: Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) Fabless chip designers: Apple, Broadcom, Mediatek, nVidia, Qualcomm, Xilinx Electronic component distributors: Avnet/EBV, Digi-key, Mouser Consumer product: Arista, ASUS, BLU, Cisco, Google, HiSense, Lenovo, Motorola, TCL, OnePlus GF Patents in the cases (16): The technologies at issue relate to the advanced semiconductor devices and methods of manufacturing those devices. See table on next page for details. Accused Infringing Technologies (5): TSMC 7nm, 10nm, 12nm, 16nm , 28nm Courts/Tribunals (5) and Complaints (25) U.S. International Trade Commission (“ITC”) – 2 complaints (i.e. lawsuits) U.S. District Court for the District of Delaware – 6 complaints U.S. District Court for the Western District of Texas – 13 complaints Regional Court of Mannheim (“Landgericht Mannheim“) – 2 complaints Regional Court of Düsseldorf (“Landgericht Düsseldorf”) – 2 complaints see pp. 3-4 for details August 25, 2019 GF Patents in the cases Patent No. Title Inventors US 8,823,178 Bit Cell With Double Patterned Metal Layer Structures Juhan Kim, Mahbub Rashed US 8,581,348 Semiconductor device with transistor local Mahbub Rashed, Steven Soss, Jongwook Kye, Irene Y. Lin, interconnects James Benjamin Gullette, Chinh Nguyen, Jeff Kim, Marc Tarabbia, Yuansheng Ma, Yunfei Deng, Rod Augur, Seung- Hyun Rhee, Scott Johnson, Subramani Kengeri Suresh Venkatesan US 9,355,910 Semiconductor device with transistor local Mahbub Rashed, Irene Y. Lin, Steven Soss, Jeff Kim, interconnects Chinh Nguyen, Marc Tarabbia, Scott Johnson, Subramani Kengeri, Suresh Venkatesan US 7,425,497 Introduction of metal impurity to change workfunction Michael P.