ASP-DAC 2017 Advance Program

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Third Quarter Results

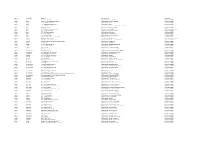

Consolidated Financial Results for the First Nine Months from April 1 to December 31, 2016 2017・1・31 Index 02 Highlights of the Third Quarter, FY2017 09 Unit Information Copyright 2017 Nomura Real Estate Holdings, Inc. 1 Highlights of the Third Quarter, FY2017 Copyright 2017 Nomura Real Estate Holdings, Inc. 2 Summary of Financial Results • The cumulative result of FY2017 3Q was as follows: Operating revenue;¥368.9 billion (down 3.1% y/y); operating income; ¥49.1 billion (down 7.4% y/y); ordinary income;¥42.9 billion (down 8.8% y/y); and profit attributable to owners of parent;¥29.1 billion (increase 2.7% y/y). • In the Residential Development Unit, the number of housing units sold decreased to 3,074 (down 711 units y/y) while gross margin ratio and housing prices increased. The contract progress rate for the planned 5,650 units of this consolidated fiscal year was 90.1% as of the end of the current third quarter. • In the leasing business, tenant leasing made a satisfactory progress, and the vacancy rate as of the end of the third quarter improved to 1.0% (down 1.2 points from the end of the previous fiscal year). • Service Management Sector which consists of 3 Units, the Investment Management Unit, the Property Brokerage & CRE Unit, and the Property & Facility Management Unit marked a smooth progress. Especially in the Property Brokerage & CRE Unit, both the number of transactions and transaction value marked the highest figure ever as the third quarter. • No change in the consolidated operating result forecast and dividend forecast which was announced in October, 2016. -

Annual Report 2013 1

Otemachi Building, 6-1, Otemachi 1-chome, Chiyoda-ku, Tokyo 100-8133, Japan http://www.mec.co.jp/index_e.html ANNUAL REPORT2013 Approx. 296m Approx. 240m Approx. Approx. 205m 180m Approx. 36m Approx. 20m Yokohama Landmark Tower Sunshine 60 McGraw-Hill Building Marunouchi Building Paternoster Square Mitsubishi Ichigokan ANNUAL REPORT This report is printed using paper that con- This report has been prepared using tains raw materials certified by the Forest 100% vegetable ink. Every effort is Stewardship Council (FSC)®. FSC ® certifi cation made to contain the incidence of vol- Fiscal Year ended ensures that materials have been harvested atile organic compounds (VOCs) and from properly managed forests. to preserve petroleum resources. Printed in Japan March 31, 2013 2013 113mec_ar表紙英文0815_初戻P.indd3mec_ar表紙英文0815_初戻P.indd 11-2-2 113/09/063/09/06 116:376:37 MITSUBISHI ESTATE CO., LTD. ANNUAL REPORT 2013 1 A Love for People A Love for the City Forever Taking on New Challenges–The Mitsubishi Estate Group Our wish is to provide people who live in, work in and visit the city with enriching and fulfi lling lives, full of stimulating opportunities to meet. The Mitsubishi Estate Group has always pursued the genuine value sought by people in the environments and services it provides. With an eye to the future, we carefully listen to each and every customer, and create the true value they seek. We wish to share with our customers the inspiration and passion we derive from our work. We will constantly take on new challenges to achieve this vision, and through it, we will continuously evolve. -

Notice of Conclusion of Fixed-Term Building Lease Renewal Agreement on AEON MALL Tsudanuma

September 30, 2019 To all concerned parties: Investment Corporation MCUBS MidCity Investment Corporation Representative: Katsuhiro Tsuchiya, Executive Director TSE Code: 3227, LEI Code: 353800WZPKHG2SQS1P32 URL: https://www.midcity-reit.com/en/ Asset Management Company Mitsubishi Corp.‐ UBS Realty Inc. Representative: Katsuji Okamoto, President & CEO Inquiries: Katsura Matsuo, Head of Office Division TEL: +81-3-5293-4150 Notice of Conclusion of Fixed-Term Building Lease Renewal Agreement on AEON MALL Tsudanuma MCUBS MidCity Investment Corporation (hereafter "MCUBS MidCity") has entered into a fixed-term building lease renewal agreement with AEON RETAIL Co., Ltd., one of the major tenant of MCUBS MidCity, as follows. 1. Background of conclusion of the Renewal Agreement (1) Environment surrounding the AEON MALL Tsudanuma "AEON MALL Tsudanuma" (Narashino City, Chiba) (hereafter "the Property") owned by MCUBS MidCity is a retail property that is directly connected to “Shin-Tsudanuma” station on the Shin-Keisei Line. The population of Narashino City and the neighboring Funabashi City has been consistently increasing since 2011. At the same time, the population of those with purchasing power is high in terms of income and age, and hence the potential for retail property is high. Also, in March 2016, Narashino City formulated the "Policy for Considering Community Development around JR Tsudanuma Station" and designated the area connecting JR “Tsudanuma” station and Shin-Keisei Line "Shin-Tsudanuma" station as the entrance to the city front, which promotes redevelopment by the private sector. As a result, redevelopment around the station is expected in the future. (2) Background to conclusion of the Renewal Agreement AEON RETAIL Co., Ltd. -

Haneda Airport Route(*PDF File)

1 of 3 Bus stop valid for Limousine & Subway pass(Haneda Airport route) Area Bus Stop Useable Area Bus Stop Useable Century Southern Tower ○ The Capitol Hotel Tokyu ○ Hotel Sunroute Plaza Shinjuku ○ Grand Hyatt Tokyo ○ Hilton Tokyo ○ ANA InterContinental Tokyo ○ Shinjuku Washington Hotel The Okura Tokyo ○ Akasaka Roppongi, ○ Park Hyatt Tokyo ○ Toranomon Hills ○ Hyatt Regency Tokyo Andaz Tokyo ○ Toranomon ○ Shinjuku Keio Plaza Hotel ○ HOTEL THE CELESTINE TOKYO SHIBA ○ Shinjuku Station/West ○ Shiba Park Hotel ○ Shinjuku Expressway Bus Terminal ○ Tokyo Prince Hotel ○ 【Early Morning Service】Shinjuku Expressway Bus Terminal × The Prince Park Tower Tokyo ○ 【Early Morning Service】Higashi Shinjuku Station × The Westin Tokyo ○ T-CAT Tokyo City Air Terminal ○ Sheraton Miyako Hotel Tokyo ○ Ikebukuro Sunshine Bus Terminal ○ Tokyo Marriott Hotel ○ Sunshine City Prince Hotel Shinagawa Prince Hotel ○ Shinagawa Ebisu, Shiba, ○ Hotel Metropolitan ○ The Prince Sakura Tower Tokyo ○ Ikebukuro Ikebukuro Station/West ○ Grand Prince Hotel Takanawa ○ 【Early Morning Service】Ikebukuro Station/East × Grand Prince Hotel New Takanawa ○ Hotel Chinzanso Tokyo ○ Shibuya Excel Hotel Tokyu × Tokyo Dome Hotel ○ Shibuya Station/West × Akihabara Station Shibuya Station(SHIBUYA FUKURAS) ○ Shibuya × Akihabara 【Early Morning Service】Akihabara Station Cerulean Tower Tokyu Hotel Mejiro, Mejiro, Kourakuen, × × HOSHINOYA Tokyo/Otemachi Financial City Grand Cube ○ ARIAKE GARDEN × Marunouchi Tokyo Station/Marunouchi North SOTETSU GRAND FRESA TOKYO-BAY ARIAKE , ○ × Otemachi Tokyo -

Haneda Airport Route(*PDF File)

1 of 3 Bus stop valid for Airport Limousine Bus Premium Coupon(Haneda Airport route) required required Area Bus Stop Useable Area Bus Stop Useable number number Century Southern Tower ○ 1 coupon The Capitol Hotel Tokyu ○ 1 coupon Hotel Sunroute Plaza Shinjuku ○ 1 coupon Grand Hyatt Tokyo ○ 1 coupon Hilton Tokyo ○ 1 coupon ANA InterContinental Tokyo ○ 1 coupon Shinjuku Washington Hotel 1 coupon The Okura Tokyo 1 coupon ○ Akasaka Roppongi, ○ Park Hyatt Tokyo ○ 1 coupon Toranomon Hills × × Hyatt Regency Tokyo 1 coupon Andaz Tokyo 1 coupon ○ Toranomon ○ Shinjuku Keio Plaza Hotel ○ 1 coupon HOTEL THE CELESTINE TOKYO SHIBA ○ 1 coupon Shinjuku Station/West ○ 1 coupon Shiba Park Hotel ○ 1 coupon Shinjuku Expressway Bus Terminal ○ 1 coupon Tokyo Prince Hotel ○ 1 coupon 【Early Morning Service】Shinjuku Expressway Bus Terminal ○ 2 coupons The Prince Park Tower Tokyo ○ 1 coupon 【Early Morning Service】Higashi Shinjuku Station ○ 2 coupons The Westin Tokyo ○ 1 coupon T-CAT Tokyo City Air Terminal ○ 1 coupon Sheraton Miyako Hotel Tokyo ○ 1 coupon Ikebukuro Sunshine Bus Terminal ○ 1 coupon Tokyo Marriott Hotel ○ 1 coupon Sunshine City Prince Hotel 1 coupon Shinagawa Prince Hotel 1 coupon ○ Shinagawa Ebisu, Shiba, ○ Hotel Metropolitan ○ 1 coupon The Prince Sakura Tower Tokyo ○ 1 coupon Ikebukuro Ikebukuro Station/West ○ 1 coupon Grand Prince Hotel Takanawa ○ 1 coupon 【Early Morning Service】Ikebukuro Station/East ○ 2 coupons Grand Prince Hotel New Takanawa ○ 1 coupon Hotel Chinzanso Tokyo ○ 1 coupon Shibuya Excel Hotel Tokyu × × Tokyo Dome Hotel ○ 1 coupon -

Area Locality Address Description Operator Aichi Aisai 10-1

Area Locality Address Description Operator Aichi Aisai 10-1,Kitaishikicho McDonald's Saya Ustore MobilepointBB Aichi Aisai 2283-60,Syobatachobensaiten McDonald's Syobata PIAGO MobilepointBB Aichi Ama 2-158,Nishiki,Kaniecho McDonald's Kanie MobilepointBB Aichi Ama 26-1,Nagamaki,Oharucho McDonald's Oharu MobilepointBB Aichi Anjo 1-18-2 Mikawaanjocho Tokaido Shinkansen Mikawa-Anjo Station NTT Communications Aichi Anjo 16-5 Fukamachi McDonald's FukamaPIAGO MobilepointBB Aichi Anjo 2-1-6 Mikawaanjohommachi Mikawa Anjo City Hotel NTT Communications Aichi Anjo 3-1-8 Sumiyoshicho McDonald's Anjiyoitoyokado MobilepointBB Aichi Anjo 3-5-22 Sumiyoshicho McDonald's Anjoandei MobilepointBB Aichi Anjo 36-2 Sakuraicho McDonald's Anjosakurai MobilepointBB Aichi Anjo 6-8 Hamatomicho McDonald's Anjokoronaworld MobilepointBB Aichi Anjo Yokoyamachiyohama Tekami62 McDonald's Anjo MobilepointBB Aichi Chiryu 128 Naka Nakamachi Chiryu Saintpia Hotel NTT Communications Aichi Chiryu 18-1,Nagashinochooyama McDonald's Chiryu Gyararie APITA MobilepointBB Aichi Chiryu Kamishigehara Higashi Hatsuchiyo 33-1 McDonald's 155Chiryu MobilepointBB Aichi Chita 1-1 Ichoden McDonald's Higashiura MobilepointBB Aichi Chita 1-1711 Shimizugaoka McDonald's Chitashimizugaoka MobilepointBB Aichi Chita 1-3 Aguiazaekimae McDonald's Agui MobilepointBB Aichi Chita 24-1 Tasaki McDonald's Taketoyo PIAGO MobilepointBB Aichi Chita 67?8,Ogawa,Higashiuracho McDonald's Higashiura JUSCO MobilepointBB Aichi Gamagoori 1-3,Kashimacho McDonald's Gamagoori CAINZ HOME MobilepointBB Aichi Gamagori 1-1,Yuihama,Takenoyacho -

Integration of the Lalaport Financial Center and the Tsudanuma Consulting Spot

May 2011 Dear customers with accounts opened at the LaLaport Financial Center or the Tsudanuma Consulting Spot, Integration of the LaLaport Financial Center and the Tsudanuma Consulting Spot We would like to inform customers that the LaLaport Financial Center and the Tsudanuma Consult- ing Spot will be integrated. As a result, the LaLaport Financial Center will close as of Sunday, July 31, 2011, and the existing Tsudanuma Consulting Spot will be renamed the Tsudanuma Financial Center effective Monday, August 1, 2011. We thank you for your long patronage of these branches. Any of the Shinsei Financial Centers including the Tsudanuma Financial Center, which is the current Tsudanuma Consulting Spot, will welcome your future business. No changes will occur to the cash card, branch code, and account number customers use. However, the branch name will become “Tsudanuma” effective Monday, August 1, 2011 instead of “LaLaport”. Please note that the branch name of “Tsudanuma” is specified for salary transfers and fund trans- fers from Monday, August 1, 2011. For more detailed information and specific requests that need to be carried out for the branch name change, please read the reverse of this letter. We apologize for any inconvenience it may cause you. Your understanding is appreciated, and we look forward to continuing to serve you. Yours faithfully, A List of Branches in the Vicinity of LaLaport Financial Center Tsudanuma Financial Center To Funabashi To Yotsukaido Toyoko Inn LAWSON The existing Tsudanuma Consulting Spot will be To Ichikawa renamed the Tsudanuma Financial Center effective FamilyMart To Matsudo August 1, 2011. PARCO B Tsudanuma Address: 2-21-1, Maebara-nishi, Funabashi-shi, Chiba, Tsudanuma Sta. -

Fiscal Year Ended March 31, 2018 (FY2017) Results Presentation

Representative Director and President Fiscal Year Ended March 31, 2018 Keisei Electric Railway Co. , Ltd. (FY2017) Results Presentation May 9, 2018 Toshiya Kobayashi Contents I. Results of Fiscal Year Ended March 31, 2018 II. Initiatives for Fiscal Year Ended March 31, 2019 III. Results Forecast for Fiscal Year Ending March 31, 2019 IV. Progress in E3 Plan V. Reference Material Copyright © Keisei Electric Railway Co., Ltd. 1 1. Overview of Results (Year on Year) Operating revenue, Operating income, and ordinary income posted record highs. FY2017 FY2016 % Changes in operating revenue (by segment) Million yen, % Change ■ unit: million yen Result Result Change 3538 Operating revenue 255,028 245,837 9,191 3.7 2,762 581 4,571 166 -1,514 Operating income 30,085 30,048 36 0.1 -914 255,028 (Operating income 11.8 12.2 -0.4pt - margin) 245, 837 FY2016 Transportation Distribution Real Leisure, Construction Other Elimination FY2017 estate service Ordinary income 47,145 47,064 80 0.2 FY2016 Transportation Distribution Real Leisure, Construction Other Elimination FY2017 estate service Share of profit of entities accounted for using equity 18,178 18,991 -812 -4.3 method ■ Changes in operating income (by segment) unit: million yen Net profit attributable 1,029 210 to owners of parent 34,811 35,711 -900 -2.5 -133 -2 -56 Depreciation 25,531 23,891 1,639 6.9 -752 -258 30,048 30,085 Interest-bearing debt outstanding* 302,301 314,348 -12,046 -3.8 EBITDA multiple* 5.5 5.9 -0.4pt - FY2016 Transportation Distribution Real Leisure, Construction Other Elimination FY2017 estate service FY2016 Transportation Distribution Real Leisure, Construction Other Elimination FY2017 • EBITDA multiple = Interest-bearing debt outstanding / (Operating income + estate service Depreciation and amortization) Interest-bearing debt outstanding includes lease obligations. -

Results Presentation

First Half of Fiscal Year Ending March 31, 2017 (FY2016) Results Presentation We aim to connect smiles. Keisei Electric Railway November 17, 2016 TSE First Section 9009 Contents 1. Management Overview 2. Progress in E3 Plan 3. Consolidated Results in First Half of Fiscal Year Ending March 31, 2017 4. Consolidated Results Forecast for Fiscal Year Ending March 31, 2017 5. Trends in Consolidated Results 6. Reference Material Copyright © Keisei Electric Railway Co., Ltd. 2 Consolidated Results Forecast for FY2016 Overview of Results Forecast Operating revenue: ¥246.4bn Down ¥0.6bn, reflecting a rise in the transportation business and store closings in the distribution business Operating income: ¥28.2bn Up ¥1.2bn due to a rise in the transportation business and falls in electric rates and fuel costs FY2016 FY2016 Percentage Change E3 Plan target Revised forecast Initial forecast change Operating revenue ¥246.4bn ¥247.0bn -¥0.6bn -0.2% – Operating income ¥28.2bn ¥27.0bn ¥28.0bn or more +¥1.2bn +4.6% (Operating income margin) (11.4%) (10.9%) (11% or more) Ordinary income ¥43.8bn ¥42.6bn +¥1.2bn +2.8% ¥44.0bn or more Net profit attributable to ¥32.7bn ¥31.8bn +¥0.9bn +2.9% – owners of parent Interest-bearing debt ¥317.8bn ¥322.1bn ¥325.0bn maximum outstanding -¥4.3bn – (6.1 times maximum) (EBITDA multiple) (6.1 times) (6.4 times) Interest-bearing debt includes lease obligations. EBITDA multiple = Interest-bearing debt outstanding / (Operating income + Depreciation and amortization) Copyright © Keisei Electric Railway Co., Ltd. 3 Results in Railway -

![Presentation [PDF/551KB]](https://docslib.b-cdn.net/cover/0831/presentation-pdf-551kb-6430831.webp)

Presentation [PDF/551KB]

FY2011.3 Second Quarter Financial Results Presentation October 29, 2010 East Japan Railway Company Contents I. FY2011.3 Second Quarter Financial Results (summary) III. Reference Material (Overview of Forward-Looking Initiatives) Main Points of FY2011.3 Second Quarter Financial Results (consolidated) 4 Near-Term Initiatives for Growth (Transportation) 28 Main Points of FY2011.3 Second Quarter Financial Results (non-consolidated) 5 Near-Term Initiatives for Growth (Life-Style Businesses) 29 Main Points of FY2011.3 Business Results Forecast Revision 6 Topics: Initiatives in Inbound Tourism Businesses 30 FY2011.3 Business Results Forecast (consolidated) 7 Topics: Initiatives in Life-Style Businesses 31 FY2011.3 Business Results Forecast (non-consolidated) 8 IV. Reference Material (Data) Uses of Consolidated Cash Flows 9 FY2013.3 Numerical Targets (by segment) 33 II. Second Quarter Non-consolidated and Consolidated Financial Results FY2013.3 Numerical Targets 34 FY2011.3 Passenger Revenues - Main Positive and Negative Factors (2Q cumulative) 11 Passenger Revenues 35 FY2011.3 Target for Passenger Revenues 12 Traffic Volume 36 Topics: FY2011.3 Passenger Revenues Results and Targets 13 Topics: Investment in Life-Style Businesses 37 FY2011.3 Non-consolidated Operating Expenses Development of ecute 38 - Main Positive and Negative Factors 14 Development of Tokyo Station City 39 FY2011.3 Approach to Forecast of Energy Cost 15 Hotel Operations - Overview 40 FY2011.3 Non-consolidated Financial Results 16 Suica 41 FY2011.3 Transportation 17 Suica Electronic -

JR East Group Sustainability Report 2018

■Creation of new stations to develop the railway network Topics Promoting Open Innovation : Collaborating with Venture Companies We are also cooperating with local governments in the creation of new stations in line with their city planning, based on requests from local In order to swiftly create new businesses railways, and the Group businesses’s management governments, etc. In April 2018, we opened a and services as passengers’ needs and the and information resources from venture new station, Ashikaga Flower Park Station, on the management environment change rapidly, JR companies and individuals with various ideas. In Ryomo Line. East requires expertise in unknown technologies FY2018, the program received 237 proposals, Ashikaga Flower Park Station, Ryomo Line Safety and business fields where we lack experience. from which 19 were selected for development. Of Therefore, in addition to leveraging our internal these, 11 have been implemented on a trial basis, resources, we are also collaborating with venture including an unstaffed store at Omiya Station companies, universities, and other research and baggage check service at Tokyo Station. organizations and will be proactively adopting Collaboration with a view to commercialization is Opening New Station in Collaboration with the Local Community their technologies and expertise. As part of these currently under way for several other proposals. efforts, in February 2018, we established JR East For the second edition of the program in FY2019, Ashikaga Station Staff, Takasaki Branch Office Startup Co., Ltd. for the purpose of speeding up there will be expanding themes to include new the promotion of open innovation. By creating areas such as partnerships with communities (local On April 1, 2018, Ashikaga Flower Park Station opened on the Ashikaga Flower Park is very popular Society new businesses and services through the governments, etc.) and collaboration with foreign Ryomo Line. -

![Non-Transportation [PDF/281KB]](https://docslib.b-cdn.net/cover/3246/non-transportation-pdf-281kb-6963246.webp)

Non-Transportation [PDF/281KB]

REVIEW OF OPERATIONS—NON-TRANSPORTATION STATION RENAISSANCE— CREATING NEW STATION ENVIRONMENTS FOR THE 21st CENTURY Since establishment, JR East has moved decisively to leverage the potential synergy of its business resources such as high-traffic stations and adjacent commercial spaces. Creation of convenient and attractive retail-store, restaurant, office, hotel and other facilities will deliver sustainable revenue growth and complementary business diversity. Shopping Centers & Office Buildings In April 2002, JR East and Tokyu Corporation jointly opened the JR Tokyu Meguro Building. A subsidiary of JR East is renting out office space and operating a shop- ping center there. Station Space Utilization JR East continued its efforts to improve the attractiveness and earning power of its stations. Tsudanuma and Asagaya stations were enhanced through Cosmos Plan initiatives implement- ed in November 2002 and May 2003, respectively. Sunflower Plan initiatives were imple- mented at 67 stations, including Mejiro, Osaki, Sakuragicho, Hashimoto and Hachinohe. 32 EAST JAPAN RAILWAY COMPANY ANNUAL REPORT 2003 Cosmos Plan Shops/ Convenience Introduced in December 2000, the Cosmos Plan involves com- Convenience Restaurants store prehensive reviews of existing operational facilities at stations where passenger numbers are in excess of 200 thousand per day and major terminal stations in prefectural capitals. In addi- tion, substantial new station spaces are being newly created through various methods, including the construction of artificial ground. Sunflower Plan Ticket gate Commercial Launched in fiscal 1998, the Sunflower Plan mainly targets sta- space tions with passenger numbers generally in excess of 30 thou- Station sand per day. Activities include partial reviews of operational Artificial office facilities at and around stations and short construction sched- ground ules with minimal investment to develop stores.