Simms & OTHER MEMORY MODULES

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Different Types of RAM RAM RAM Stands for Random Access Memory. It Is Place Where Computer Stores Its Operating System. Applicat

Different types of RAM RAM RAM stands for Random Access Memory. It is place where computer stores its Operating System. Application Program and current data. when you refer to computer memory they mostly it mean RAM. The two main forms of modern RAM are Static RAM (SRAM) and Dynamic RAM (DRAM). DRAM memories (Dynamic Random Access Module), which are inexpensive . They are used essentially for the computer's main memory SRAM memories(Static Random Access Module), which are fast and costly. SRAM memories are used in particular for the processer's cache memory. Early memories existed in the form of chips called DIP (Dual Inline Package). Nowaday's memories generally exist in the form of modules, which are cards that can be plugged into connectors for this purpose. They are generally three types of RAM module they are 1. DIP 2. SIMM 3. DIMM 4. SDRAM 1. DIP(Dual In Line Package) Older computer systems used DIP memory directely, either soldering it to the motherboard or placing it in sockets that had been soldered to the motherboard. Most memory chips are packaged into small plastic or ceramic packages called dual inline packages or DIPs . A DIP is a rectangular package with rows of pins running along its two longer edges. These are the small black boxes you see on SIMMs, DIMMs or other larger packaging styles. However , this arrangment caused many problems. Chips inserted into sockets suffered reliability problems as the chips would (over time) tend to work their way out of the sockets. 2. SIMM A SIMM, or single in-line memory module, is a type of memory module containing random access memory used in computers from the early 1980s to the late 1990s . -

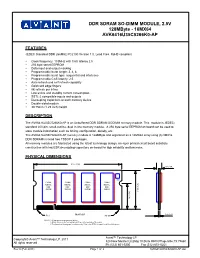

DDR SDRAM SO-DIMM MODULE, 2.5V 128Mbyte - 16MX64 AVK6416U35C5266K0-AP

DDR SDRAM SO-DIMM MODULE, 2.5V 128MByte - 16MX64 AVK6416U35C5266K0-AP FEATURES JEDEC Standard DDR 266MHz PC2100 Version 1.0, Lead Free, RoHS compliant Clock frequency: 133MHz with CAS latency 2.5 256 byte serial EEPROM Data input and output masking Programmable burst length: 2, 4, 8 Programmable burst type: sequential and interleave Programmable CAS latency: 2.5 Auto refresh and self refresh capability Gold card edge fingers 8K refresh per 64ms Low active and standby current consumption SSTL-2 compatible inputs and outputs Decoupling capacitors at each memory device Double-sided module 30.75mm (1.25 inch) height DESCRIPTION The AVK6416U35C5266K0-AP is an Unbuffered DDR SDRAM SODIMM memory module. This module is JEDEC- standard 200-pin, small-outline, dual in-line memory module. A 256 byte serial EEPROM on board can be used to store module information such as timing, configuration, density, etc. The AVK6416U35C5266K0-AP memory module is 128MByte and organized as a 16MX64 array using (8) 8MX16 DDR SDRAMs in lead free TSSOP II packages. All memory modules are fabricated using the latest technology design, six-layer printed circuit board substrate construction with low ESR decoupling capacitors on-board for high reliability and low noise. PHYSICAL DIMENSIONS 67.60 (2.66) 3.50 (0.14) SPD 128Mbit 128Mbit 128Mbit 128Mbit ) 5 8MbX16 8MbX16 8MbX16 8MbX16 2 . 1 ( DDR DDR DDR DDR 5 7 SDRAM SDRAM SDRAM SDRAM . 1 ) 3 7 8 7 . 0 ( 0 2 FRONT SIDE 1.00 (0.04) Pin 1 Pin 199 NOTES: 1- All dimensions are in milimeters (inches) 2- All blue ICs are on the front, and all red ICs are on the back side of the module. -

Baby Steps to Our Future by Ron Fenley

Baby Steps to our Future by Ron Fenley Memory – Past, Present and Future, Part 2 of 3 Memories,… food for the EGO. Manifestation of memories into self-esteem, honor, dignity and many other traits characterize the individual. Obviously, memories are stored in the brain and scientist have identified, subdivided, labeled and compartmentalized the brain in many functional regions. Computer memory like human memory manifests it presents in different ways to perform a variety of functions; and computer memory has been divided into partitions, subsystems and specialization. Although the memory in today’s computers have not been programmed with personality traits, some PC systems do demonstrate personality disorders, particularly the one this article was written with. There is an abundance of terms that have been used to describe or label computer memory functions, features and attributes. Some terms apply to the hardware technology, some terms apply to the packing of these chips and others apply to the memory usage or memory systems within the computer. Collectively, all of these terms may be confusing and to help sort out and clarify these labels we will look at how these items have been applied to computer memory. To simplify this task, the effort will be divided into the following 5 areas: packing, parity & ECC, buffered/non-buffered, systems and labels. MEMORY PACKAGING Just as memory technology has evolved so has memory packaging. Shown below is a table of the different form factors (packaging) that has been used in memory deployment over -

Micron Technology Inc

MICRON TECHNOLOGY INC FORM 10-K (Annual Report) Filed 10/26/10 for the Period Ending 09/02/10 Address 8000 S FEDERAL WAY PO BOX 6 BOISE, ID 83716-9632 Telephone 2083684000 CIK 0000723125 Symbol MU SIC Code 3674 - Semiconductors and Related Devices Industry Semiconductors Sector Technology Fiscal Year 03/10 http://www.edgar-online.com © Copyright 2010, EDGAR Online, Inc. All Rights Reserved. Distribution and use of this document restricted under EDGAR Online, Inc. Terms of Use. UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended September 2, 2010 OR TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to Commission file number 1-10658 Micron Technology, Inc. (Exact name of registrant as specified in its charter) Delaware 75 -1618004 (State or other jurisdiction of (IRS Employer incorporation or organization) Identification No.) 8000 S. Federal Way, Boise, Idaho 83716 -9632 (Address of principal executive offices) (Zip Code) Registrant ’s telephone number, including area code (208) 368 -4000 Securities registered pursuant to Section 12(b) of the Act: Title of each class Name of each exchange on which registered Common Stock, par value $.10 per share NASDAQ Global Select Market Securities registered pursuant to Section 12(g) of the Act: None (Title of Class) Indicate by check mark if the registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. -

Swissbit SMT Memory Product Guide Rev1.9.Pub

SWISSMEMORY™ Industrial Product Line DRAM Memory Products Solutions for Industrial and Embedded Applications Surface Mount Technology (SMT) DDR3 DDR2 DDR SDRAM DRAM Visit us at www.swissbit.com Version 1.9 - 01/2009 DDR3 SDRAM TECHNOLOGY SDRAM DDR3 modules are Swissbit’s most recent Double Data Rate products to market. DDR3 is the memory choice for performance driven systems with clock frequencies of 400 to 800MHz and data rates of 800 to 1600 Mb per second. In addition to DDR3’s improved performance in dual- and multi-core systems, it also provides increased efficiency with lower power consumption. DDR3 power consumption is approximately 20% or more lower than its predecessor at 1.35V to 1.5V as compared to the 1.8V of DDR2. Swissbit offers DDR3’s unmatched combination of high bandwidth and density with lower power consumption in the variety of module packages. Density Swissbit PN Data Rate (MT/s) - CL Height # IC’s IC Org Rank DDR3 SDRAM UDIMM (240 pin) 512MB (64Mx64) SGU06464C1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 4 64Mx16 1 1GB (128Mx64) SGU12864D1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 8 128Mx8 1 2GB (256Mx64) SGU25664E1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 16 128Mx8 2 DDR3 SDRAM UDIMM w/ ECC (240 pin) 512MB (64Mx72) SGU06472H1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 5 64Mx16 1 1GB (128Mx72) SGU12872F1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 9 128Mx8 1 2GB (256Mx72) SGU25672G1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 18 128Mx8 2 DDR3 SDRAM -

Dynamic Random Access Memory Topics

Dynamic Random Access Memory Topics Simple DRAM Fast Page Mode (FPM) DRAM Extended Data Out (EDO) DRAM Burst EDO (BEDO) DRAM Synchronous DRAM (SDRAM) Rambus DRAM (RDRAM) Double Data Rate (DDR) SDRAM One capacitor and transistor of power, the discharge y Leaks a smallcapacitor amount slowly Simplicit refresh Requires top sk de in ed Us le ti la o v General DRAM Formats • DRAM is produced as integrated circuits (ICs) bonded and mounted into plastic packages with metal pins for connection to control signals and buses • In early use individual DRAM ICs were usually either installed directly to the motherboard or on ISA expansion cards • later they were assembled into multi-chip plug-in modules (DIMMs, SIMMs, etc.) General DRAM formats • Some Standard Module Type: • DRAM chips (Integrated Circuit or IC) • Dual in-line Package (DIP) • DRAM (memory) modules • Single in-line in Package(SIPP) • Single In-line Memory Module (SIMM) • Dual In-line Memory Module (DIMM) • Rambus In-line Memory Module (RIMM) • Small outline DIMM (SO-DIMM) Dual in-line Package (DIP) • is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins • 14 pins Single in-line in Package (SIPP) • It consisted of a small printed circuit board upon which were mounted a number of memory chips. • It had 30 pins along one edge which mated with matching holes in the motherboard of the computer. Single In-line Memory Module (SIMM) SIMM can be a 30 pin memory module or a 72 pin Dual In-line Memory Module (DIMM) Two types of DIMMs: a 168-pin SDRAM module and a 184-pin DDR SDRAM module. -

SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer

Primer SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer Table of Contents Introduction . 3 - 4 DRAM Trends . .3 DRAM . 4 - 6 SDRAM . 6 - 9 DDR SDRAM . .6 DDR2 SDRAM . .7 DDR3 SDRAM . .8 DDR4 SDRAM . .9 GDDR and LPDDR . .9 DIMMs . 9 - 13 DIMM Physical Size . 9 DIMM Data Width . 9 DIMM Rank . .10 DIMM Memory Size & Speed . .10 DIMM Architecture . .10 Serial Presence Detect . .12 Memory System Design . .13 - 15 Design Simulation . .13 Design Verification . .13 Verification Strategy . .13 SDRAM Verification . .14 Glossary . .16 - 19 2 www.tektronix.com/memory SDRAM Memory Systems: Architecture Overview and Design Verification Primer Introduction Memory needs to be compatible with a wide variety of memory controller hubs used by the computer DRAM (Dynamic Random Access Memory) is attractive to manufacturers. designers because it provides a broad range of performance Memory needs to work when a mixture of different and is used in a wide variety of memory system designs for manufacturer’s memories is used in the same memory computers and embedded systems. This DRAM memory system of the computer. primer provides an overview of DRAM concepts, presents potential future DRAM developments and offers an overview Open memory standards are useful in helping to ensure for memory design improvement through verification. memory compatibility. DRAM Trends On the other hand, embedded systems typically use a fixed There is a continual demand for computer memories to be memory configuration, meaning the user does not modify larger, faster, lower powered and physically smaller. These the memory system after purchasing the product. -

Datakommunikasjon Og Maskinvare

Institutt for økonomi og IT Datakommunikasjon og maskinvare Kompendium til emnet 6105N Windows Server og datanett Jon Kvisli Universitetet i Sørøst-Norge, Januar 2020 © Jon Kvisli, 2020 Windows® og Windows Server® er varemerker registrert av Microsoft Corporation. Det må ikke kopieres fra dette heftet ut over det som er tillatt etter bestemmelser i «Lov om opphavsrett til åndsverk», og avtaler om kopiering inngått med Kopinor. Forsidebilde: Colourbox Sats: Jon Kvisli 2 Innhold 1. GRUNNPRINSIPPER I DATAKOMMUNIKASJON .......................................................................... 4 1.1. Punkt-til-punkt kommunikasjon ................................................................................................................ 4 1.2. Kommunikasjonsbusser ............................................................................................................................. 8 1.3. Signalering ................................................................................................................................................ 10 1.4. Dempning, støy og forvrengning.............................................................................................................. 14 1.5. Digitale og analoge signaler ..................................................................................................................... 16 1.6. Noen kommunikasjonsstandarder ........................................................................................................... 17 1.7. Sammendrag ........................................................................................................................................... -

Advances in Computer Random Access Memory Himadri Barman

Advances in Computer Random Access Memory Himadri Barman Introduction Random‐access memory (RAM) is a form of computer data storage and is typically associated with the main memory of a computer. RAM in popular context is volatile but as would be seen later on in the discussion, they need not be. Because of increasing complexity of the computer, emergence of portable devices, etc., RAM technology is undergoing tremendous advances. This report looks at some recent advances in RAM technology, including that of the conventional Dynamic Random Access Memory in the form of DDR 3 (Double Data Rate Type 3). We also look at the emerging area of Non‐volatile random‐access memory (NVRAM). NVRAM is random‐access memory that retains its information when power is turned off, which is described technically as being non‐volatile. This is in contrast to the most common forms of random access memory today, dynamic random‐access memory (DRAM) and static random‐access memory (SRAM), which both require continual power in order to maintain their data. NVRAM is a subgroup of the more general class of non‐volatile memory types, the difference being that NVRAM devices offer random access, unlike hard disks. Double Data Rate 3 Synchronous Dynamic Random Access Memory DDR 3, the third‐generation of DDR SDRAM technology, is a modern kind of DRAM with a high bandwidth interface. It is one of several variants of DRAM and associated interface techniques used since the early 1970s. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of RAM due to different signaling voltages, timings, and other factors. -

High Bandwidth Memory Interface Design Based on DDR3 SDRAM and FPGA

High bandwidth memory interface design based on DDR3 SDRAM and FPGA Baopo Wang1,2, Jinsong Du1,3, Xin Bi1,3*and Xing Tian1,3 1Shenyang Institute of Automation, Chinese Academy of Sciences, China 2University of Chinese Academy of Sciences, China 3Key Laboratory of Liaoning Province on Radar System and Application, China E-mail: [email protected] *Corresponding author: Xin Bi; E-mail: [email protected] Abstract—This work presented the high bandwidth memory addressing. The address bus consists of A[14:0] and BA[2:0], interface design based on DDR3 SDRAM using external memory while the data bus including DQ[31:0] and the source IP core provided by FPGA devices. The structure and synchronous clock DQS[3:0]. configuration of IP core was introduced and the simulation on soft and hard IP was carried out with the access controller designed. The maximum transmission bandwidth of the memory interface based on the soft and hard IP respectively reached 19.2Gbps and 25.6Gbps. Finally, the reliability of the interface controller was verified by downloading the program to the DAQ board and observing the internal signals. Keywords-Memory interface; DDR3; FPGA; IP; High Figure 1. The schematic diagram of the DAQ board and the storage module bandwidth III. MEMORY INTERFACE DESIGN AND SIMULATION I. INTRODUCTION Memory performance has become a key factor in A. Introduction and configuration of the IP core. improving the overall performance of the real time system[1], The devices of Cyclone V series provide available hard or requirements on the data processing, the stability and the power soft IP for external memory interface including DDR3. -

SMBIOS) Reference 6 Specification

1 2 Document Identifier: DSP0134 3 Date: 2018-04-26 4 Version: 3.2.0 5 System Management BIOS (SMBIOS) Reference 6 Specification 7 Supersedes: 3.1.1 8 Document Class: Normative 9 Document Status: Published 10 Document Language: en-US 11 System Management BIOS (SMBIOS) Reference Specification DSP0134 12 Copyright Notice 13 Copyright © 2000, 2002, 2004–2016 Distributed Management Task Force, Inc. (DMTF). All rights 14 reserved. 15 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 16 management and interoperability. Members and non-members may reproduce DMTF specifications and 17 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 18 time, the particular version and release date should always be noted. 19 Implementation of certain elements of this standard or proposed standard may be subject to third party 20 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 21 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 22 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 23 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 24 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 25 disclose, or identify any such third party patent rights, or for such party’s reliance on the standard or 26 incorporation thereof in its product, protocols or testing procedures. -

Overview of Packaging Drams and Use of RDL

Overview of packaging DRAMs and use of RDL ECG 721 – Memory Circuit Design Kostas Moutafis April 2017 A die photograph of the Micron Technology MT4C1024 DRAM integrated circuit. It has a capacity of 1 megabit, equivalent of 2^20 bits or 128 kB [1] What is Dynamic Random‐Access Memory (DRAM) Random‐Access… because data can be accessed in the same amount of time irrespective of their physical location Dynamic… because data have to be refreshed periodically DRAM stores each bit of data in a storage cell consisting of a capacitor and a transistor (1T1C DRAM memory cell) The DRAM cell (bottom left) has remained relatively the same, but the manufacturing technology has kept it competitive for decades [2] Where is it used? Volatile memory Fast but not too expensive memory Billions of Gbits Bandwidth (MB/s) Cost vs speed in memory hierarchy [4] Growing and Diversifying DRAM Demand [3] DRAM types Asynchronous DRAM Synchronous DRAM (SDRAM) Single Data Rate (SDR) Double Data Rate (DDR) Samsung has begun mass production of 10‐nm class, 8‐Gbit DDR4 DRAM chips, which support speeds up to 3.2GT/s (equal to 51.2GB/s) [5] DDR4 high speed performance compared with DDR3 and DDR2 [5] DRAM modules Single Inline Memory Module (SIMM) early 80s to late 90s 32‐bit data path (72 pins) Crucial 16GB Kit (8GBx2) DDR4 2133 MT/s UDIMM 288‐Pin Memory (Amazon.com ‐ $102.99) Small out line DIMM (SoDIMM ) 260‐pins used for DDR4 SDRAM From top to bottom: SIMM (30‐pin), SIMM (72‐pin) [5] Dual Inline Memory Module (DIMM) contacts on both sides 64‐bit data path 288‐pins used for DDR4 SDRAM Crucial 16GB Kit (8GBx2) DDR3/DDR3L 1866 MT/s SODIMM 204‐Pin Memory (Amazon.com ‐ $89.99) Why packaging? Protection Physical damage Environmental damage Electrical connections Redbdistributes I /O Heat dissipation TfiTransfer via convec tion DRAM package evolution [6] Increased surface area DRAM packaging in time Samsung: World’s fastest (Jan.