Low-Power, High-Bandwidth, and Ultra-Small Memory Module Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Performance Impact of Memory Channels on Sparse and Irregular Algorithms

Performance Impact of Memory Channels on Sparse and Irregular Algorithms Oded Green1,2, James Fox2, Jeffrey Young2, Jun Shirako2, and David Bader3 1NVIDIA Corporation — 2Georgia Institute of Technology — 3New Jersey Institute of Technology Abstract— Graph processing is typically considered to be a Graph algorithms are typically latency-bound if there is memory-bound rather than compute-bound problem. One com- not enough parallelism to saturate the memory subsystem. mon line of thought is that more available memory bandwidth However, the growth in parallelism for shared-memory corresponds to better graph processing performance. However, in this work we demonstrate that the key factor in the utilization systems brings into question whether graph algorithms are of the memory system for graph algorithms is not necessarily still primarily latency-bound. Getting peak or near-peak the raw bandwidth or even the latency of memory requests. bandwidth of current memory subsystems requires highly Instead, we show that performance is proportional to the parallel applications as well as good spatial and temporal number of memory channels available to handle small data memory reuse. The lack of spatial locality in sparse and transfers with limited spatial locality. Using several widely used graph frameworks, including irregular algorithms means that prefetched cache lines have Gunrock (on the GPU) and GAPBS & Ligra (for CPUs), poor data reuse and that the effective bandwidth is fairly low. we evaluate key graph analytics kernels using two unique The introduction of high-bandwidth memories like HBM and memory hierarchies, DDR-based and HBM/MCDRAM. Our HMC have not yet closed this inefficiency gap for latency- results show that the differences in the peak bandwidths sensitive accesses [19]. -

Different Types of RAM RAM RAM Stands for Random Access Memory. It Is Place Where Computer Stores Its Operating System. Applicat

Different types of RAM RAM RAM stands for Random Access Memory. It is place where computer stores its Operating System. Application Program and current data. when you refer to computer memory they mostly it mean RAM. The two main forms of modern RAM are Static RAM (SRAM) and Dynamic RAM (DRAM). DRAM memories (Dynamic Random Access Module), which are inexpensive . They are used essentially for the computer's main memory SRAM memories(Static Random Access Module), which are fast and costly. SRAM memories are used in particular for the processer's cache memory. Early memories existed in the form of chips called DIP (Dual Inline Package). Nowaday's memories generally exist in the form of modules, which are cards that can be plugged into connectors for this purpose. They are generally three types of RAM module they are 1. DIP 2. SIMM 3. DIMM 4. SDRAM 1. DIP(Dual In Line Package) Older computer systems used DIP memory directely, either soldering it to the motherboard or placing it in sockets that had been soldered to the motherboard. Most memory chips are packaged into small plastic or ceramic packages called dual inline packages or DIPs . A DIP is a rectangular package with rows of pins running along its two longer edges. These are the small black boxes you see on SIMMs, DIMMs or other larger packaging styles. However , this arrangment caused many problems. Chips inserted into sockets suffered reliability problems as the chips would (over time) tend to work their way out of the sockets. 2. SIMM A SIMM, or single in-line memory module, is a type of memory module containing random access memory used in computers from the early 1980s to the late 1990s . -

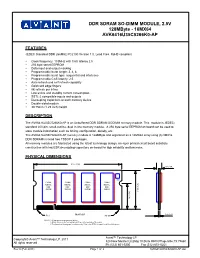

DDR SDRAM SO-DIMM MODULE, 2.5V 128Mbyte - 16MX64 AVK6416U35C5266K0-AP

DDR SDRAM SO-DIMM MODULE, 2.5V 128MByte - 16MX64 AVK6416U35C5266K0-AP FEATURES JEDEC Standard DDR 266MHz PC2100 Version 1.0, Lead Free, RoHS compliant Clock frequency: 133MHz with CAS latency 2.5 256 byte serial EEPROM Data input and output masking Programmable burst length: 2, 4, 8 Programmable burst type: sequential and interleave Programmable CAS latency: 2.5 Auto refresh and self refresh capability Gold card edge fingers 8K refresh per 64ms Low active and standby current consumption SSTL-2 compatible inputs and outputs Decoupling capacitors at each memory device Double-sided module 30.75mm (1.25 inch) height DESCRIPTION The AVK6416U35C5266K0-AP is an Unbuffered DDR SDRAM SODIMM memory module. This module is JEDEC- standard 200-pin, small-outline, dual in-line memory module. A 256 byte serial EEPROM on board can be used to store module information such as timing, configuration, density, etc. The AVK6416U35C5266K0-AP memory module is 128MByte and organized as a 16MX64 array using (8) 8MX16 DDR SDRAMs in lead free TSSOP II packages. All memory modules are fabricated using the latest technology design, six-layer printed circuit board substrate construction with low ESR decoupling capacitors on-board for high reliability and low noise. PHYSICAL DIMENSIONS 67.60 (2.66) 3.50 (0.14) SPD 128Mbit 128Mbit 128Mbit 128Mbit ) 5 8MbX16 8MbX16 8MbX16 8MbX16 2 . 1 ( DDR DDR DDR DDR 5 7 SDRAM SDRAM SDRAM SDRAM . 1 ) 3 7 8 7 . 0 ( 0 2 FRONT SIDE 1.00 (0.04) Pin 1 Pin 199 NOTES: 1- All dimensions are in milimeters (inches) 2- All blue ICs are on the front, and all red ICs are on the back side of the module. -

Case Study on Integrated Architecture for In-Memory and In-Storage Computing

electronics Article Case Study on Integrated Architecture for In-Memory and In-Storage Computing Manho Kim 1, Sung-Ho Kim 1, Hyuk-Jae Lee 1 and Chae-Eun Rhee 2,* 1 Department of Electrical Engineering, Seoul National University, Seoul 08826, Korea; [email protected] (M.K.); [email protected] (S.-H.K.); [email protected] (H.-J.L.) 2 Department of Information and Communication Engineering, Inha University, Incheon 22212, Korea * Correspondence: [email protected]; Tel.: +82-32-860-7429 Abstract: Since the advent of computers, computing performance has been steadily increasing. Moreover, recent technologies are mostly based on massive data, and the development of artificial intelligence is accelerating it. Accordingly, various studies are being conducted to increase the performance and computing and data access, together reducing energy consumption. In-memory computing (IMC) and in-storage computing (ISC) are currently the most actively studied architectures to deal with the challenges of recent technologies. Since IMC performs operations in memory, there is a chance to overcome the memory bandwidth limit. ISC can reduce energy by using a low power processor inside storage without an expensive IO interface. To integrate the host CPU, IMC and ISC harmoniously, appropriate workload allocation that reflects the characteristics of the target application is required. In this paper, the energy and processing speed are evaluated according to the workload allocation and system conditions. The proof-of-concept prototyping system is implemented for the integrated architecture. The simulation results show that IMC improves the performance by 4.4 times and reduces total energy by 4.6 times over the baseline host CPU. -

ECE 571 – Advanced Microprocessor-Based Design Lecture 17

ECE 571 { Advanced Microprocessor-Based Design Lecture 17 Vince Weaver http://web.eece.maine.edu/~vweaver [email protected] 3 April 2018 Announcements • HW8 is readings 1 More DRAM 2 ECC Memory • There's debate about how many errors can happen, anywhere from 10−10 error/bit*h (roughly one bit error per hour per gigabyte of memory) to 10−17 error/bit*h (roughly one bit error per millennium per gigabyte of memory • Google did a study and they found more toward the high end • Would you notice if you had a bit flipped? • Scrubbing { only notice a flip once you read out a value 3 Registered Memory • Registered vs Unregistered • Registered has a buffer on board. More expensive but can have more DIMMs on a channel • Registered may be slower (if it buffers for a cycle) • RDIMM/UDIMM 4 Bandwidth/Latency Issues • Truly random access? No, burst speed fast, random speed not. • Is that a problem? Mostly filling cache lines? 5 Memory Controller • Can we have full random access to memory? Why not just pass on CPU mem requests unchanged? • What might have higher priority? • Why might re-ordering the accesses help performance (back and forth between two pages) 6 Reducing Refresh • DRAM Refresh Mechanisms, Penalties, and Trade-Offs by Bhati et al. • Refresh hurts performance: ◦ Memory controller stalls access to memory being refreshed ◦ Refresh takes energy (read/write) On 32Gb device, up to 20% of energy consumption and 30% of performance 7 Async vs Sync Refresh • Traditional refresh rates ◦ Async Standard (15.6us) ◦ Async Extended (125us) ◦ SDRAM - -

Adm-Pcie-9H3 V1.5

ADM-PCIE-9H3 10th September 2019 Datasheet Revision: 1.5 AD01365 Applications Board Features • High-Performance Network Accelerator • 1x OpenCAPI Interface • Data CenterData Processor • 1x QSFP-DD Cages • High Performance Computing (HPC) • Shrouded heatsink with passive and fan cooling • System Modelling options • Market Analysis FPGA Features • 2x 4GB HBM Gen2 memory (32 AXI Ports provide 460GB/s Access Bandwidth) • 3x 100G Ethernet MACs (incl. KR4 RS-FEC) • 3x 150G Interlaken cores • 2x PCI Express x16 Gen3 / x8 Gen4 cores Summary The ADM-PCIE-9H3 is a high-performance FPGA processing card intended for data center applications using Virtex UltraScale+ High Bandwidth Memory FPGAs from Xilinx. The ADM-PCIE-9H3 utilises the Xilinx Virtex Ultrascale Plus FPGA family that includes on substrate High Bandwidth Memory (HBM Gen2). This provides exceptional memory Read/Write performance while reducing the overall power consumption of the board by negating the need for external SDRAM devices. There are also a number of high speed interface options available including 100G Ethernet MACs and OpenCAPI connectivity, to make the most of these interfaces the ADM-PCIE-9H3 is fitted with a QSFP-DD Cage (8x28Gbps lanes) and one OpenCAPI interface for ultra low latency communications. Target Device Host Interface Xilinx Virtex UltraScale Plus: XCVU33P-2E 1x PCI Express Gen3 x16 or 1x/2x* PCI Express (FSVH2104) Gen4 x8 or OpenCAPI LUTs = 440k(872k) Board Format FFs = 879k(1743k) DSPs = 2880(5952) 1/2 Length low profile x16 PCIe form Factor BRAM = 23.6Mb(47.3Mb) WxHxD = 19.7mm x 80.1mm x 181.5mm URAM = 90.0Mb(180.0Mb) Weight = TBCg 2x 4GB HBM Gen2 memory (32 AXI Ports Communications Interfaces provide 460GB/s Access Bandwidth) 1x QSFP-DD 8x28Gbps - 10/25/40/100G 3x 100G Ethernet MACs (incl. -

High Bandwidth Memory for Graphics Applications Contents

High Bandwidth Memory for Graphics Applications Contents • Differences in Requirements: System Memory vs. Graphics Memory • Timeline of Graphics Memory Standards • GDDR2 • GDDR3 • GDDR4 • GDDR5 SGRAM • Problems with GDDR • Solution ‐ Introduction to HBM • Performance comparisons with GDDR5 • Benchmarks • Hybrid Memory Cube Differences in Requirements System Memory Graphics Memory • Optimized for low latency • Optimized for high bandwidth • Short burst vector loads • Long burst vector loads • Equal read/write latency ratio • Low read/write latency ratio • Very general solutions and designs • Designs can be very haphazard Brief History of Graphics Memory Types • Ancient History: VRAM, WRAM, MDRAM, SGRAM • Bridge to modern times: GDDR2 • The first modern standard: GDDR4 • Rapidly outclassed: GDDR4 • Current state: GDDR5 GDDR2 • First implemented with Nvidia GeForce FX 5800 (2003) • Midway point between DDR and ‘true’ DDR2 • Stepping stone towards DDR‐based graphics memory • Second‐generation GDDR2 based on DDR2 GDDR3 • Designed by ATI Technologies , first used by Nvidia GeForce FX 5700 (2004) • Based off of the same technological base as DDR2 • Lower heat and power consumption • Uses internal terminators and a 32‐bit bus GDDR4 • Based on DDR3, designed by Samsung from 2005‐2007 • Introduced Data Bus Inversion (DBI) • Doubled prefetch size to 8n • Used on ATI Radeon 2xxx and 3xxx, never became commercially viable GDDR5 SGRAM • Based on DDR3 SDRAM memory • Inherits benefits of GDDR4 • First used in AMD Radeon HD 4870 video cards (2008) • Current -

Architectures for High Performance Computing and Data Systems Using Byte-Addressable Persistent Memory

Architectures for High Performance Computing and Data Systems using Byte-Addressable Persistent Memory Adrian Jackson∗, Mark Parsonsy, Michele` Weilandz EPCC, The University of Edinburgh Edinburgh, United Kingdom ∗[email protected], [email protected], [email protected] Bernhard Homolle¨ x SVA System Vertrieb Alexander GmbH Paderborn, Germany x [email protected] Abstract—Non-volatile, byte addressable, memory technology example of such hardware, used for data storage. More re- with performance close to main memory promises to revolutionise cently, flash memory has been used for high performance I/O computing systems in the near future. Such memory technology in the form of Solid State Disk (SSD) drives, providing higher provides the potential for extremely large memory regions (i.e. > 3TB per server), very high performance I/O, and new ways bandwidth and lower latency than traditional Hard Disk Drives of storing and sharing data for applications and workflows. (HDD). This paper outlines an architecture that has been designed to Whilst flash memory can provide fast input/output (I/O) exploit such memory for High Performance Computing and High performance for computer systems, there are some draw backs. Performance Data Analytics systems, along with descriptions of It has limited endurance when compare to HDD technology, how applications could benefit from such hardware. Index Terms—Non-volatile memory, persistent memory, stor- restricted by the number of modifications a memory cell age class memory, system architecture, systemware, NVRAM, can undertake and thus the effective lifetime of the flash SCM, B-APM storage [29]. It is often also more expensive than other storage technologies. -

Dynamic Random Access Memory Topics

Dynamic Random Access Memory Topics Simple DRAM Fast Page Mode (FPM) DRAM Extended Data Out (EDO) DRAM Burst EDO (BEDO) DRAM Synchronous DRAM (SDRAM) Rambus DRAM (RDRAM) Double Data Rate (DDR) SDRAM One capacitor and transistor of power, the discharge y Leaks a smallcapacitor amount slowly Simplicit refresh Requires top sk de in ed Us le ti la o v General DRAM Formats • DRAM is produced as integrated circuits (ICs) bonded and mounted into plastic packages with metal pins for connection to control signals and buses • In early use individual DRAM ICs were usually either installed directly to the motherboard or on ISA expansion cards • later they were assembled into multi-chip plug-in modules (DIMMs, SIMMs, etc.) General DRAM formats • Some Standard Module Type: • DRAM chips (Integrated Circuit or IC) • Dual in-line Package (DIP) • DRAM (memory) modules • Single in-line in Package(SIPP) • Single In-line Memory Module (SIMM) • Dual In-line Memory Module (DIMM) • Rambus In-line Memory Module (RIMM) • Small outline DIMM (SO-DIMM) Dual in-line Package (DIP) • is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins • 14 pins Single in-line in Package (SIPP) • It consisted of a small printed circuit board upon which were mounted a number of memory chips. • It had 30 pins along one edge which mated with matching holes in the motherboard of the computer. Single In-line Memory Module (SIMM) SIMM can be a 30 pin memory module or a 72 pin Dual In-line Memory Module (DIMM) Two types of DIMMs: a 168-pin SDRAM module and a 184-pin DDR SDRAM module. -

How to Manage High-Bandwidth Memory Automatically

How to Manage High-Bandwidth Memory Automatically Rathish Das Kunal Agrawal Michael A. Bender Stony Brook University Washington University in St. Louis Stony Brook University [email protected] [email protected] [email protected] Jonathan Berry Benjamin Moseley Cynthia A. Phillips Sandia National Laboratories Carnegie Mellon University Sandia National Laboratories [email protected] [email protected] [email protected] ABSTRACT paging algorithms; Parallel algorithms; Shared memory al- This paper develops an algorithmic foundation for automated man- gorithms; • Computer systems organization ! Parallel ar- agement of the multilevel-memory systems common to new super- chitectures; Multicore architectures. computers. In particular, the High-Bandwidth Memory (HBM) of these systems has a similar latency to that of DRAM and a smaller KEYWORDS capacity, but it has much larger bandwidth. Systems equipped with Paging, High-bandwidth memory, Scheduling, Multicore paging, HBM do not fit in classic memory-hierarchy models due to HBM’s Online algorithms, Approximation algorithms. atypical characteristics. ACM Reference Format: Unlike caches, which are generally managed automatically by Rathish Das, Kunal Agrawal, Michael A. Bender, Jonathan Berry, Benjamin the hardware, programmers of some current HBM-equipped super- Moseley, and Cynthia A. Phillips. 2020. How to Manage High-Bandwidth computers can choose to explicitly manage HBM themselves. This Memory Automatically. In Proceedings of the 32nd ACM Symposium on process is problem specific and resource intensive. Vendors offer Parallelism in Algorithms and Architectures (SPAA ’20), July 15–17, 2020, this option because there is no consensus on how to automatically Virtual Event, USA. ACM, New York, NY, USA, 13 pages. https://doi.org/10. -

SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer

Primer SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer Table of Contents Introduction . 3 - 4 DRAM Trends . .3 DRAM . 4 - 6 SDRAM . 6 - 9 DDR SDRAM . .6 DDR2 SDRAM . .7 DDR3 SDRAM . .8 DDR4 SDRAM . .9 GDDR and LPDDR . .9 DIMMs . 9 - 13 DIMM Physical Size . 9 DIMM Data Width . 9 DIMM Rank . .10 DIMM Memory Size & Speed . .10 DIMM Architecture . .10 Serial Presence Detect . .12 Memory System Design . .13 - 15 Design Simulation . .13 Design Verification . .13 Verification Strategy . .13 SDRAM Verification . .14 Glossary . .16 - 19 2 www.tektronix.com/memory SDRAM Memory Systems: Architecture Overview and Design Verification Primer Introduction Memory needs to be compatible with a wide variety of memory controller hubs used by the computer DRAM (Dynamic Random Access Memory) is attractive to manufacturers. designers because it provides a broad range of performance Memory needs to work when a mixture of different and is used in a wide variety of memory system designs for manufacturer’s memories is used in the same memory computers and embedded systems. This DRAM memory system of the computer. primer provides an overview of DRAM concepts, presents potential future DRAM developments and offers an overview Open memory standards are useful in helping to ensure for memory design improvement through verification. memory compatibility. DRAM Trends On the other hand, embedded systems typically use a fixed There is a continual demand for computer memories to be memory configuration, meaning the user does not modify larger, faster, lower powered and physically smaller. These the memory system after purchasing the product. -

Exploring New Features of High- Bandwidth Memory for Gpus

This article has been accepted and published on J-STAGE in advance of copyediting. Content is final as presented. IEICE Electronics Express, Vol.*, No.*, 1{11 Exploring new features of high- bandwidth memory for GPUs Bingchao Li1, Choungki Song2, Jizeng Wei1, Jung Ho Ahn3a) and Nam Sung Kim4b) 1 School of Computer Science and Technology, Tianjin University 2 Department of Electrical and Computer Engineering, University of Wisconsin- Madison 3 Graduate School of Convergence Science and Technology, Seoul National University 4 Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign a) [email protected] b) [email protected] Abstract: Due to the off-chip I/O pin and power constraints of GDDR5, HBM has been proposed to provide higher bandwidth and lower power consumption for GPUs. In this paper, we first provide de- tailed comparison between HBM and GDDR5 and expose two unique features of HBM: dual-command and pseudo channel mode. Second, we analyze the effectiveness of these two features and show that neither notably contributes to performance. However, by combining pseudo channel mode with cache architecture supporting fine-grained cache- line management such as Amoeba cache, we achieve high efficiency for applications with irregular memory requests. Our experiment demon- strates that compared with Amoeba caches with legacy mode, Amoeba cache with pseudo channel mode improves GPU performance by 25% and reduces HBM energy consumption by 15%. Keywords: GPU, HBM, DRAM, Amoeba cache, Energy Classification: Integrated circuits References [1] JEDEC: Graphic Double Data Rate 5 (GDDR5) Specification (2009) https://www.jedec.org/standards- documents/results/taxonomy%3A4229.