Memory Systems Cache, DRAM, Disk

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Fully-Buffered DIMM Memory Architectures: Understanding Mechanisms, Overheads and Scaling

Fully-Buffered DIMM Memory Architectures: Understanding Mechanisms, Overheads and Scaling Brinda Ganesh†, Aamer Jaleel‡, David Wang†, and Bruce Jacob† †University of Maryland, College Park, MD ‡VSSAD, Intel Corporation, Hudson, MA {brinda, blj}@eng.umd.edu Abstract Consequently the maximum number of DIMMs per channel in Performance gains in memory have traditionally been successive DRAM generations has been decreasing. SDRAM obtained by increasing memory bus widths and speeds. The channels have supported up to 8 DIMMs of memory, some diminishing returns of such techniques have led to the types of DDR channels support only 4 DIMMs, DDR2 channels proposal of an alternate architecture, the Fully-Buffered have but 2 DIMMs, and DDR3 channels are expected to support DIMM. This new standard replaces the conventional only a single DIMM. In addition the serpentine routing required for electrical path-length matching of the data wires becomes memory bus with a narrow, high-speed interface between the challenging as bus widths increase. For the bus widths of today, memory controller and the DIMMs. This paper examines the motherboard area occupied by a single channel is signifi- how traditional DDRx based memory controller policies for cant, complicating the task of adding capacity by increasing the scheduling and row buffer management perform on a Fully- number of channels. To address these scalability issues, an alter- Buffered DIMM memory architecture. The split-bus nate DRAM technology, the Fully Buffered Dual Inline Mem- architecture used by FBDIMM systems results in an average ory Module (FBDIMM) [2] has been introduced. improvement of 7% in latency and 10% in bandwidth at The FBDIMM memory architecture replaces the shared par- higher utilizations. -

Different Types of RAM RAM RAM Stands for Random Access Memory. It Is Place Where Computer Stores Its Operating System. Applicat

Different types of RAM RAM RAM stands for Random Access Memory. It is place where computer stores its Operating System. Application Program and current data. when you refer to computer memory they mostly it mean RAM. The two main forms of modern RAM are Static RAM (SRAM) and Dynamic RAM (DRAM). DRAM memories (Dynamic Random Access Module), which are inexpensive . They are used essentially for the computer's main memory SRAM memories(Static Random Access Module), which are fast and costly. SRAM memories are used in particular for the processer's cache memory. Early memories existed in the form of chips called DIP (Dual Inline Package). Nowaday's memories generally exist in the form of modules, which are cards that can be plugged into connectors for this purpose. They are generally three types of RAM module they are 1. DIP 2. SIMM 3. DIMM 4. SDRAM 1. DIP(Dual In Line Package) Older computer systems used DIP memory directely, either soldering it to the motherboard or placing it in sockets that had been soldered to the motherboard. Most memory chips are packaged into small plastic or ceramic packages called dual inline packages or DIPs . A DIP is a rectangular package with rows of pins running along its two longer edges. These are the small black boxes you see on SIMMs, DIMMs or other larger packaging styles. However , this arrangment caused many problems. Chips inserted into sockets suffered reliability problems as the chips would (over time) tend to work their way out of the sockets. 2. SIMM A SIMM, or single in-line memory module, is a type of memory module containing random access memory used in computers from the early 1980s to the late 1990s . -

Architectural Techniques to Enhance DRAM Scaling

Architectural Techniques to Enhance DRAM Scaling Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Yoongu Kim B.S., Electrical Engineering, Seoul National University Carnegie Mellon University Pittsburgh, PA June, 2015 Abstract For decades, main memory has enjoyed the continuous scaling of its physical substrate: DRAM (Dynamic Random Access Memory). But now, DRAM scaling has reached a thresh- old where DRAM cells cannot be made smaller without jeopardizing their robustness. This thesis identifies two specific challenges to DRAM scaling, and presents architectural tech- niques to overcome them. First, DRAM cells are becoming less reliable. As DRAM process technology scales down to smaller dimensions, it is more likely for DRAM cells to electrically interfere with each other’s operation. We confirm this by exposing the vulnerability of the latest DRAM chips to a reliability problem called disturbance errors. By reading repeatedly from the same cell in DRAM, we show that it is possible to corrupt the data stored in nearby cells. We demonstrate this phenomenon on Intel and AMD systems using a malicious program that generates many DRAM accesses. We provide an extensive characterization of the errors, as well as their behavior, using a custom-built testing platform. After examining various potential ways of addressing the problem, we propose a low-overhead solution that effec- tively prevents the errors through a collaborative effort between the DRAM chips and the DRAM controller. Second, DRAM cells are becoming slower due to worsening variation in DRAM process technology. To alleviate the latency bottleneck, we propose to unlock fine-grained paral- lelism within a DRAM chip so that many accesses can be served at the same time. -

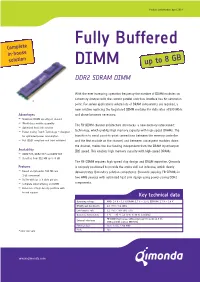

Fully Buffered Dimms for Server

07137_Fully_Buffered_DIMM.qxd 22.03.2007 12:08 Uhr Seite 1 Product Information April 2007 Fully Buffered Complete in-house solution DIMM up to 8 GB DDR2 SDRAM DIMM With the ever increasing operation frequency the number of DIMM modules on a memory channel with the current parallel stub-bus interface has hit saturation * point. For server applications where lots of DRAM components are required, a new solution replacing the Registered DIMM modules for data rates of 533 Mb/s Advantages and above becomes necessary. s Maximum DRAM density per channel s World-class module assembly The FB-DIMM channel architecture introduces a new memory interconnect s Optimized heat sink solution s Power Saving Trench Technology – designed technology, which enables high memory capacity with high-speed DRAMs. The for optimized power consumption transition to serial point-to-point connections between the memory controller s Full JEDEC compliant and Intel validated and the first module on the channel, and between subsequent modules down the channel, makes the bus-loading independent from the DRAM input/output Availability (IO) speed. This enables high memory capacity with high-speed DRAMs. s DDR2-533, DDR2-667 and DDR2-800 s Densities from 512 MB up to 8 GB The FB-DIMM requires high-speed chip design and DRAM expertise. Qimonda Features is uniquely positioned to provide the entire skill set in-house, which clearly s Based on Qimonda’s 512 Mb and demonstrates Qimonda’s solution competence. Qimonda supplies FB-DIMMs in 1 Gb component two AMB sources with optimized heat sink design using power-saving DDR2 s Buffer with up to 6 Gb/s per pin s Complete data buffering on DIMM components. -

![Zynq-7000 All Programmable Soc and 7 Series Devices Memory Interface Solutions User Guide (UG586) [Ref 2]](https://docslib.b-cdn.net/cover/3157/zynq-7000-all-programmable-soc-and-7-series-devices-memory-interface-solutions-user-guide-ug586-ref-2-573157.webp)

Zynq-7000 All Programmable Soc and 7 Series Devices Memory Interface Solutions User Guide (UG586) [Ref 2]

Zynq-7000 AP SoC and 7 Series Devices Memory Interface Solutions (v4.1) DS176 April 4, 2018 Advance Product Specification • I/O Power Reduction option reduces average I/O Introduction power by automatically disabling DQ/DQS IBUFs and The Xilinx® Zynq®-7000 All Programmable SoC and internal terminations during writes and periods of 7 series FPGAs memory interface solutions cores provide inactivity high-performance connections to DDR3 and DDR2 • Internal VREF support SDRAMs, QDR II+ SRAM, RLDRAM II/RLDRAM 3, and • LPDDR2 SDRAM. Multicontroller support for up to eight controllers • Two controller request processing modes: DDR3 and DDR2 SDRAMs o Normal: reorder requests to optimize system throughput and latency This section discusses the features, applications, and functional description of Xilinx 7 series FPGAs memory o Strict: memory requests are processed in the order interface solutions in DDR3 and DDR2 SDRAMs. These received solutions are available with an optional AXI4 slave interface. LogiCORE™ IP Facts Table Core Specifics DDR3 SDRAM Features Supported Zynq®-7000 All Programmable SoC (1) • Component support for interface widths up to 72 bits Device Family 7series(2) FPGAs • Supported DDR3 Component and DIMM, DDR2 Single and dual rank UDIMM, RDIMM, and SODIMM Memory support Component and DIMM, QDR II+, RLDRAM II, RLDRAM 3, and LPDDR2 SDRAM Components • DDR3 (1.5V) and DDR3L (1.35V) Resources See Table 1. • 1, 2, 4, and 8 Gb density device support Provided with Core • 8-bank support Documentation Product Specification • x8 and x16 device -

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441 Contract Institution: Georgia Institute of Technology Project Director: D. Scott Wills Project Report 12 September 2002 — 11 September 2004 This project explored the impact of developing memory technologies on future supercomputers. This activity included both a literature study (see attached whitepaper), plus a more practical exploration of potential memory interfacing techniques using the sponsor recommended HyperTransport interface. The report indicates trends that will affect interconnection network design in future supercomputers. Related publications during the contract period include: 1. P. G. Sassone and D. S. Wills, On the Scaling of the Atlas Chip-Scale Multiprocessor, to appear in IEEE Transaction on Computers. 2. P. G. Sassone and D. S. Wills, Dynamic Strands: Collapsing Speculative Dependence Chains for Reducing Pipeline Communication, to appear in IEEE/ACM International Symposium on Microarchitecture, Portland, OR, December 2004. 3. B. A. Small, A. Shacham, K. Bergman, K. Athikulwongse, C. Hawkins, and D. S. Wills, Emulation of Realistic Network Traffic Patterns on an Eight-Node Data Vortex Interconnection Network Subsystem, to appear in OSA Journal of Optical Networking. 4. P. G. Sassone and D. S. Wills, On the Extraction and Analysis of Prevalent Dataflow Patterns, to appear in The IEEE 7th Annual Workshop on Workload Characterization (WWC-7), 8 pages, Austin, TX, October 2004. 5. H. Kim, D. S. Wills, and L. M. Wills, Empirical Analysis of Operand Usage and Transport in Multimedia Applications, in Proceedings of the 4th IEEE International Workshop on System-on-Chip for Real-Time Applications(IWSOC'04), pages 168-171, Banff, Alberta, Canada, July 2004. -

SBA-7121M-T1 Blade Module User's Manual

SBA-7121M-T1 Blade Module User’s Manual Revison 1.0c SBA-7121M-T1 Blade Module User’s Manual The information in this User’s Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. Please Note: For the most up-to-date version of this manual, please see our web site at www.supermicro.com. Super Micro Computer, Inc. ("Supermicro") reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software and documentation, is the property of Supermicro and/or its licensors, and is supplied only under a license. Any use or reproduction of this product is not allowed, except as expressly permitted by the terms of said license. IN NO EVENT WILL SUPERMICRO BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, SUPERMICRO SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA. Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. -

Baby Steps to Our Future by Ron Fenley

Baby Steps to our Future by Ron Fenley Memory – Past, Present and Future, Part 2 of 3 Memories,… food for the EGO. Manifestation of memories into self-esteem, honor, dignity and many other traits characterize the individual. Obviously, memories are stored in the brain and scientist have identified, subdivided, labeled and compartmentalized the brain in many functional regions. Computer memory like human memory manifests it presents in different ways to perform a variety of functions; and computer memory has been divided into partitions, subsystems and specialization. Although the memory in today’s computers have not been programmed with personality traits, some PC systems do demonstrate personality disorders, particularly the one this article was written with. There is an abundance of terms that have been used to describe or label computer memory functions, features and attributes. Some terms apply to the hardware technology, some terms apply to the packing of these chips and others apply to the memory usage or memory systems within the computer. Collectively, all of these terms may be confusing and to help sort out and clarify these labels we will look at how these items have been applied to computer memory. To simplify this task, the effort will be divided into the following 5 areas: packing, parity & ECC, buffered/non-buffered, systems and labels. MEMORY PACKAGING Just as memory technology has evolved so has memory packaging. Shown below is a table of the different form factors (packaging) that has been used in memory deployment over -

Micron Technology Inc

MICRON TECHNOLOGY INC FORM 10-K (Annual Report) Filed 10/26/10 for the Period Ending 09/02/10 Address 8000 S FEDERAL WAY PO BOX 6 BOISE, ID 83716-9632 Telephone 2083684000 CIK 0000723125 Symbol MU SIC Code 3674 - Semiconductors and Related Devices Industry Semiconductors Sector Technology Fiscal Year 03/10 http://www.edgar-online.com © Copyright 2010, EDGAR Online, Inc. All Rights Reserved. Distribution and use of this document restricted under EDGAR Online, Inc. Terms of Use. UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended September 2, 2010 OR TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to Commission file number 1-10658 Micron Technology, Inc. (Exact name of registrant as specified in its charter) Delaware 75 -1618004 (State or other jurisdiction of (IRS Employer incorporation or organization) Identification No.) 8000 S. Federal Way, Boise, Idaho 83716 -9632 (Address of principal executive offices) (Zip Code) Registrant ’s telephone number, including area code (208) 368 -4000 Securities registered pursuant to Section 12(b) of the Act: Title of each class Name of each exchange on which registered Common Stock, par value $.10 per share NASDAQ Global Select Market Securities registered pursuant to Section 12(g) of the Act: None (Title of Class) Indicate by check mark if the registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. -

Architecture of an AHB Compliant SDRAM Memory Controller

International Journal of Innovations in Engineering and Technology (IJIET) Architecture of An AHB Compliant SDRAM Memory Controller S. Lakshma Reddy Metch student, Department of Electronics and Communication Engineering CVSR College of Engineering, Hyderabad, Andhra Pradesh, India A .Krishna Kumari Professor, Department of Electronics and Communication Engineering CVSR College of Engineering, Hyderabad, Andhra Pradesh, India Abstract- -- Microprocessor performance has improved rapidly these years. In contrast, memory latencies and bandwidths have improved little. The result is that the memory access time has been a bottleneck which limits the system performance. As the speed of fetching data from memories is not able to match up with speed of processors. So there is the need for a fast memory controller. The responsibility of the controller is to match the speeds of the processor on one side and memory on the other so that the communication can take place seamlessly. Here we have built a memory controller which is specifically targeted for SDRAM. Certain features were included in the design which could increase the overall efficiency of the controller, such as, searching the internal memory of the controller for the requested data for the most recently used data, instead of going to the Memory to fetch it. The memory controller is designed which compatible with Advanced High-performance Bus (AHB) which is a new generation of AMBA bus. The AHB is for high-performance, high clock frequency system modules. The AHB acts as the high-performance system backbone bus. Index Terms- SDRAM, Memory controller, AMBA, FPGA, Xilinx, I. INTRODUCTION In order to enhance overall performance, SDRAMs offer features including multiple internal banks, burst mode access, and pipelining of operation executions. -

All-Inclusive ECC: Thorough End-To-End Protection for Reliable Computer Memory

All-Inclusive ECC: Thorough End-to-End Protection for Reliable Computer Memory Jungrae Kim∗ Michael Sullivan∗∗ Sangkug Lym∗ Mattan Erez∗ ∗The University of Texas at Austin ∗∗NVIDIA fdale40, sklym, [email protected] [email protected] Abstract—Increasing transfer rates and decreasing I/O voltage DDR1 levels make signals more vulnerable to transmission errors. While DDR2 the data in computer memory are well-protected by modern DDR3 1.6 Gbps error checking and correcting (ECC) codes, the clock, control, DDR4 3.2 Gbps command, and address (CCCA) signals are weakly protected GDDR3 GDDR4 or even unprotected such that transmission errors leave serious 3.5 Gbps gaps in data-only protection. This paper presents All-Inclusive GDDR5 7 Gbps 14 Gbps ECC (AIECC), a memory protection scheme that leverages and GDDR5X augments data ECC to also thoroughly protect CCCA signals. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 AIECC provides strong end-to-end protection of memory, cmd rate (per pin) addr rate (per pin) data rate (per pin) detecting nearly 100% of CCCA errors and also preventing (a) The increasing maximum DRAM transfer rates of command, address, transmission errors from causing latent memory data corruption. and data signals. AIECC provides these system-level benefits without requiring 3 2.5 8 extra storage and transfer overheads and without degrading the Core power IO power 2.5 effective level of data protection. 1.8 6 3.49 2 (46%) 2.88 1.5 1.35 2.88 1.5 1.2 (47%) (42%) 4 (52%) 1 4.13 1.48 VDD (V) 0.5 2 3.23 2.65 I. -

Swissbit SMT Memory Product Guide Rev1.9.Pub

SWISSMEMORY™ Industrial Product Line DRAM Memory Products Solutions for Industrial and Embedded Applications Surface Mount Technology (SMT) DDR3 DDR2 DDR SDRAM DRAM Visit us at www.swissbit.com Version 1.9 - 01/2009 DDR3 SDRAM TECHNOLOGY SDRAM DDR3 modules are Swissbit’s most recent Double Data Rate products to market. DDR3 is the memory choice for performance driven systems with clock frequencies of 400 to 800MHz and data rates of 800 to 1600 Mb per second. In addition to DDR3’s improved performance in dual- and multi-core systems, it also provides increased efficiency with lower power consumption. DDR3 power consumption is approximately 20% or more lower than its predecessor at 1.35V to 1.5V as compared to the 1.8V of DDR2. Swissbit offers DDR3’s unmatched combination of high bandwidth and density with lower power consumption in the variety of module packages. Density Swissbit PN Data Rate (MT/s) - CL Height # IC’s IC Org Rank DDR3 SDRAM UDIMM (240 pin) 512MB (64Mx64) SGU06464C1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 4 64Mx16 1 1GB (128Mx64) SGU12864D1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 8 128Mx8 1 2GB (256Mx64) SGU25664E1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 16 128Mx8 2 DDR3 SDRAM UDIMM w/ ECC (240 pin) 512MB (64Mx72) SGU06472H1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 5 64Mx16 1 1GB (128Mx72) SGU12872F1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 9 128Mx8 1 2GB (256Mx72) SGU25672G1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 18 128Mx8 2 DDR3 SDRAM