Hardware Systems: Processor and Board Alternatives

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SBC-410 Half-Size 486 All-In-One CPU Card with Cache

SBC-410 Half-size 486 All-in-One CPU Card with Cache FCC STATEMENT THIS DEVICE COMPLIES WITH PART 15 FCC RULES. OPERA- TION IS SUBJECT TO THE FOLLOWING TWO CONDITIONS: (1) THIS DEVICE MAY NOT CAUSE HARMFUL INTERFER- ENCE. (2) THIS DEVICE MUST ACCEPT ANY INTERFERENCE RECEIVED INCLUDING INTERFERENCE THAT MAY CAUSE UNDESIRED OPERATION. THIS EQUIPMENT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS "A" DIGITAL DEVICE, PURSUANT TO PART 15 OF THE FCC RULES. THESE LIMITS ARE DESIGNED TO PROVIDE REASON- ABLE PROTECTION AGAINTST HARMFUL INTERFER- ENCE WHEN THE EQUIPMENT IS OPERATED IN A COMMERCIAL ENVIRONMENT. THIS EQUIPMENT GENER- ATES, USES, AND CAN RADIATE RADIO FREQENCY ENERGY AND , IF NOT INSTATLLED AND USED IN ACCOR- DANCE WITH THE INSTRUCTION MANUAL, MAY CAUSE HARMFUL INTERFERENCE TO RADIO COMMUNICA- TIONS. OPERATION OF THIS EQUIPMENT IN A RESIDEN- TIAL AREA IS LIKELY TO CAUSE HARMFUL INTERFER- ENCE IN WHICH CASE THE USER WILL BE REQUIRED TO CORRECT THE INTERFERENCE AT HIS OWN EX- PENSE. Copyright Notice This document is copyrighted, 1997, by AAEON Technology Inc. All rights are reserved. AAEON Technology Inc. reserves the right to make improvements to the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of AAEON Technology Inc. Information provided in this manual is intended to be accurate and reliable. However, AAEON Technology Inc. assumes no responsibility for its use, nor for any infringements upon the rights of third parties which may result from its use. -

The Great Telecom Meltdown for a Listing of Recent Titles in the Artech House Telecommunications Library, Turn to the Back of This Book

The Great Telecom Meltdown For a listing of recent titles in the Artech House Telecommunications Library, turn to the back of this book. The Great Telecom Meltdown Fred R. Goldstein a r techhouse. com Library of Congress Cataloging-in-Publication Data A catalog record for this book is available from the U.S. Library of Congress. British Library Cataloguing in Publication Data Goldstein, Fred R. The great telecom meltdown.—(Artech House telecommunications Library) 1. Telecommunication—History 2. Telecommunciation—Technological innovations— History 3. Telecommunication—Finance—History I. Title 384’.09 ISBN 1-58053-939-4 Cover design by Leslie Genser © 2005 ARTECH HOUSE, INC. 685 Canton Street Norwood, MA 02062 All rights reserved. Printed and bound in the United States of America. No part of this book may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the publisher. All terms mentioned in this book that are known to be trademarks or service marks have been appropriately capitalized. Artech House cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark. International Standard Book Number: 1-58053-939-4 10987654321 Contents ix Hybrid Fiber-Coax (HFC) Gave Cable Providers an Advantage on “Triple Play” 122 RBOCs Took the Threat Seriously 123 Hybrid Fiber-Coax Is Developed 123 Cable Modems -

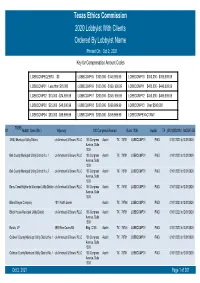

Texas Ethics Commission 2020 Lobbyist with Clients Ordered by Lobbyist Name Printed on Oct 2, 2021 Key for Compensation Amount Codes

Texas Ethics Commission 2020 Lobbyist With Clients Ordered By Lobbyist Name Printed On Oct 2, 2021 Key for Compensation Amount Codes LOBBCOMPEQZERO $0 LOBBCOMP05 $100,000 - $149,999.99 LOBBCOMP10 $350,000 - $399,999.99 LOBBCOMP01 Less than $10,000 LOBBCOMP06 $150,000 - $199, 999.99 LOBBCOMP11 $400,000 - $449,999.99 LOBBCOMP02 $10,000 - $24,999.99 LOBBCOMP07 $200,000 - $249, 999.99 LOBBCOMP12 $450,000 - $499,999.99 LOBBCOMP03 $25,000 - $49,000.99 LOBBCOMP08 $250,000 - $299,999.99 LOBBCOMP13 Over $500,000 LOBBCOMP04 $50,000 - $99,999.99 LOBBCOMP09 $300,000 - $349,999.99 LOBBCOMPEXACTAMT 70358 #1 Abbott, Sean (Mr.) Attorney 100 Congress Avenue Suite 1300 Austin TX (512)4352334 MODIFIED 3 B&J Municipal Utility District c/o Armbrust & Brown, PLLC 100 Congress Austin TX 78701 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Avenue, Suite 1300 Bell County Municipal Utility District No. 1 c/o Armbrust & Brown, PLLC 100 Congress Austin TX 78701 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Avenue, Suite 1300 Bell County Municipal Utility District No. 2 c/o Armbrust & Brown, PLLC 100 Congress Austin TX 78701 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Avenue, Suite 1300 Berry Creek Highlands Municipal Utility District c/o Armbrust & Brown, PLLC 100 Congress Austin TX 78701 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Avenue, Suite 1300 Blake Magee Company 1011 North Lamar Austin TX 78704 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Block House Municipal Utility District c/o Armbrust & Brown, PLLC 100 Congress Austin TX 78701 LOBBCOMP01 PAID 01/01/2020 to12/31/2020 Avenue, Suite 1300 Bonzo, LP 3939 Bee Caves Rd. -

Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses

of Commerce Computer Science National Bureau and Technology of Standards NBS Special Publication 500-110 Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses QO IGf) .U57 500-110 NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act ot Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides; (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is per- formed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology. THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; develops, produces, and -

586 Vs. 586 CPU Proliferation Creates Need for Benchmarks to Sort Them Out

MICROPROCESSOR REPORT THE PUBLISHER’S VIEW Coming Next Year: 586 vs. 586 CPU Proliferation Creates Need for Benchmarks To Sort Them Out Not so long ago, the name—or, more likely, the tion. Unlike the Nx586, these two chips will have FPUs, number—for a microprocessor was a technical issue of and they will be pin-compatible with Pentium. little importance. Beyond providing an association with Based on the design techniques used—such as reg- the supplier, microprocessor designations were chosen to ister renaming and out-of-order execution—the Nx586, reflect the technical features of the chip. K5, and M1 all go beyond Pentium. In some ways, they The emergence of personal computers as consumer may resemble Intel’s P6 more than Pentium. Neverthe- items has brought a new set of priorities for micropro- less, none of them qualify as a 686, because they don’t cessor names. Intel is investing hundreds of millions of come close to doubling Pentium performance and fall dollars to establish the Pentium name, and the Intel short of P6’s expected performance. name itself, as household words. At the same time, a pro- The 586 name won’t refer to a particular pin config- liferation of differing microprocessor designs from half a uration, feature set, or microarchitecture. What it does dozen vendors has made the naming challenge more refer to is a performance level, what we have called Pen- complex than ever before. tium-class performance: 60–100 SPECint92 today, with The x86 naming scheme used to be simple. From floating-point scores modestly lower than integer. -

Embedded Intel486™ Processor Hardware Reference Manual

Embedded Intel486™ Processor Hardware Reference Manual Release Date: July 1997 Order Number: 273025-001 The embedded Intel486™ processors may contain design defects known as errata which may cause the products to deviate from published specifications. Currently characterized errata are available on request. Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or oth- erwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel retains the right to make changes to specifications and product descriptions at any time, without notice. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683 or visit Intel’s web site at http:\\www.intel.com Copyright © INTEL CORPORATION, July 1997 *Third-party brands and names are the property of their respective owners. CONTENTS CHAPTER 1 GUIDE TO THIS MANUAL 1.1 MANUAL CONTENTS .................................................................................................. -

The State Board of Education

THE STAte OF the RELIGIOUS RIGht { 2008 } THE STATE BOARD OF EDUCATION: DRAGGING TEXAS SCHOOLS INTO THE CULTURE WARS THE STAte OF the RELIGIOUS RIGht { 2008 } THE STATE BOARD OF EDUCATION: DRAGGING TEXAS SCHOOLS INTO THE CULTURE WARS A R E p ort f ro m the T exas f R E E D O m N etwor k E ducation f U N D kathy miller, TFN president Dan Quinn, TFN communications director Bren Gorman, researcher Judie Niskala, researcher Emily Sentilles, researcher A bout the T f N E ducation f U N D The Texas Freedom Network Education Fund is a 501(c)(3) tax-exempt, nonprofit corporation. Created in 1996, the TFN Education Fund researches the agenda, activities and funding of the religious right. It also educates mainstream people of faith in how to formulate and to advocate a faith-based response to the religious right’s policy agenda. TfN Education fund Board of Directors Rebecca Lightsey, chair Janis pinnelli, treasurer Rev. Dr. Larry Bethune Grace Garcia Diane Ireson Dale Linebarger Table Of Contents Introduction. .2. Watch List: 2008. .5 1: The State Board of Education in Texas. .11 2: A History of Censorship in Texas. .17 3: The Right Ascendant. 21 4: Targeting Curriculum Standards (TEKS). .25 Appendices Appendix A: Who’s Who in Texas Textbook Censorship . .30 Appendix B: Textbook Censorship in Texas: A Timeline. .32 Appendix C: Textbook Censorship in Texas: The Record. .35 Appendix D: They Really Said It: Quoting the Religious Right in 2007 .. .. .. .. .. .. .. ...36 Appendix E: Organizations of the Religious Right in Texas. -

Torrents of Information Flood in to NASA Each Day From

BY DREW ROBB orrents of information flood in to NASA each day from III processors and 2GB of RAM. Custom software linked the 25 satellites patrolling both the earth and the solar system. A workstations, connected on a common subnet, into a grid so that T large portion of that information is managed by Dr. they would all act as a single parallel computing system. While this Jonathan Jiang and his colleagues. Jiang is a climatologist at worked for the early stages of development, when it came time to NASA’s Jet Propulsion Laboratory (JPL) in Pasadena, CA, part of start running simulations, more power was needed. The MLS team a team working on the Aura satellite, which is scheduled for launch opted to add a cluster using the same software they were using to in January 2004. run the grid in order to get the necessary speed. To process the data that will come from the Aura spacecraft, But in selecting a vendor and building the cluster, JPL had a spe- NASA is relying on Linux clusters. This article will examine the cific requirement that the cluster run on the same grid software the Aura satellite’s mission and how JPL scientists are using a Linux MLS team already had in place. The grid would remain in use, while cluster to process satellite data and use it to model climate change. the cluster added additional processors for concurrent or backup use. “We were pleased with the results we had gotten with our grid,” says SPACE PENGUIN Navnit Patel, a contractor from ERC Incorporated (Huntsville, AL) who operates as the team’s Science Computing Facility Manager. -

M4-4X4 / M4-4X4s / M4-4X2 / M4-4X2s / PCS42P

M4-4x4 / M4-4x4S / M4-4x2 / M4-4x2S / PCS42P CHARACTERISTICS This Personal Computer line is highly modular. The different models of this product line, in fact, are the result of the combination of two different board versions (ENTRY and ENHANCED), different CPUs (i486SX, i486SX2, i486DX2 and Intel DX4) and two different cases (TIN BOX and SLIM TIN BOX). The models of this product line are listed in the following table. 4 CASE MOTHER- PROCESSOR COMMERCIAL OLIVETTI BOARD NAME PROJECT NAME TIN BOX ENTRY i486SX @ 33 MHz MODULO M4-422 KPT44 S33 i486SX2 @ 50 MHz MODULO M4-432 KPT44 S50 i486DX2 @ 50 MHz MODULO M4-452 KPT44 D50 i486SX @ 25 MHz PCS42P SX/25 E XST41 S25 i486SX @ 33 MHz PCS42P SX/33 E XST41 S33 i486SX2 @ 50 MHz PCS42P S2/50 E XST41 S50 ENHANCED i486SX @ 33 MHz MODULO M4-424 KPT45 S33 i486SX2 @ 50 MHz MODULO M4-434 KPT45 S50 i486DX2 @ 50 MHz MODULO M4-454 KPT45 D50 i486DX2 @ 66 MHz MODULO M4-464 KPT45 D66 Intel DX4 @ 100 MHz MODULO M4-484 KPT45 DX4 i486DX2 @ 50 MHz PCS42P D2/50 E XST42 D250 i486DX2 @ 66 MHz PCS42P D2/66 E XST42 D266 SLIM TIN BOX ENTRY i486SX @ 33 MHz MODULO M4-422 S KPS44 S33 i486SX2 @ 50 MHz MODULO M4-432 S KPS44 S50 i486DX2 @ 50 MHz MODULO M4-452 S KPS44 D50 i486SX @ 25 MHz PCS42P SX/25 XSS41 S25 i486SX @ 33 MHz PCS42P SX/33 XSS41 S33 i486SX2 @ 50 MHz PCS42P S2/50 XSS41 S50 ENHANCED i486SX @ 33 MHz MODULO M4-424 S KPS45 S33 i486SX2 @ 50 MHz MODULO M4-434 S KPS45 S50 i486DX2 @ 50 MHz MODULO M4-454 S KPS45 D50 i486DX2 @ 66 MHz MODULO M4-464 S KPS45 D66 Intel DX4 @ 100 MHz MODULO M4-484 S KPS45 DX4 i486DX2 @ 50 MHz -

Assessment of Data Rates on the Internal and External Cpu Interfaces and Its Applications for Wireless Network-On-Chip Development

MARIIA KOMAR ASSESSMENT OF DATA RATES ON THE INTERNAL AND EXTERNAL CPU INTERFACES AND ITS APPLICATIONS FOR WIRELESS NETWORK-ON-CHIP DEVELOPMENT Master of Science thesis Examiner: Prof. Yevgeni Koucheryavy, Dr. Dmitri Moltchanov Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 27th September 2017 I ABSTRACT MARIIA KOMAR: Assessment of data rates on the internal and external CPU interfaces and its applications for Wireless Network-on-Chip development Tampere University of Technology Master of Science thesis, 56 pages November 2017 Master's Degree Programme in Information Technology Major: Information Technology Examiner: Prof. Yevgeni Koucheryavy, Dr. Dmitri Moltchanov Keywords: central processing unit, CPU, CPU performance, Wireless Networks-on-Chip, WNoC, data rates assessment Nowadays central processing units (CPUs) are the major part of the personal com- puters, and usually their progress denes personal computers (PCs) progress. How- ever, modern CPU architecture has a set of limitations mentioned in this thesis. As a result, new CPU architectures are now under development. Most prospective solution in this eld are based on a proposed concept of Wireless Networks-on-Chip (WNoCs), where part of wired connections is changed into wireless links. However in order to design and develop this kind of system, information about data rates on the internal and external CPU interfaces of modern CPUs is needed. Main goals set in the beginning of working on this thesis were to get this data rates assessment and give an assessment of suitable wireless technologies for milticore CPUs with dierent number of cores. In this thesis CPU evolution is described and peculiarities of modern CPU archi- tectures are mentioned. -

Low Cost Video for Distance Education Michael J

Nova Southeastern University NSUWorks CEC Theses and Dissertations College of Engineering and Computing 1996 Low Cost Video For Distance Education Michael J. Simpson Nova Southeastern University, [email protected] This document is a product of extensive research conducted at the Nova Southeastern University College of Engineering and Computing. For more information on research and degree programs at the NSU College of Engineering and Computing, please click here. Follow this and additional works at: https://nsuworks.nova.edu/gscis_etd Part of the Computer Sciences Commons Share Feedback About This Item NSUWorks Citation Michael J. Simpson. 1996. Low Cost Video For Distance Education. Doctoral dissertation. Nova Southeastern University. Retrieved from NSUWorks, Graduate School of Computer and Information Sciences. (842) https://nsuworks.nova.edu/gscis_etd/842. This Dissertation is brought to you by the College of Engineering and Computing at NSUWorks. It has been accepted for inclusion in CEC Theses and Dissertations by an authorized administrator of NSUWorks. For more information, please contact [email protected]. Low Cost Video for Distance Education by Michael J. Simpson A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy School of Computer and Information Sciences Nova Southeastern University 1996 We hereby certify that this dissertation, submitted by Michael J. Simpson, conforms to acceptable standards and is fully adequate in scope and quality to fulfill the dissertation requirements for the degree of Doctor of Philosophy. _______________________________________________________ Jacques C. Levin, Ph.D. Date Chairman of Dissertation Committee _______________________________________________________ John A. Scigliano, Ed.D. Date Dissertation Committee Member _______________________________________________________ Steven R. Terrell, Ed.D. -

Datapoint Oral History Panel

Datapoint Oral History Panel Henry Donzis, Lewis Donzis, John Murphy, Jonathan Schmidt Interviewed by: Len Shustek and Harry Saal Recorded: June 3, 2004 San Antonio, Texas CHM Reference number: X2850.2005 © 2004 Computer History Museum Datapoint Oral History Panel Len Shustek: June 3, 2004. We are doing a Computer History Museum world interview. And you’re here with John Murphy, Jonathan Schmidt, Lewis Donzis, and Henry Donzis, all at one time working for Datapoint. And we’ve actually done the individual histories with Jonathan and John. Maybe we should start with giving a little background, getting a little background from the Donzis brothers, find out how they got associated with these characters. In fact any of you can tell that story. Lewis Donzis: We get younger all the time. Henry Donzis: We get younger. Jonathan Schmidt: Henry was four and Lewis was two. Lewis Donzis: And I wasn’t born yet. Jonathan Schmidt: Oh he wasn’t born yet. Yes, we had- Henry was recommended as a brilliant potential computer scientist by his math teacher. Henry Donzis: Forester High School Jonathan Schmidt: Forster. Henry Donzis: Mr. Foster. Well I think it started out with you being- cause I used to- was using Al's basic computer. Lewis Donzis: Wasn’t that because of Gus Roache’s son ? Henry Donzis: It was Arty Roache . Jonathan Schmidt: Forgot about that. Lewis Donzis: Well there you go. Henry Donzis: Well that’s... Jonathan Schmidt: Yes. Henry Donzis: And every time I would lose a program and I called, and Randy or David or Harry or somebody would have to reload the thing.