DDR3 SDRAM Features DDR3 SDRAM MT41J256M4 – 32 Meg X 4 X 8 Banks MT41J128M8 – 16 Meg X 8 X 8 Banks MT41J64M16 – 8 Meg X 16 X 8 Banks

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2GB DDR3 SDRAM 72Bit SO-DIMM

Apacer Memory Product Specification 2GB DDR3 SDRAM 72bit SO-DIMM Speed Max CAS Component Number of Part Number Bandwidth Density Organization Grade Frequency Latency Composition Rank 0C 78.A2GCB.AF10C 8.5GB/sec 1066Mbps 533MHz CL7 2GB 256Mx72 256Mx8 * 9 1 Specifications z Support ECC error detection and correction z On DIMM Thermal Sensor: YES z Density:2GB z Organization – 256 word x 72 bits, 1rank z Mounting 9 pieces of 2G bits DDR3 SDRAM sealed FBGA z Package: 204-pin socket type small outline dual in line memory module (SO-DIMM) --- PCB height: 30.0mm --- Lead pitch: 0.6mm (pin) --- Lead-free (RoHS compliant) z Power supply: VDD = 1.5V + 0.075V z Eight internal banks for concurrent operation ( components) z Interface: SSTL_15 z Burst lengths (BL): 8 and 4 with Burst Chop (BC) z /CAS Latency (CL): 6,7,8,9 z /CAS Write latency (CWL): 5,6,7 z Precharge: Auto precharge option for each burst access z Refresh: Auto-refresh, self-refresh z Refresh cycles --- Average refresh period 7.8㎲ at 0℃ < TC < +85℃ 3.9㎲ at +85℃ < TC < +95℃ z Operating case temperature range --- TC = 0℃ to +95℃ z Serial presence detect (SPD) z VDDSPD = 3.0V to 3.6V Apacer Memory Product Specification Features z Double-data-rate architecture; two data transfers per clock cycle. z The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture. z Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver. z DQS is edge-aligned with data for READs; center aligned with data for WRITEs. -

Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines, External

5. Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines June 2012 EMI_DG_005-4.1 EMI_DG_005-4.1 This chapter describes guidelines for implementing dual unbuffered DIMM (UDIMM) DDR2 and DDR3 SDRAM interfaces. This chapter discusses the impact on signal integrity of the data signal with the following conditions in a dual-DIMM configuration: ■ Populating just one slot versus populating both slots ■ Populating slot 1 versus slot 2 when only one DIMM is used ■ On-die termination (ODT) setting of 75 Ω versus an ODT setting of 150 Ω f For detailed information about a single-DIMM DDR2 SDRAM interface, refer to the DDR2 and DDR3 SDRAM Board Design Guidelines chapter. DDR2 SDRAM This section describes guidelines for implementing a dual slot unbuffered DDR2 SDRAM interface, operating at up to 400-MHz and 800-Mbps data rates. Figure 5–1 shows a typical DQS, DQ, and DM signal topology for a dual-DIMM interface configuration using the ODT feature of the DDR2 SDRAM components. Figure 5–1. Dual-DIMM DDR2 SDRAM Interface Configuration (1) VTT Ω RT = 54 DDR2 SDRAM DIMMs (Receiver) Board Trace FPGA Slot 1 Slot 2 (Driver) Board Trace Board Trace Note to Figure 5–1: (1) The parallel termination resistor RT = 54 Ω to VTT at the FPGA end of the line is optional for devices that support dynamic on-chip termination (OCT). © 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. -

AN 436: Using DDR3 SDRAM in Stratix III and Stratix IV Devices.Pdf

AN 436: Using DDR3 SDRAM in Stratix III and Stratix IV Devices © November 2008 AN-436-4.0 Introduction DDR3 SDRAM is the latest generation of DDR SDRAM technology, with improvements that include lower power consumption, higher data bandwidth, enhanced signal quality with multiple on-die termination (ODT) selection and output driver impedance control. DDR3 SDRAM brings higher memory performance to a broad range of applications, such as PCs, embedded processor systems, image processing, storage, communications, and networking. Although DDR2 SDRAM is currently the more popular SDRAM, to save system power and increase system performance you should consider using DDR3 SDRAM. DDR3 SDRAM offers lower power by using 1.5 V for the supply and I/O voltage compared to the 1.8-V supply and I/O voltage used by DDR2 SDRAM. DDR3 SDRAM also has better maximum throughput compared to DDR2 SDRAM by increasing the data rate per pin and the number of banks (8 banks are standard). 1 The Altera® ALTMEMPHY megafunction and DDR3 SDRAM high-performance controller only support local interfaces running at half the rate of the memory interface. Altera Stratix® III and Stratix IV devices support DDR3 SDRAM interfaces with dedicated DQS, write-, and read-leveling circuitry. Table 1 displays the maximum clock frequency for DDR3 SDRAM in Stratix III devices. Table 1. DDR3 SDRAM Maximum Clock Frequency Supported in Stratix III Devices (Note 1), (2) Speed Grade fMAX (MHz) –2 533 (3) –3 and I3 400 –4, 4L, and I4L at 1.1 V 333 (4), (5) –4, 4L, and I4L at 0.9 V Not supported Notes to Table 1: (1) Numbers are preliminary until characterization is final. -

High Bandwidth Memory for Graphics Applications Contents

High Bandwidth Memory for Graphics Applications Contents • Differences in Requirements: System Memory vs. Graphics Memory • Timeline of Graphics Memory Standards • GDDR2 • GDDR3 • GDDR4 • GDDR5 SGRAM • Problems with GDDR • Solution ‐ Introduction to HBM • Performance comparisons with GDDR5 • Benchmarks • Hybrid Memory Cube Differences in Requirements System Memory Graphics Memory • Optimized for low latency • Optimized for high bandwidth • Short burst vector loads • Long burst vector loads • Equal read/write latency ratio • Low read/write latency ratio • Very general solutions and designs • Designs can be very haphazard Brief History of Graphics Memory Types • Ancient History: VRAM, WRAM, MDRAM, SGRAM • Bridge to modern times: GDDR2 • The first modern standard: GDDR4 • Rapidly outclassed: GDDR4 • Current state: GDDR5 GDDR2 • First implemented with Nvidia GeForce FX 5800 (2003) • Midway point between DDR and ‘true’ DDR2 • Stepping stone towards DDR‐based graphics memory • Second‐generation GDDR2 based on DDR2 GDDR3 • Designed by ATI Technologies , first used by Nvidia GeForce FX 5700 (2004) • Based off of the same technological base as DDR2 • Lower heat and power consumption • Uses internal terminators and a 32‐bit bus GDDR4 • Based on DDR3, designed by Samsung from 2005‐2007 • Introduced Data Bus Inversion (DBI) • Doubled prefetch size to 8n • Used on ATI Radeon 2xxx and 3xxx, never became commercially viable GDDR5 SGRAM • Based on DDR3 SDRAM memory • Inherits benefits of GDDR4 • First used in AMD Radeon HD 4870 video cards (2008) • Current -

DDR3 SODIMM Product Datasheet

DDR3 SODIMM Product Datasheet 廣 穎 電 通 股 份 有 限 公 司 Silicon Power Computer & Communications Inc. TEL: 886-2 8797-8833 FAX: 886-2 8751-6595 台北市114內湖區洲子街106號7樓 7F, No.106, ZHO-Z ST. NEIHU DIST, 114, TAIPEI, TAIWAN, R.O.C This document is a general product description and is subject to change without notice DDR3 SODIMM Product Datasheet Index Index...................................................................................................................................................................... 2 Revision History ................................................................................................................................................ 3 Description .......................................................................................................................................................... 4 Features ............................................................................................................................................................... 5 Pin Assignments................................................................................................................................................ 7 Pin Description................................................................................................................................................... 8 Environmental Requirements......................................................................................................................... 9 Absolute Maximum DC Ratings.................................................................................................................... -

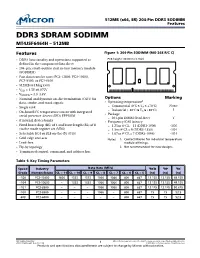

512MB (X64, SR) 204-Pin DDR3 SODIMM Features DDR3 SDRAM SODIMM MT4JSF6464H – 512MB

512MB (x64, SR) 204-Pin DDR3 SODIMM Features DDR3 SDRAM SODIMM MT4JSF6464H – 512MB Features Figure 1: 204-Pin SODIMM (MO-268 R/C C) • DDR3 functionality and operations supported as PCB height: 30.0mm (1.18in) defined in the component data sheet • 204-pin, small-outline dual in-line memory module (SODIMM) • Fast data transfer rates: PC3-12800, PC3-10600, PC3-8500, or PC3-6400 • 512MB (64 Meg x 64) • VDD = 1.5V ±0.075V • VDDSPD = 3.0–3.6V • Nominal and dynamic on-die termination (ODT) for Options Marking 1 data, strobe, and mask signals • Operating temperature – Commercial (0°C ≤ T ≤ +70°C) None • Single rank A – Industrial (–40°C ≤ T ≤ +85°C) I • On-board I2C temperature sensor with integrated A Package serial presence-detect (SPD) EEPROM • – 204-pin DIMM (lead-free) Y 8 internal device banks • • Frequency/CAS latency • Fixed burst chop (BC) of 4 and burst length (BL) of 8 – 1.25ns @ CL = 11 (DDR3-1600) -1G6 via the mode register set (MRS) – 1.5ns @ CL = 9 (DDR3-1333) -1G4 • Selectable BC4 or BL8 on-the-fly (OTF) – 1.87ns @ CL = 7 (DDR3-1066) -1G1 • Gold edge contacts Notes: 1. Contact Micron for industrial temperature • Lead-free module offerings. • Fly-by topology 2. Not recommended for new designs. • Terminated control, command, and address bus Table 1: Key Timing Parameters Speed Industry Data Rate (MT/s) tRCD tRP tRC Grade Nomenclature CL = 11 CL = 10 CL = 9 CL = 8 CL = 7 CL = 6 CL = 5 (ns) (ns) (ns) -1G6 PC3-12800 1600 1333 1333 1066 1066 800 667 13.125 13.125 48.125 -1G4 PC3-10600 – 1333 1333 1066 1066 800 667 13.125 13.125 49.125 -1G1 PC3-8500 – – – 1066 1066 800 667 13.125 13.125 50.625 -1G0 PC3-8500 – – – 1066 – 800 667 15 15 52.5 -80B PC3-6400 – – – – – 800 667 15 15 52.5 PDF: 09005aef82b2f090 Micron Technology, Inc. -

Swissbit SMT Memory Product Guide Rev1.9.Pub

SWISSMEMORY™ Industrial Product Line DRAM Memory Products Solutions for Industrial and Embedded Applications Surface Mount Technology (SMT) DDR3 DDR2 DDR SDRAM DRAM Visit us at www.swissbit.com Version 1.9 - 01/2009 DDR3 SDRAM TECHNOLOGY SDRAM DDR3 modules are Swissbit’s most recent Double Data Rate products to market. DDR3 is the memory choice for performance driven systems with clock frequencies of 400 to 800MHz and data rates of 800 to 1600 Mb per second. In addition to DDR3’s improved performance in dual- and multi-core systems, it also provides increased efficiency with lower power consumption. DDR3 power consumption is approximately 20% or more lower than its predecessor at 1.35V to 1.5V as compared to the 1.8V of DDR2. Swissbit offers DDR3’s unmatched combination of high bandwidth and density with lower power consumption in the variety of module packages. Density Swissbit PN Data Rate (MT/s) - CL Height # IC’s IC Org Rank DDR3 SDRAM UDIMM (240 pin) 512MB (64Mx64) SGU06464C1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 4 64Mx16 1 1GB (128Mx64) SGU12864D1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 8 128Mx8 1 2GB (256Mx64) SGU25664E1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 16 128Mx8 2 DDR3 SDRAM UDIMM w/ ECC (240 pin) 512MB (64Mx72) SGU06472H1CB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 5 64Mx16 1 1GB (128Mx72) SGU12872F1BB1xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 9 128Mx8 1 2GB (256Mx72) SGU25672G1BB2xx-ssR 800-CL5 / 1066-CL7 / 1333-CL9 1.18" (29.97mm) 18 128Mx8 2 DDR3 SDRAM -

SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer

Primer SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer Table of Contents Introduction . 3 - 4 DRAM Trends . .3 DRAM . 4 - 6 SDRAM . 6 - 9 DDR SDRAM . .6 DDR2 SDRAM . .7 DDR3 SDRAM . .8 DDR4 SDRAM . .9 GDDR and LPDDR . .9 DIMMs . 9 - 13 DIMM Physical Size . 9 DIMM Data Width . 9 DIMM Rank . .10 DIMM Memory Size & Speed . .10 DIMM Architecture . .10 Serial Presence Detect . .12 Memory System Design . .13 - 15 Design Simulation . .13 Design Verification . .13 Verification Strategy . .13 SDRAM Verification . .14 Glossary . .16 - 19 2 www.tektronix.com/memory SDRAM Memory Systems: Architecture Overview and Design Verification Primer Introduction Memory needs to be compatible with a wide variety of memory controller hubs used by the computer DRAM (Dynamic Random Access Memory) is attractive to manufacturers. designers because it provides a broad range of performance Memory needs to work when a mixture of different and is used in a wide variety of memory system designs for manufacturer’s memories is used in the same memory computers and embedded systems. This DRAM memory system of the computer. primer provides an overview of DRAM concepts, presents potential future DRAM developments and offers an overview Open memory standards are useful in helping to ensure for memory design improvement through verification. memory compatibility. DRAM Trends On the other hand, embedded systems typically use a fixed There is a continual demand for computer memories to be memory configuration, meaning the user does not modify larger, faster, lower powered and physically smaller. These the memory system after purchasing the product. -

A High Performance DDR3 SDRAM Controller

A High Performance DDR3 SDRAM Controller A High Performance DDR3 SDRAM Controller Shabana Aqueel* and Kavita Khare** * Dept. of Electronics and Communication, M.A.N.I.T, Bhopal, India ** Dept. of Electronics and Communication, M.A.N.I.T, Bhopal, India E-mail - [email protected] Abstract—The paper presents the implementation of of memory density, hardware cost and power dissipation. compliant DDR3 memory controller. It discusses the overall CAM is widely used in network equipment for fast table look architecture of the DDR3 controller along with the detailed up [1]. Recently, a Hash-CAM circuit [2], which combines the design and operation of its individual sub blocks, the merits of the hash algorithm and the CAM function, was pipelining implemented in the design to increase the design proposed to replace pure CAM based lookup circuits with throughput. It also discusses the advantages of DDR3 comparable performance, higher memory density and lower memories over DDR2 memories operation. Double Data cost. Efficient DDR bandwidth utilization [3] is a major Rate (DDR) SDRAMs have been prevalent in the PC challenge for lookup functions that exhibit short and random memory market in recent years and are widely used for memory access patterns. Most importantly, off-chip high- networking systems. These memory devices are rapidly density low-cost DDR memory technology has now become developing, with high density, high memory bandwidth and an attractive alternative for the proposed Hash-CAM based low device cost. However, because of the high-speed lookup circuit. However, DDR technology is optimized for interface technology and complex instruction-based memory burst access for cached processor platforms. -

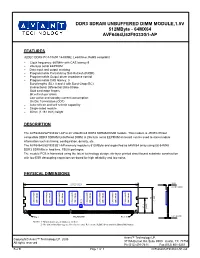

DDR3 SDRAM UNBUFFERED DIMM MODULE,1.5V 512Mbyte - 64MX64 AVF6464U52F9333G1-AP

Rev B All rights reserved Copyright© Avant with low ESR decoupling capacitorsThe on-board module for PCB high is reliability fabricated andDDR3 using low the noise. latest technology design,The six-layer printed circuit board substrateinformation constructi such as timing, configuration,compatible density, DDR3 etc. SDRAM Unbuffered DIMM.The A 256 byte serial EEPROM on board can be used toDESCRIPTI store module JEDEC DDR3 PC3-10600 1333MHz, Lead Free, RoHSFEATURES compliant PHYSICAL DIMENSIONS 30mm (1.181 inch) height Data input and output masking AVF6464U52F9333G1-AP AVF6464U52F9333G1-AP Single-sided module Auto refresh and self refreshOn Die capability Termination (ODT) Low active and standby current8K consumption refresh per 64 Gold card edge fingers Bi-directional Differential Data-Strobe Burst lengths (BL): 8 andProgrammable 4 CAS with latency: Burst 9 ChopProgrammable (BC) Output driver impedanceProgrammable control Partial Array Self-Refresh (PASR) 256 byte serial EEPROM Clock frequency: 667MHz with CAS latency 9 SDRAMs in lead free, FBGA packages. NOTES: 1- All dimensions are in milimeters (inches) Pin 1 512Mbit (64MbX8) ™ DDR3 SDRAM Technology LP. 2008 2- The dimensional drawings are for reference only. Refer to the JEDEC document for additional information. ON 512Mbit (64MbX8) DDR3 SDRAM ms 512Mbit (64MbX8) DDR3 SDRAM memory module is 512MByte and organized as 64MX64 array using (8) 64MX8 is an Unbuffered DDR3 SDRAM DIMM module. This module is JEDEC Pinout 133.25 (5.25) 512Mbit (64MbX8) FRONT SIDE DDR3 SDRAM DDR3 SDRAM UNBUFFERED DIMM MODULE,1.5V SPD 512Mbit (64MbX8) Page DDR3 SDRAM 1 of 512Mbit (64MbX8) AVF6464U52F9333G1-AP 7 DDR3 SDRAM 512MByte - 64MX64 512Mbit (64MbX8) DDR3 SDRAM Pin 120 Ph (512) 491-7411 9715A Burnet Rd. -

Keystone Architecture DDR3 Memory Controller

Keystone Architecture DDR3 Memory Controller User's Guide Literature Number: SPRUGV8E November 2010–Revised January 2015 Contents Preface....................................................................................................................................... 11 1 Introduction ....................................................................................................................... 13 1.1 Purpose of the Peripheral ................................................................................................. 14 1.2 Features ..................................................................................................................... 14 1.3 Industry Standard(s) Compliance Statement ........................................................................... 14 2 Peripheral Architecture ....................................................................................................... 16 2.1 Clock Interface.............................................................................................................. 17 2.2 SDRAM Memory Map ..................................................................................................... 17 2.3 Signal Descriptions......................................................................................................... 17 2.4 Protocol Descriptions ...................................................................................................... 18 2.4.1 Mode Register Set (MRS or EMRS) ........................................................................... -

DDR Sdrams a Suncam Online Continuing Education Course

Memories in Computers—Part 2: DDR SDRAMs A SunCam online continuing education course Memories in Computers Part 2: DDR SDRAMs by Dr. William R. Huber, P.E. www.SunCam.com Copyright 2011 William R. Huber (updated 2018) Page 1 of 43 Memories in Computers—Part 2: DDR SDRAMs A SunCam online continuing education course A. Introduction To understand the operation and advantages of Double Data Rate (DDR) Synchronous Dynamic Random Access Memories (DDR SDRAMs), we will start by reviewing the architecture of a single data rate (SDR) SDRAM. In keeping with industry practice, the balance of this course will refer to SDR SDRAMs simply as SDRAMs. A Micron data sheet provides a functional block diagram.1 1 Micron MT48LC128M4A2 512Mb SDRAM Data Sheet, Rev. M 6/10 EN, page 8 www.SunCam.com Copyright 2011 William R. Huber (updated 2018) Page 2 of 43 Memories in Computers—Part 2: DDR SDRAMs A SunCam online continuing education course SDRAM architecture is very similar to that of an asynchronous DRAM, with the addition of Command Inputs (CS#, WE#, CAS# and RAS#)2, Clock Inputs (CKE, CLK) and Control Logic including Command Decode and Mode Register. Some of the significant differences in the operation of an SDRAM as compared to a DRAM are as follows: • SDRAM operation is initiated by the low to high transition of the external clock, and data bits are input or output in synchronism with the external clock; • In an SDRAM, the operational mode (ACTIVE, READ, WRITE, REFRESH, etc.) is established by a command issued at the beginning of the cycle; • The SDRAM command is defined by the logic state of several inputs (e.g.; RAS#, CAS#, WE# and A10) when CS# (Chip Select) is low, CKE (Clock Enable) is high, and CLK (external Clock) transitions from low to high; • The SDRAM is organized into banks, which can operate virtually independently of each other.