MVME3100 Single-Board Computer Programmer's Reference Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1 Decision of the Election Committee on a Due Impartiality Complaint Brought by the Respect Party in Relation to the London Deba

Decision of the Election Committee on a due impartiality complaint brought by the Respect Party in relation to The London Debate ITV London, 5 April 2016 LBC 97.3 , 5 April 2016 1. On Friday 29 April 2016, Ofcom’s Election Committee (“the Committee”)1 met to consider and adjudicate on a complaint made by the Respect Party in relation to its candidate for the London Mayoral election, George Galloway (“the Complaint”). The Complaint was about the programme The London Debate, broadcast in ITV’s London region on ITV, and on ITV HD and ITV+1 at 18:00 on Tuesday 5 April 2016 (“the Programme”). The Programme was broadcast simultaneously by LBC on the local analogue radio station LBC 97.3, as well as nationally on DAB radio and on digital television (as a radio channel). 2. The Committee consisted of the following members: Nick Pollard (Chair, Member of the Ofcom Content Board); Dame Lynne Brindley DBE (Member of the Ofcom Board and Content Board); Janey Walker (Member of the Ofcom Content Board); and Tony Close (Ofcom Director with responsibility for Content Standards, Licensing and Enforcement and Member of the Ofcom Content Board). 3. For the reasons set out in this decision, having considered all of the submissions and evidence before it under the relevant provisions of the Broadcasting Code (“the Code”), the Committee decided not to uphold the Respect Party’s complaint. The Committee found that in respect of ITV the broadcast of the Programme complied with the requirements of the Code. In the case of LBC, the Programme did not a contain list of candidates in the 2016 London Mayoral election (in audio form) and LBC therefore breached Rule 6.11. -

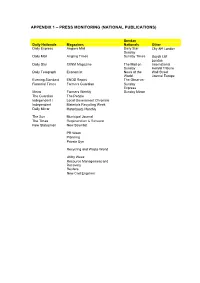

Appendix 1 – Press Monitoring (National Publications)

APPENDIX 1 – PRESS MONITORING (NATIONAL PUBLICATIONS) Sunday Daily Nationals Magazines Nationals Other Daily Express Anglers Mail Daily Star City AM London Sunday Daily Mail Angling Times Sunday Times Lloyds List London Daily Star CIWM Magazine The Mail on International Sunday Herald Tribune Daily Telegraph Economist News of the Wall Street World Journal Europe Evening Standard ENDS Report The Observer Financial Times Farmers Guardian Sunday Express Metro Farmers Weekly Sunday Mirror The Guardian The People Independent i Local Government Chronicle Independent Materials Recycling Week Daily Mirror Motorboats Monthly The Sun Municipal Journal The Times Regeneration & Renewal New Statesman New Scientist PR Week Planning Private Eye Recycling and Waste World Utility Week Resource Management and Recovery Reuters New Civil Engineer APPENDIX 2 – PRESS MONITORING (NATIONAL KEY WORDS) Keyword Keyword Description Agriculture - Environment Important mentions of farming or agriculture ICW the environment. Carbon Emissions All mentions of carbon emissions OICW climate change, global warming etc. Climate Change All mentions of climate change. Coastal Erosion All mentions of coastal erosion. DEFRA All mentions of Department for Environment, Food and Rural Affairs (DEFRA). Department of Energy & Climate All mentions of the Department of Energy & Climate Change Change (DECC) Drought Main focus mentions of droughts in the UK Environment All mentions of environmental issues Environment - Emissions Important mentions of emissions and their effect on the environment. Environment Agency All mentions of the Environment Agency. Fishing All mentions of fishing ICW the environment. Flooding - Environmental Impact Important Mentions of floods OICW effects on the environment and homes Fly Tipping All mentions of fly tipping Hosepipes All mentions of hosepipes Nuclear Power - Environmental Main focus mentions of environmental effects of nuclear power. -

BMJ in the News 29 March

BMJ in the News is a weekly digest of journal stories, plus any other news about the company that has appeared in the national and a selection of English-speaking international media. A total of 27 journals were picked up in the media last week (29 March-4 April) - our highlights include: ● Research published in The BMJ finding that levels of adherence to the UK’s test, trace, and isolate system are low made national headlines, including BBC News, The Guardian, and The Daily Telegraph. ● A BJSM study suggesting that physical inactivity is responsible for up to 8% of non-communicable diseases and deaths worldwide was picked up by CNN, ITV News, and Gulf Today. ● A study in The BMJ revealing that people discharged from hospital after covid-19 appear to have increased rates of organ damage compared with similar individuals in the general population made headlines in the Times of India, Huffington Post, and Asian Image. BMJ PRESS RELEASES The BMJ | British Journal of Ophthalmology British Journal of Sports Medicine | Thorax EXTERNAL PRESS RELEASES BMJ Nutrition, Prevention & Health | BMJ Open Gut | Journal for Immunotherapy of Cancer Stroke & Vascular Neurology OTHER COVERAGE The BMJ | Annals of the Rheumatic Diseases BMJ Case Reports | BMJ Global Health BMJ Open Gastroenterology | BMJ Open Ophthalmology BMJ Open Science | BMJ Open Sport & Exercise Medicine BMJ Supportive & Palliative Care| Heart Journal of Epidemiology & Community Health | Journal of Medical Ethics Journal of Medical Genetics | Journal of NeuroInterventional Surgery Journal -

Culture, Media and Sport Committee

House of Commons Culture, Media and Sport Committee Future of the BBC Fourth Report of Session 2014–15 Report, together with formal minutes relating to the report Ordered by the House of Commons to be printed 10 February 2015 HC 315 INCORPORATING HC 949, SESSION 2013-14 Published on 26 February 2015 by authority of the House of Commons London: The Stationery Office Limited £0.00 The Culture, Media and Sport Committee The Culture, Media and Sport Committee is appointed by the House of Commons to examine the expenditure, administration and policy of the Department for Culture, Media and Sport and its associated public bodies. Current membership Mr John Whittingdale MP (Conservative, Maldon) (Chair) Mr Ben Bradshaw MP (Labour, Exeter) Angie Bray MP (Conservative, Ealing Central and Acton) Conor Burns MP (Conservative, Bournemouth West) Tracey Crouch MP (Conservative, Chatham and Aylesford) Philip Davies MP (Conservative, Shipley) Paul Farrelly MP (Labour, Newcastle-under-Lyme) Mr John Leech MP (Liberal Democrat, Manchester, Withington) Steve Rotheram MP (Labour, Liverpool, Walton) Jim Sheridan MP (Labour, Paisley and Renfrewshire North) Mr Gerry Sutcliffe MP (Labour, Bradford South) The following Members were also a member of the Committee during the Parliament: David Cairns MP (Labour, Inverclyde) Dr Thérèse Coffey MP (Conservative, Suffolk Coastal) Damian Collins MP (Conservative, Folkestone and Hythe) Alan Keen MP (Labour Co-operative, Feltham and Heston) Louise Mensch MP (Conservative, Corby) Mr Adrian Sanders MP (Liberal Democrat, Torbay) Mr Tom Watson MP (Labour, West Bromwich East) Powers The Committee is one of the Departmental Select Committees, the powers of which are set out in House of Commons Standing Orders, principally in SO No 152. -

Overview and Scrutiny Annual Report 2016/17 Table of Contents

Overview and Scrutiny Annual Report 2016/17 Table of Contents Introduction...........................................................................................................................................3 Part One: Community and Wellbeing Scrutiny Committee ..............................................................4 1. Work programme 2016/17 ..........................................................................................................4 1.1. Housing.......................................................................................................................................4 1.2. Health .........................................................................................................................................5 1.3. Adult Social Care ........................................................................................................................6 1.4. Safeguarding ..............................................................................................................................6 1.5. Children’s Services .....................................................................................................................7 2. Task and Finish Groups..................................................................................................................8 2.1. Housing associations..................................................................................................................8 2.2. Signs of Safety............................................................................................................................8 -

Ofcom Audio Survey 2021: Questionnaire

Survey name: Ofcom Audio Survey 2021 Timings: 3-7 March 2021 Methodology: Online survey We are conducting research on behalf of the UK's communications regulator Ofcom, who are looking to understand use of and attitudes towards different types of radio and audio services. ASK ALL 1. How often, if at all, do you do any of the following? GRID ROWS – RANDOMISE ORDER 1. A. Listen to radio (at the time of broadcast: not catch-up/podcast) 2. B. Listen to catch-up radio 3. C. Listen to music online 4. D. Listen to music stored or downloaded on a device 5. E. Listen to personal music collection (e.g. CDs, vinyls) 6. F. Listen to podcasts 7. G. Listen to audiobooks (digital/online and physical) 8. H. Use music videos as background listening (i.e. music video channels or sites such as YouTube or MTV) 9. GRID COLUMNS – SINGLE CODE 1. Several times a day 2. About once a day 3. Several times a week 4. About once a week 5. Several times a month 6. About once a month 7. Less often 8. Never ASK ALL (BACK FILTER ANYONE WHO LISTS A STATION HERE BUT DID NOT CODE ‘A RADIO STATION’ IN Q1) 2. Which, if any, of these radio stations have you listened to in the last 7 days? MULTICODE BBC Radio 1 BBC Radio 2 BBC Radio 3 BBC Radio 4 BBC Radio 5 live BBC 6 Music BBC Asian Network BBC Radio 1Xtra BBC Radio 4 Extra BBC Radio 5 live sports extra BBC World Service BBC radio for your nation / region (e.g. -

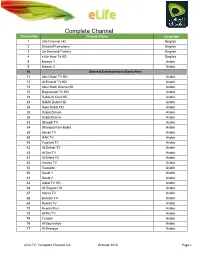

Complete Channel List October 2015 Page 1

Complete Channel Channel No. List Channel Name Language 1 Info Channel HD English 2 Etisalat Promotions English 3 On Demand Trailers English 4 eLife How-To HD English 8 Mosaic 1 Arabic 9 Mosaic 2 Arabic 10 General Entertainment Starts Here 11 Abu Dhabi TV HD Arabic 12 Al Emarat TV HD Arabic 13 Abu Dhabi Drama HD Arabic 15 Baynounah TV HD Arabic 22 Dubai Al Oula HD Arabic 23 SAMA Dubai HD Arabic 24 Noor Dubai HD Arabic 25 Dubai Zaman Arabic 26 Dubai Drama Arabic 33 Sharjah TV Arabic 34 Sharqiya from Kalba Arabic 38 Ajman TV Arabic 39 RAK TV Arabic 40 Fujairah TV Arabic 42 Al Dafrah TV Arabic 43 Al Dar TV Arabic 51 Al Waha TV Arabic 52 Hawas TV Arabic 53 Tawazon Arabic 60 Saudi 1 Arabic 61 Saudi 2 Arabic 63 Qatar TV HD Arabic 64 Al Rayyan HD Arabic 67 Oman TV Arabic 68 Bahrain TV Arabic 69 Kuwait TV Arabic 70 Kuwait Plus Arabic 73 Al Rai TV Arabic 74 Funoon Arabic 76 Al Soumariya Arabic 77 Al Sharqiya Arabic eLife TV : Complete Channel List October 2015 Page 1 Complete Channel 79 LBC Sat List Arabic 80 OTV Arabic 81 LDC Arabic 82 Future TV Arabic 83 Tele Liban Arabic 84 MTV Lebanon Arabic 85 NBN Arabic 86 Al Jadeed Arabic 89 Jordan TV Arabic 91 Palestine Arabic 92 Syria TV Arabic 94 Al Masriya Arabic 95 Al Kahera Wal Nass Arabic 96 Al Kahera Wal Nass +2 Arabic 97 ON TV Arabic 98 ON TV Live Arabic 101 CBC Arabic 102 CBC Extra Arabic 103 CBC Drama Arabic 104 Al Hayat Arabic 105 Al Hayat 2 Arabic 106 Al Hayat Musalsalat Arabic 108 Al Nahar TV Arabic 109 Al Nahar TV +2 Arabic 110 Al Nahar Drama Arabic 112 Sada Al Balad Arabic 113 Sada Al Balad -

Content-Based Recommendations for Radio Stations with Deep Learned Audio Fingerprints

Herausgeber et al. (Hrsg.): Informatik 2020, Lecture Notes in Informatics (LNI), Gesellschaft für Informatik, Bonn 2020 1 Content-based Recommendations for Radio Stations with Deep Learned Audio Fingerprints Stefan Langer ,1 Liza Obermeier ,2 André Ebert ,3 Markus Friedrich ,4 Emma Munisamy ,5 Claudia Linnhoff-Popien 6 Abstract: The world of linear radio broadcasting is characterized by a wide variety of stations and played content. That is why finding stations playing the preferred content is a tough task for a potential listener, especially due to the overwhelming number of offered choices. Here, recommender systems usually step in but existing content-based approaches rely on metadata and thus are constrained by the available data quality. Other approaches leverage user behavior data and thus do not exploit any domain-specific knowledge and are furthermore disadvantageous regarding privacy concerns. Therefore, we propose a new pipeline for the generation of audio-based radio station fingerprints relying on audio stream crawling and a Deep Autoencoder. We show that the proposed fingerprints are especially useful for characterizing radio stations by their audio content and thus are an excellent representation for meaningful and reliable radio station recommendations. Furthermore, the proposed modules are part of the HRADIO Communication Platform, which enables hybrid radio features to radio stations. It is released with a flexible open source license and enables especially small- and medium-sized businesses, to provide customized and high quality radio services to potential listeners. Keywords: Hybrid Radio, Multimedia Services, Recommender Systems, Unsupervised Learning, Deep Audio Fingerprints, Deep Learning 1 Introduction Despite emerging competition from on-demand content services, linear radio broadcasting still remains one of the most popular entertainment and information media in Europe. -

Optical Studies of Massive X-Ray Binaries" Door E.J

C 7A OPTICAL STUDIES OF SIVE m EJ. ZUIDERWIJK optical studies of massive X- ray binaries ACADEMISCH PROEFSCHRIFT TER VERKRIJGING VAN DE GRAAD VAN DOCTOR IN DE WISKUNDE EN NATUURWETENSCHAPPEN AAN DE UNIVERSITEIT VAN AMSTERDAM, OP GEZAG VAN DE RECTOR MAGNIFICUS, DR. J. BRUYN, HOOGLERAAR IN DE FACULTEIT DER LETTEREN, IN HET OPENBAAR TE VERDEDIGEN IN DE AULA DER UNIVERSITEIT (TIJDELIJK IN DE LUTHERSE KERK, INGANG SINGEL 411, HOEK SPUI) OP WOENSDAG 20 JUN11979 DES NAMIDDAGS TE 15.00 UUR PRECIES DOOR EDUARDUSJOSEPHUSZUIDERWIJK GEBOREN TE HAARLEM PROMOTOR : Prof. Dr. E.P.J. van den Heave 1 COREFERENT : Dr. H.G L.M. Lamers The work described in this thesis was supported by the "Netherlands Organi- sation for the advancement of Pure Re- search" (ZWO) and by the University of of Amsterdam. -\ Voor mijn Iet en onze Ouders i Na het voltooien van mijn proefschrift wil ik graag allen bedanken die aan het tot stand komen ervan hebben bijgedragen. Allereerst dank ik mijn ouders, die mij de gelegenheid gaven een aca- demische opleiding te volgen. Bijzonder erkentelijk ben ik mijn Promotor Prof. Dr. E.P.J. van den Heuvel, die het voor mij mogelijk maakte het onderzoek uit te voeren. Hij is daarbij altijd een steun geweest door de interesse getoond in mijn werk, die onder andere tot uiting kwam in langdurige en diepgaande gedach- tenwisselingen. De coreferent Dr. H.J.G.L.M. Lamers dank ik voor het kritisch lezen van het proefschrift. Het grootste deel van de in mijn proefschrift verwerkte publicaties zijn tot stand gekomen in nauwe samenwerking met mijn collega's van het Sterrenkundig Instituut van de universiteit van Amsterdam en van het As- trophysisch Instituut van de Vrije Universiteit van Brussel. -

At South Carolina (2-6) ----- Carolina Game Notes

#13/10 GEORGIA (5-2) AT SOUTH CAROLINA (2-6) ----- CAROLINA GAME NOTES ON THE AIR 2020 SOUTH CAROLINA SCHEDULE TELEVISION National Broadcast ............................. SEC Network vs #16/21 TENNESSEE VOLUNTEERS: Sept. 26 - 7:30 pm ET - SECN Final: UT 31; SC 27 Play-by-Play .................................................. Taylor Zarzour Analyst ......................................................Matt Stinchcomb Williams-Brice Stadium (77,559), Columbia, S.C. SC Record: 0-1 Sideline ..................................................................Alyssa Lang Vols use 2 turnovers, including a pick-6, and hold off Gamecocks Attend: 15,009 RADIO Gamecock IMG Sports Network at #3/3 FLORIDA GATORS: Oct. 3 - Noon ET - ESPN Final: UF 38; SC 24 Play-by-Play ........................................................Derek Scott Ben Hill Griffin Stadium (88,548), Gainesville, Fla. SC Record: 0-2 Analyst ............................................................. Tommy Suggs Trask throws for 268 yards and 4 scores as Gators outscore Gamecocks Attend: 15,120 Sideline .............................................................. Jamar Nesbit National Radio ....................................................ESPN at VANDERBILT COMMODORES: Oct. 10 - Noon ET - SECN Final: SC 41; VU 7 Play-by-Play ........................................................ Sean Kelley Vanderbilt Stadium (39,773), Nashville, Tenn. : 1-2 Analyst ............................................................... Barrett Jones SC Record Harris runs for 171 yards as Gamecocks -

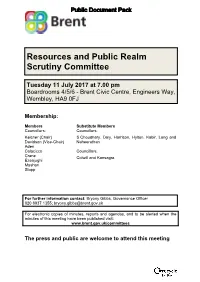

(Public Pack)Agenda Document for Resources and Public Realm

Resources and Public Realm Scrutiny Committee Tuesday 11 July 2017 at 7.00 pm Boardrooms 4/5/6 - Brent Civic Centre, Engineers Way, Wembley, HA9 0FJ Membership: Members Substitute Members Councillors: Councillors: Kelcher (Chair) S Choudhary, Daly, Harrison, Hylton, Kabir, Long and Davidson (Vice-Chair) Naheerathan Aden Colacicco Councillors: Crane Colwill and Kansagra Ezeajughi Mashari Stopp For further information contact: Bryony Gibbs, Governance Officer 020 8937 1355; [email protected] For electronic copies of minutes, reports and agendas, and to be alerted when the minutes of this meeting have been published visit: www.brent.gov.uk/committees The press and public are welcome to attend this meeting Notes for Members - Declarations of Interest: If a Member is aware they have a Disclosable Pecuniary Interest* in an item of business, they must declare its existence and nature at the start of the meeting or when it becomes apparent and must leave the room without participating in discussion of the item. If a Member is aware they have a Personal Interest** in an item of business, they must declare its existence and nature at the start of the meeting or when it becomes apparent. If the Personal Interest is also a Prejudicial Interest (i.e. it affects a financial position or relates to determining of any approval, consent, licence, permission, or registration) then (unless an exception at 14(2) of the Members Code applies), after disclosing the interest to the meeting the Member must leave the room without participating in discussion of the item, except that they may first make representations, answer questions or give evidence relating to the matter, provided that the public are allowed to attend the meeting for those purposes. -

Issue 385 of Ofcom's Broadcast and on Demand Bulletin

Issue 385 of Ofcom’s Broadcast and On Demand Bulletin 27 August 2019 Issue number 385 27 August 2019 Issue 385 of Ofcom’s Broadcast and On Demand Bulletin 27 August 2019 Contents Introduction 3 Notice of Sanction Autonomous Non-profit Organisation TV-Novosti 5 Broadcast Standards cases In Breach The No Repeat 9 to 5 on Sam FM Sam FM Bristol, 20 May 2019, 12:34 7 Journey for Iqra Iqra Bangla, 28 March 2019, 20:00 9 Resolved The Music Marathon Gold, 27 May 2019, 12:45 15 Advertising Scheduling cases In Breach Advertising minutage ATN Bangla UK, various dates between 27 January 2019 and 10 March 2019 19 Advertising minutage Sony Entertainment Television, various dates between 24 February 2019 and 14 April 2019 20 Broadcast Licence Conditions cases In Breach Providing a service in accordance with ‘Key Commitments’ EAVA FM, St Mathews Community Solution Centre Ltd, 6 to 12 May 2019 22 Retention and production of recordings ATN Bangla UK, ATN Bangla UK Limited 25 Tables of cases Complaints assessed, not investigated 27 Complaints outside of remit 38 BBC First 40 Investigations List 42 Issue 385 of Ofcom’s Broadcast and On Demand Bulletin 27 August 2019 Introduction Under the Communications Act 2003 (“the Act”), Ofcom has a duty to set standards for broadcast content to secure the standards objectives1. Ofcom also has a duty to ensure that On Demand Programme Services (“ODPS”) comply with certain standards requirements set out in the Act2. Ofcom reflects these requirements in its codes and rules. The Broadcast and On Demand Bulletin reports on the outcome of Ofcom’s investigations into alleged breaches of its codes and rules, as well as conditions with which broadcasters licensed by Ofcom are required to comply.