Upd78p018f (A) DS

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Integrated Report 2018 1

Integrated Report 2018 1 The latest information on the Maxell Group can be found on our website. Editorial Policy This report is issued for the purpose of sharing the vision of the Maxell Group, where business is based on harmonious coexistence with society. This is an integrated report that goes over the Group’s businesses and financial results as well as its CSR activities and the outcomes of these activities. This report, in the wake of the Maxell Group’s transition to a holding company in October 2017, is aimed at renewing stakeholders’ under- standing of the strengths of the new Maxell Group, the overall vision and specific measures of its new Mid-Term Plan, and the connection between both CSV business management and CSR activities and our business strategy, which is geared toward sustainable growth. The Group has worked hard to win support for its position on co-creation and co-prosperity as well as to foster anticipation for and confidence in the Group’s growth, and will continue to do so. Moreover, we include ESG information, which forms the foun- dation of corporate management, as a way to fulfill our social responsibility to all stakeholders and demonstrate the Maxell Group’s stance toward corporate governance, protection of the global environment, and social contributions. Detailed financial and CSR-related information that could not be Regarding Support for Disasters in published in full in this report is disclosed on the Company’s website. For Viewing via PDF Summer 2018 Category tabs, navigation buttons, and link buttons have been provided on each page for easy access to related pages and websites. -

2SK3446 Datasheet

To our customers, Old Company Name in Catalogs and Other Documents On April 1st, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding. Renesas Electronics website: http://www.renesas.com April 1st, 2010 Renesas Electronics Corporation Issued by: Renesas Electronics Corporation (http://www.renesas.com) Send any inquiries to http://www.renesas.com/inquiry. Notice 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website. 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others. 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. -

Internal Round Table Discussion: the Potential of the Field Solutions Business

Internal Round Table Discussion: The Potential of the Field Solutions Business Our field solutions (FS) business undertakes the maintenance, repair, and modification of semiconductor production equipment supplied by the TEL Group to customers, and until now responsibility for these business activities was spread over multiple organizations, including post-sales divisions. In October 2009 these activities were unified and our FS business launched. Employees involved in this area conducted a round table discussion of the potential for FS business (the discussion was held on June 28, 2010). Generating innovation in the FS business local situations and creating ideas independently. Asano: I feel that the equipment modification business, Moderator: Business models in the world are changing which was inactive only a few years ago, has really changed. dramatically. From now on not only cutting-edge but also Our company is now calling this a period of innovation and low-cost and other numerous semiconductor applications growth. In the FS business, too, we intend to construct new are going to become necessary, especially when aiming business models and generate innovation. at developing countries. Is there a relationship between Sakamoto: I think that one way to generate innovation is the background to these times and the launching of the FS through interpersonal communication. By expanding our business? FS business, our close communication with customers has Kaminaga: In our FS business, the entire TEL Group is become livelier than ever before and this has promoted responding to the polarization of the market into competing innovation. Moreover, by making use of the broad knowledge with cutting-edge technology and effectively utilizing existing and know-how we have accumulated in developing both devices and production lines through the sale of TEL-certified hardware and software, we provide consulting services for used equipment and other efforts. -

Japanese Semiconductor Manufacturing

+44 20 8123 2220 [email protected] Japanese Semiconductor Manufacturing Industry Development and Strategies of Key Players https://marketpublishers.com/r/JE397FCA2F5EN.html Date: August 2019 Pages: 29 Price: US$ 1,260.00 (Single User License) ID: JE397FCA2F5EN Abstracts The Japanese semiconductor industry, which previously operated under the IDM (Integrated Device Manufacturer) model, not only was a leader in Asia, but also had a unprecedented role in the world. After many years passed, Japan was too slow to adjust to structural changes in the industry, causing it to gradually lose its edge. This report covers the current status and future development of the industry as it gears itself towards new application markets such as autonomous vehicles and explores strategies of key players, including Toshiba, Panasonic, Fujitsu, Renesas Electronics, and Sony. Japanese Semiconductor Manufacturing Industry Development and Strategies of Key Players +44 20 8123 2220 [email protected] Contents 1.INDUSTRY STATUS 1.1 Toshiba is the Only Japan’s Semiconductor Brand Left on Top 10 Player List 2. DEVELOPMENT OF JAPAN'S KEY PLAYERS 2.1 Toshiba 2.1.1 Japan’s No. 1 Semiconductor Manufacturer, Ranked 8th in the World 2.1.2 NAND Flash is Toshiba’s Main Semiconductor Revenue Source 2.1.3 Toshiba Memory Corporation (TMC) Spun off to Fix Accounting Issues 2.2 Panasonic 2.2.1 Missed Market Changes, Poor Operations, No Longer a Top-ranked Company 2.2.2 Tightening Belts to Focus on Sensors 2.3 Fujitsu 2.3.1 Ranked 20th in the World, with no Standout -

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan Shozo Saito Chairman, ISSM2020 Organizing Committee Device & System Platform Development Center Co., Ltd. Shuichi Inoue, ATONARP INC. It is our great pleasure to announce that The 28th annual International Symposium on Semiconductor Manufacturing (ISSM) 2020 will be held on December 15-16, 2020 at KFC Hall, Ryogoku, Tokyo in cooperation with e-Manufacturing & Design Collaboration Symposium (eMDC) which is sponsored by TSIA with support from SEMI and GSA. The program will feature keynote speeches by world leading speakers, timely and highlighted topics and networking sessions focusing on equipment/materials/software/services with suppliers' exhibits. ISSM continues to contribute to the growth of the semiconductor industry through its infrastructure for networking, discussion, and information sharing among the world's professionals. We would like you to cooperate with us by supporting the ISSM 2020. Please see the benefit of ISSM2020 sponsorship. Conference Overview Date: December 15-16, 2020 Location: KFC (Kokusai Fashion Center) Hall 1-6-1 Yokoami Sumidaku, Tokyo 130-0015 Japan +81-3-5610-5810 Co-Sponsored by: IEEE Electron Devices Society Minimal Fab Semiconductor Equipment Association of Japan (SEAJ) Semiconductor Equipment and Materials International (SEMI) Taiwan Semiconductor Industry Association (TSIA) Endorsement by: The Japan Society of Applied Physics Area of Interest: Fab Management Factory Design & Automated Material -

Renesas Electronics Announces Share Issue Through Third-Party Allotment, and Change in Major Shareholders, Largest Shareholder W

Renesas Electronics Announces Share Issue through Third-Party Allotment, and Change in Major Shareholders, Largest Shareholder who is a Major Shareholder, Parent Company and Other Related Companies TOKYO, Japan, December 10, 2012 – Renesas Electronics Corporation (TSE: 6723, hereafter “Renesas” or “the Company”), a premier supplier of advanced semiconductor solutions, at a meeting of the board of directors held today, resolved to issue shares through Third-Party Allotment to The Innovation Network Corporation of Japan (“INCJ”), Toyota Motor Corporation, Nissan Motor Co., Ltd., Keihin Corporation, Denso Corporation, Canon Inc., Nikon Corporation, Panasonic Corporation and Yaskawa Electric Corporation, and (hereafter the “scheduled subscribers”). In implementing the Third-Party Allotment, one of the scheduled subscribers, INCJ, is required to file for regulatory approval in relation to business mergers with competition authorities in various countries, and the payment pertaining to the Allotment of Third Party Shares is subject to approval from all the applicable regulatory authorities. Furthermore, implementation of the Third-Party Allotment will result in changes to major shareholders, the largest shareholder who is a major shareholder, the parent company and other related companies, as outlined herein. I. Outline of the Third-Party Allotment 1. Outline of the offering February 23, 2013 through September 30, 2013 (Note 1) The above schedule takes into account the time required by the competition authorities of each country where INCJ, one of the (1) Issue period scheduled subscribers, files application, to review the Third-Party Allotment. Payment for the following total of shares is to be made promptly by the scheduled subscribers after approval from all applicable antitrust authorities, etc. -

Notice of Certification/Authorization and Settlement Approval Hearings Regarding National Settlement Agreements with Hynix, Mitsubishi/Renesas, Cypress, Toshiba and Etron

NOTICE OF CERTIFICATION/AUTHORIZATION AND SETTLEMENT APPROVAL HEARINGS REGARDING NATIONAL SETTLEMENT AGREEMENTS WITH HYNIX, MITSUBISHI/RENESAS, CYPRESS, TOSHIBA AND ETRON IN THE MATTER OF SRAM (STATIC RANDOM ACCESS MEMORY) CLASS ACTION LITIGATION READ THIS NOTICE CAREFULLY. IT MAY AFFECT YOUR LEGAL RIGHTS. TO: All Persons in Canada who purchased Static Random Access Memory (“SRAM”) or products containing SRAM, between January 1, 1998 through December 31, 2005, except for the defendants or parties related to a defendant (“Settlement Class”). NATURE OF LAWSUITS SRAM is a type of memory commonly used in computers, mobile phones and other hand held communication devices. Class action proceedings were commenced in Ontario (Court File No. CV-08-0035836800CP, Toronto Registry), British Columbia (Court File No. S-070350, Vancouver Registry), and Quebec (Court File No. 200-06-000083-074, District of Quebec) alleging that the defendants, conspired to fix prices in the market for SRAM (collectively the "SRAM Proceedings"). The plaintiffs on behalf of themselves and the classes are claiming damages from the defendants for unlawfully conspiring to fix, maintain or increase the price of SRAM. The defendants include: Samsung Electronics Co. Ltd., Samsung Semiconductor, Inc. and Samsung Electronics Canada Inc. (”Samsung’), Hynix Semiconductor, Inc. and Hynix Semiconductor America, Inc. (“Hynix”), Micron Technology, Inc., Micron Semiconductor Canada and Micron Semiconductor Products, Inc.(“Micron”), Cypress Semiconductor Corporation and Cypress Semiconductor, Inc. (“Cypress”), Etron Technology Inc. and Etron Technology America, Inc. (“Etron”), Mitsubishi Electric Corporation, Mitsubishi Electric Sales Canada Inc., Mitsubishi Electric & Electronics USA, Inc., Renesas Electronics Corporation fka Renesas Technology Corporation, Renesas Electronics Canada Limited fka Renesas Technology Canada Limited, Renesas Electronics America Inc. -

ENVIRONMENTAL REPORT 2017 Contents CONTENTS How to Each Page in This Report Contains Navigation Buttons and Category Tabs to Make It Easy to Move from Page to Page

Renesas Electronics ENVIRONMENTAL REPORT 2017 Contents CONTENTS How to Each page in this report contains navigation buttons and category tabs to make it easy to move from page to page. Use Contents/Editorial Policies 1 ■ Category tab Top Message 2 Contents/Editorial Policies/ Go to top page in each category. (Corporate Outline) How to Use/Editorial Policies Renesas Electronics Group EnvironmentalTop Message Measures 3 Eco-Management Initiative 5 Renesas Electronics Group Eco-FactoriesEnvironmental Initiative Measures 7 Eco-Products Initiative 12 Eco-Management Initiative ■ Link button Eco-Communication Initiative 15 European RoHS initiatives OpinionEco-Factories exchange Initiative meeting with Fujitsu Limited 17 https://www.renesas.com/en-eu/support/products-common/lead/rohs.html Links to site outside of the report. Eco-Products Initiative ■ Navigation button Eco-Communication Initiative Go back one page. Opinion exchange meeting Go forward one page. with Fujitsu Limited Editorial Policies Reporting Scope This Environmental Report is intended for the many stakeholders of the Renesas The report covers the Renesas Electronics Group, which consists of Renesas Electronics Electronics Group, including employees, customers, members of the local communities Corporation, 5 domestic Group companies and 22 overseas Group companies. where we conduct business, suppliers, partners, shareholders and investors. With the In this Environmental Report, we use the fiscal year, which ends on the last day of March objective of promoting two-way communication between the Company and these until FY 2015. Note that from 2016 is a period of transition for International Accounting stakeholders, this report explains our approach to the environment and illustrates our Standards. Refer to the example below. -

PANJIT International Inc

PANJIT International Inc Power Semiconductor ! Copyright© 2021 PANJIT International Inc. All rights reserved. !"#$%% &'&( n About PANJIT n New Team n Financial Info n New Technology " Copyright© 2021 PANJIT International Inc. All rights reserved. About PANJIT 3 Copyright© 2021 PANJIT International Inc. All rights reserved. PANJIT Group PANJIT International Inc. PYNMAX Technology Inc. MILDEX Optoelectronics Inc. Est. 1986.05 Est. 2000.03 Est. 2005.05 Product: Discrete Packaging & Testing Product: Wafer Foundry Product: Touch Screen # Copyright© 2021 PANJIT International Inc. All rights reserved. Wafer & Assembly Capacity Wafer Capacity Assembly Capacity PYNMAX Kaohsiung, Taiwan PANJIT Kaohsiung, Taiwan n 4”/5”/6” EPI Wafer: 70,000 pcs/month Package: n 5”/6” Schottky Wafer: 50,000 pcs/month Small Signal Devices/SMD Bridge n 6” ESD/TVS Wafer: 3,000 pcs/month Capacity: n 6” ZENER Wafer: 3,000 pcs/month 2,100 KK /month n 8” wafer: In construction PANJIT Shandong, China PANJIT Wuxi, China n 4” ESD/TVS Wafer: 25,000 pcs/month Package: Power Package Devices Capacity: 400 KK /month $ Copyright© 2021 PANJIT International Inc. All rights reserved. PANJIT Overview PANJIT International Inc. is a leading global manufacturer dedicating in supplying high Market Segments quality semiconductors, serving the consumer, green power, industrial, automotive, communication and computing segments. Automotive 12% n Capital : NTD $3.3 Billion Consumer Industrial 30% n TWSE : 2481 (2001 IPO) 14% !"#$%&!"# n Approximately 2,500 employees worldwide !"!"#$%&%'(% n 2 front-end fabrication sites Green Power 19% Computing 21% n 2 back-end manufacturing sites Communication 4% Establish Launched Full range of Launched Super HQ in Wuxi factory Small Signal product MOSFET in IATF16949: 2016 IBU 8” Key process Schottky series Gangshan Pynmax (FE) PANJIT IPO development certificated R&D center foundry 1986 2000 2001 2012 2013 2018 2019 2020 % Copyright© 2021 PANJIT International Inc. -

Renesas Starter Kit+ for SH7267 Software Manual

YRSPSH7267-0103 Renesas Starter Kit for SH7267 Software Manual RENESAS SINGLE-CHIP MICROCOMPUTER SuperH FAMILY Rev.1.0 Renesas Electronics America . Revision date: 12 May 2012 www.renesas.com Disclaimer This software is supplied by Renesas Corp. and is only intended for use with Renesas products. No other uses are authorized. This software is owned by Renesas Corp. and is protected under all applicable laws, including copyright laws. THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY DISCLAIMED. TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Renesas reserves the right, without notice, to make changes to this software and to discontinue the availability of this software. By using this software, you agree to the additional terms and conditions found by accessing the following link: http://www.renesas.com/disclaimer ii Table of Contents Chapter 1. Preface .................................................................................................................................................. 1 Chapter 2. Introduction........................................................................................................................................... -

Leading Optical Chip and Module Manufacturers Announce New Pluggable Transceiver Module Multi-Source Agreement for 40 Gbps Solution with an Optical Device (XLMD2)

FOR IMMEDIATE RELEASE Leading Optical Chip and Module Manufacturers Announce New Pluggable Transceiver Module Multi-Source Agreement for 40 Gbps Solution with an Optical Device (XLMD2) Fremont, CA—July 27, 2011—Mitsubishi Electric Corporation, OKI SEMICONDUCTOR CO., LTD., Opnext, Inc., Renesas Electronics Corporation and Sumitomo Electric Industries, Ltd., today announced a transmitter optical sub-assembly (TOSA) and receiver optical sub-assembly (ROSA) Multi-Source Agreement (MSA) for 40 Gbps pluggable transceiver modules. This initiative was established to meet increased demand for pluggable 40 Gbps serial modules, similar to the CFP MSA.(*1). In an upcoming MSA meeting, the member companies will specify the common mechanical dimensions, footprint, pin functions and performance of the optical transmitter and receiver devices. The TOSA/ROSA MSA specifies key features including a low-profile and compact fit for pluggable modules and simple electrical interfaces that provide cost effective solutions. The transmission speed of 40 Gbps is the highest modulation speed, commercially-available, that uses the simple light on/off keying or serial transmission scheme. 300-pin MSA (*2) transceivers using 1550 nm light source devices are widely available for the 2 km application. Recently, 40 Gbps serial transmission over 10 km was demonstrated using 1310 nm light source devices. In addition to ITU-T 40Gbps serial transmission standards: VSR2000-3R2 for 2 km and P1I1-3D1 for 10 km (*3), the IEEE has recently defined a 40 Gbps serial interface for 2 km (40GBASE-FR) (*4). The demand for 40Gbps serial transmissions is growing in telecommunication, data and IP communication applications. In today’s 300-pin MSA transceiver module market, XLMD MSA (*5) TOSAs and ROSAs are widely adopted. -

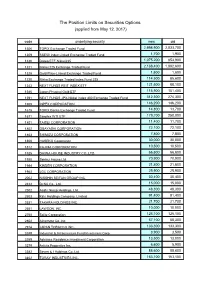

The Position Limits on Securities Options (Applied from May 12, 2017) Code Underlying Security New Old

The Position Limits on Securities Options (applied from May 12, 2017) code underlying security new old 1306 TOPIX Exchange Traded Fund 2,998,900 2,033,700 1309 SSE50 Index Linked Exchange Traded Fund 1,700 1,900 1320 Daiwa ETF-Nikkei225 1,075,200 853,900 1321 Nikkei 225 Exchange Traded Fund 2,168,400 1,882,600 1328 Gold-Price-Linked Exchange Traded Fund 1,600 1,600 1330 Nikko Exchange Traded Index Fund 225 114,500 85,600 1343 NEXT FUNDS REIT INDEX ETF 121,600 88,100 1540 Japan Physical Gold ETF 116,900 101,400 1591 NEXT FUNDS JPX-Nikkei Index 400 Exchange Traded Fund 312,300 274,300 1605 INPEX CORPORATION 146,200 146,200 1615 TOPIX Banks Exchange Traded Fund 14,800 13,700 1671 Simplex WTI ETF 179,700 250,000 1801 TAISEI CORPORATION 11,400 11,700 1802 OBAYASHI CORPORATION 72,100 72,100 1803 SHIMIZU CORPORATION 7,800 7,800 1808 HASEKO Corporation 30,000 30,000 1812 KAJIMA CORPORATION 10,500 10,500 1925 DAIWA HOUSE INDUSTRY CO.,LTD. 66,600 66,600 1928 Sekisui House,Ltd. 70,900 70,900 1944 KINDEN CORPORATION 21,800 21,800 1963 JGC CORPORATION 25,900 25,900 2002 NISSHIN SEIFUN GROUP INC. 30,400 30,400 2432 DeNA Co., Ltd. 15,000 15,000 2502 Asahi Group Holdings, Ltd. 48,300 48,300 2503 Kirin Holdings Company, Limited 91,400 91,400 2531 TAKARA HOLDINGS INC. 21,700 21,700 2651 LAWSON, INC. 10,000 10,000 2768 Sojitz Corporation 125,100 125,100 2802 Ajinomoto Co.,Inc.