AMD Sempron 3000+ Processor CPU Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Family 12H AMD Sempron Processor Product Data Sheet

Family 12h AMD Sempron™ Processor Product Data Sheet Publication # 50321 Revision: 3.00 Issue Date: December 2011 Advanced Micro Devices © 2011 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD Arrow logo, AMD PowerNow!, 3DNow!, AMD Virtualization, AMD-V, Sempron, and combinations thereof are trademarks of Advanced Micro Devices, Inc. -

Communication Theory II

Microprocessor (COM 9323) Lecture 2: Review on Intel Family Ahmed Elnakib, PhD Assistant Professor, Mansoura University, Egypt Feb 17th, 2016 1 Text Book/References Textbook: 1. The Intel Microprocessors, Architecture, Programming and Interfacing, 8th edition, Barry B. Brey, Prentice Hall, 2009 2. Assembly Language for x86 processors, 6th edition, K. R. Irvine, Prentice Hall, 2011 References: 1. Computer Architecture: A Quantitative Approach, 5th edition, J. Hennessy, D. Patterson, Elsevier, 2012. 2. The 80x86 Family, Design, Programming and Interfacing, 3rd edition, Prentice Hall, 2002 3. The 80x86 IBM PC and Compatible Computers, Assembly Language, Design, and Interfacing, 4th edition, M.A. Mazidi and J.G. Mazidi, Prentice Hall, 2003 2 Lecture Objectives 1. Provide an overview of the various 80X86 and Pentium family members 2. Define the contents of the memory system in the personal computer 3. Convert between binary, decimal, and hexadecimal numbers 4. Differentiate and represent numeric and alphabetic information as integers, floating-point, BCD, and ASCII data 5. Understand basic computer terminology (bit, byte, data, real memory system, protected mode memory system, Windows, DOS, I/O) 3 Brief History of the Computers o1946 The first generation of Computer ENIAC (Electrical and Numerical Integrator and Calculator) was started to be used based on the vacuum tube technology, University of Pennsylvania o1970s entire CPU was put in a single chip. (1971 the first microprocessor of Intel 4004 (4-bit data bus and 2300 transistors and 45 instructions) 4 Brief History of the Computers (cont’d) oLate 1970s Intel 8080/85 appeared with 8-bit data bus and 16-bit address bus and used from traffic light controllers to homemade computers (8085: 246 instruction set, RISC*) o1981 First PC was introduced by IBM with Intel 8088 (CISC**: over 20,000 instructions) microprocessor oMotorola emerged with 6800. -

SCAPP Package Spectrum CUDA Access for Parallel Programming

SCAPP Package Spectrum CUDA Access for Parallel Programming for M4i and M2p cards, English version April 12, 2019 SPECTRUM INSTRUMENTATION GMBH · AHRENSFELDER WEG 13-17 · 22927 GROSSHANSDORF · GERMANY PHONE: +49 (0)4102-6956-0 · FAX: +49 (0)4102-6956-66 · E-MAIL: [email protected] · INTERNET: www.spectrum-instrumentation.com (c) SPECTRUM INSTRUMENTATION GMBH AHRENSFELDER WEG 13-17, 22927 GROSSHANSDORF, GERMANY SBench, digitizerNETBOX and generatorNETBOX are registered trademarks of Spectrum Instrumentation GmbH. Microsoft, Visual C++, Windows, Windows 98, Windows NT, Windows 2000, Windows XP, Windows Vista, Windows 7, Windows 8, Windows 10 and Windows Server are trademarks/registered trademarks of Microsoft Corporation. LabVIEW, DASYLab, Diadem and LabWindows/CVI are trademarks/registered trademarks of National Instruments Corporation. MATLAB is a trademark/registered trademark of The Mathworks, Inc. Delphi and C++Builder are trademarks or registered trademarks of Embarcadero Technologies, Inc. Keysight VEE, VEE Pro and VEE OneLab are trademarks/registered trademarks of Keysight Technologies, Inc. FlexPro is a registered trademark of Weisang GmbH & Co. KG. PCIe, PCI Express, PCI-X and PCI-SIG are trademarks of PCI-SIG. PICMG and CompactPCI are trademarks of the PCI Industrial Computation Manufacturers Group. PXI is a trademark of the PXI Systems Alliance. LXI is a registered trademark of the LXI Consortium. IVI is a registered trademark of the IVI Foundation Oracle and Java are registered trademarks of Oracle and/or its affiliates. Intel and Intel Core i3, Core i5, Core i7, Core i9 and Xeon are trademarks and/or registered trademarks of Intel Corporation. AMD, Opteron, Sempron, Phenom, FX, Ryzen and EPYC are trademarks and/or registered trademarks of Advanced Micro Devices. -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

Processor Check Utility for 64-Bit Compatibility

Processor Check Utility for 64-Bit Compatibility VMware Workstation Processor Check Utility for 64-Bit Compatibility VMware Workstation version 5.5 supports virtual machines with 64-bit guest operating systems, running on host machines with the following processors: • AMD™ Athlon™ 64, revision D or later • AMD Opteron™, revision E or later • AMD Turion™ 64, revision E or later • AMD Sempron™, 64-bit-capable revision D or later (experimental support) • Intel™ EM64T VT-capable processors (experimental support) When you power on a virtual machine with a 64-bit guest operating system, Workstation performs an internal check: if the host CPU is not a supported 64-bit processor, you cannot power on the virtual machine. VMware also provides this standalone processor check utility, which you can use without Workstation to perform the same check and determine whether your CPU is supported for virtual machines with 64-bit guest operating systems. Note: On hosts with EM64T VT-capable processors, you may not be able to power on a 64-bit guest, even though the processor check utility indicates that the processor is supported for 64- bit guests. VT functionality can be disabled via the BIOS, but the processor check utility cannot read the appropriate model-specific register (MSR) to detect that the VT functionality has been disabled in the BIOS. Note: In shopping for a processor that is compatible with Workstation 5.5 64-bit guests, you may be unable to determine the revision numbers of a given vendor's offering of AMD Athlon 64, Opteron, Turion 64, or Sempron processors. At this time, the only reliable way to determine whether any of these processors is a revision supported by Workstation 5.5, is by the manufacturing technology (CMOS): any of the AMD Athlon 64, Opteron, Turion 64, or Sempron processors whose manufacturing technology is 90nm SOI (.09 micron SOI) is compatible with Workstation 5.5 64-bit guests. -

AMD in Embedded: Proven Leadership and Solutions

AMD in Embedded: Proven Leadership and Solutions A long history of high-performance low-power solutions for embedded applications For over two decades AMD has been a leader in the embedded market: in the early 1990’s with the introduction of the Am386 and Am486 and their adoption in embedded designs, and followed in 1995 with the introduction of the Am5x86 processor. The AM5x86 processor was one of the fastest and most universally-compatible upgrade paths for users of 486 systems when it was introduced. AMD continued to expand their E86 (Embedded x86) product family in the late 90’s with the release of the Élan™SC520 microcontroller for data communications, telecommunications, and information appliance markets. The ÉlanSC520 microcontroller extended the options available to embedded systems designers by providing fifth-generation x86 performance and was designed to run both 16-bit and 32-bit software. The AMD embedded group grew significantly in early 2000 with the acquisition of Alchemy Semiconductor for its Alchemy line of MIPS processors for the hand-held and portable media player markets. In order to augment its existing line of embedded x86 processor products, AMD also purchased the AMD Geode™ business in August 2003 which was originally part of National Semiconductor. During the second quarter of 2004, AMD launched the new low- power AMD Geode™ NX processors which were based on the AMD-K7™ Thoroughbred architecture with speeds up to 1.4 GHz. These AMD Geode NX processors offered a high performance option in the AMD Geode product line that was still sufficiently low power to be designed into fan-less applications. -

AMD Sempron™ Processor Product Brief

AMD Sempron™ Processor Product Brief AMD Sempron™ Processor Overview The AMD Sempron™ processor performs at the top of its class when running the home and business applications that you need most. The AMD Sempron™ processor’s full-featured capabilities can include HyperTransport™ technology, up to 512k total high-performance cache, advanced 333Mhz front-side bus, 3DNow! Professional technology, and an integrated DDR memory controller. The AMD Sempron™ processor provides the productivity enhancing performance you need for your everyday applications. It runs over 60,000 of the world’s most popular applications, so you can enjoy solid performance. With 35 years of design and manufacturing experience and shipments of more than 240 million PC processors, you can count on AMD to provide reliable solutions for your home or business. Best-in-class Performance • The AMD Sempron processor performs at the top of its class on the home and business applications that you need most. • The AMD Sempron processor is designed for day-to-day computing and beyond. Full-Featured to Improve your Computing Experience • The AMD Sempron processor lets you enjoy a dynamic Internet experience with smooth streaming video and audio. • The AMD Sempron processor saves you time and effort; enabling your system to boot and load your applications quickly. • Applications that allow you to communicate with family, friends and colleagues will run smoothly with the AMD Sempron processor. The AMD Sempron™ processor’s advanced architectural features help ensure best-in-class -

![CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU](https://docslib.b-cdn.net/cover/8530/cpu-history-tualatin-banias-dothan-yonah-jonah-conroe-allendale-yorkfield-xe-intel-created-pentium-from-quad-core-cpu-3058530.webp)

CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU

2nd Generation 4th Generation 5th Generation 6th Generation 7th Generation 3rd Generation Intel Pentium III-S Intel Pentium-M (Centrino) Intel Pentium-M (Centrino) Intel Core Duo (Viiv) Intel Core 2 Duo (Viiv)/Xeon Intel Core 2 Duo (Viiv) Intel Core 2 Extreme (Viiv) Intel had the first consumer CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel created Pentium (from quad-core CPU. x86/CISC Microprocessors Greek penta which means (2001) (2003) (2004) (2006) (2006) (2007) (2007) 1st Generation Intel Pentium II Xeon Intel Pentium III Xeon Centrino is not a CPU; it is Begin Core five) to distinguish the Intel [P6] [Tanner] a mobile Intel CPU paired nomeclature brand from clones. Names (1998) (1999) Intel Celeron with an Intel Wi-Fi adapter. Intel Celeron Intel Core Solo can be copyrighted, product [Tualeron] [Dothan-1024] Intel Xeon LV Intel Celeron Intel Celeron [Yonah] ID's cannot. (2001) (2004) [Sossaman] [Banias-512] [Shelton (Banias-0)] (2006) (2006) Intel Core 2 Duo Intel Core 2 Extreme Intel Celeron Intel 80386 DX Intel 80486 DX Intel Pentium Intel Pentium Pro Intel Pentium II Intel Pentium II Intel Pentium III Intel Pentium III Intel Pentium 4 Intel Pentium 4 (2004) (2004) Intel Pentium 4 Intel Pentium 4 Intel 4004 Intel 8008 Intel 8086 Intel 80286 [Conroe XE] [Conroe-L] [P3] [P4] [P5/P54/P54C] [P6] [Klamath] [Deuschutes] [Katmai] [Coppermine] [Williamette] [Northwood] [Prescott] [Cedar Mill] END-OF-LINE (Centrino Duo) (1971) (1972) (1978) (1982) (2006) (2007) (1985) (1989) (1993) (1995) (1997) (1998) (1999) (1999) (2000) (2002) (2004) (2006) [Merom] (2006) Yonah is Hebrew for Jonah. -

AMD Family 10H Desktop Processor Power and Thermal Data Sheet

AMD Family 10h Desktop Processor Power and Thermal Data Sheet Publication # 43375 Revision: 3.46 Issue Date: September 2010 Advanced Micro Devices © 2008 – 2010 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The informa- tion contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and dis- claims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as compo- nents in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD Arrow logo, AMD Athlon, AMD Phenom, AMD Sempron, and combinations thereof are trademarks of Advanced Micro Devices, Inc. -

Dnx.46X Manual

digitizerNETBOX DN2.46x-xx DN6.46x-xx Ethernet/LXI remote digitizer with 16 bit resolution Hardware Manual Software Driver Manual English version May 7, 2020 SPECTRUM INSTRUMENTATION GMBH · AHRENSFELDER WEG 13-17 · 22927 GROSSHANSDORF · GERMANY PHONE: +49 (0)4102-6956-0 · FAX: +49 (0)4102-6956-66 · E-MAIL: [email protected] · INTERNET: www.spectrum-instrumentation.com (c) SPECTRUM INSTRUMENTATION GMBH AHRENSFELDER WEG 13-17, 22927 GROSSHANSDORF, GERMANY SBench, digitizerNETBOX and generatorNETBOX are registered trademarks of Spectrum Instrumentation GmbH. Microsoft, Visual C++, Windows, Windows 98, Windows NT, Windows 2000, Windows XP, Windows Vista, Windows 7, Windows 8, Windows 10 and Windows Server are trademarks/registered trademarks of Microsoft Corporation. LabVIEW, DASYLab, Diadem and LabWindows/CVI are trademarks/registered trademarks of National Instruments Corporation. MATLAB is a trademark/registered trademark of The Mathworks, Inc. Delphi and C++Builder are trademarks or registered trademarks of Embarcadero Technologies, Inc. Keysight VEE, VEE Pro and VEE OneLab are trademarks/registered trademarks of Keysight Technologies, Inc. FlexPro is a registered trademark of Weisang GmbH & Co. KG. PCIe, PCI Express, PCI-X and PCI-SIG are trademarks of PCI-SIG. PICMG and CompactPCI are trademarks of the PCI Industrial Computation Manufacturers Group. PXI is a trademark of the PXI Systems Alliance. LXI is a registered trademark of the LXI Consortium. IVI is a registered trademark of the IVI Foundation Oracle and Java are registered trademarks of Oracle and/or its affiliates. Intel and Intel Core i3, Core i5, Core i7, Core i9 and Xeon are trademarks and/or registered trademarks of Intel Corporation. AMD, Opteron, Sempron, Phenom, FX, Ryzen and EPYC are trademarks and/or registered trademarks of Advanced Micro Devices. -

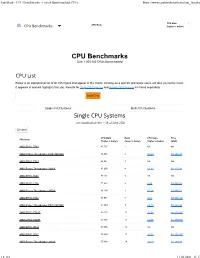

Passmark - CPU Benchmarks - List of Benchmarked Cpus

PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Mark Rank CPU Name CPU Benchmarks (higher is better) (lower is better) CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. Results for Single CPU Systems and Multiple CPU Systems are listed separately. Find CPU Single CPU Systems Multi CPU Systems Single CPU Systems Last updated on the 11th of June 2021 Column CPU Mark Rank CPU Value Price CPU Name (higher is better) (lower is better) (higher is better) (USD) AMD EPYC 7763 87,767 1 NA NA AMD Ryzen Threadripper PRO 3995WX 86,096 2 15.69 $5,486.99 AMD EPYC 7713 85,887 3 NA NA AMD Ryzen Threadripper 3990X 81,290 4 13.30 $6,110.99 AMD EPYC 7643 77,101 5 NA NA AMD EPYC 7702 71,686 6 8.43 $8,499.00 AMD Ryzen Threadripper 3970X 64,139 7 26.28 $2,440.51 AMD EPYC 7742 64,071 8 8.01 $7,995.94* AMD Ryzen Threadripper PRO 3975WX 61,259 9 22.70 $2,698.99 AMD EPYC 7702P 60,273 10 12.96 $4,650.00* AMD EPYC 7443P 58,896 11 44.05 $1,337.00* AMD EPYC 7R32 58,556 12 NA NA AMD EPYC 7542 56,809 13 13.53 $4,198.95* AMD Ryzen Threadripper 3960X 55,004 14 39.29 $1,399.99 1 z 112 11.06.2021, 11:17 PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Mark Rank CPU Value Price CPU Name (higher is better) (lower is better) (higher is better) (USD) CPU Mark Rank CPU Name CPU Benchmarks (higher -

CNPS10X Performa More

CNPS10X Performa More Dual Fan Support Pentium 4, Celeron D, Pentium D, Core 2 Duo, Core 2 Quad, Core 2 Extreme, Pentium Dual Core, Core i7, Core i5, Core i3, Sempron, Athlon, Athlon FX, Opteron, Dual- Core Opteron, Phenom, Athlon X2, Phenom II, Athlon II Socket CPU CPU Compatibility Core i7 1156 Core i5 Supports all speeds Core i3 1366 Core i7 Supports all speeds Core 2 Quad Intel Core 2 Duo Core 2 Extreme 775 Pentium Dual Core Supports all speeds Pentium D Pentium 4 Celeron D Phenom II AM3 Supports all speeds Athlon II Phenom II Phenom Athlon FX AM2+ Supports all speeds Athlon X2 Athlon Sempron Athlon FX Athlon X2 AM2 Supports all speeds Athlon AMD Sempron Dual-Core Opteron 940 Opteron Supports all speeds Athlon FX Dual-Core Opteron Opteron 939 Athlon FX Supports all speeds Athlon X2 Athlon Athlon 754 Supports all speeds Sempron Dimensions 132(L) x 100(W) x 152(H)mm Weight 748g Materials Fins: Aluminum / Base: Copper Dissipation Area 7,900㎠ Heatpipes 5 U-shaped heatpipes Fan 4-Pin 120mm PWM Fan Fan RPM 900~1,350 ±10% (RC24P Connected), 900~2,000 ±10% (RC24P Not Connected) Noise 17~24dBA ±10% (RC24P Connected), 17~36dBA ±10% (RC24P Not Connected) Fan Bearing Long life bearing Color Gray Capacity 1g Temperature Stability -40°C ~ +150°C (-40℉ ~ +302℉) Powerful Cooling Performance Dual Fan Support Optimally designed aluminum fins disperse heat away from the The heatsink is designed to mount one or two fans according CPU via 5 heatpipes, while switching noise free, high capacity to the users preferences.