PS3111-S11 Micro SSD (Μssd) 3D NAND Specification

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Phison's Resilient Business Model Generates Results Through

March 2020 Release EXECUTIVE SUMMARY Phison’s Resilient Business Phison’s diversified revenue contribution flows from a range of NAND applications including consumer, embedded, and Model Generates Results enterprise markets, making Phison less susceptible to global crisis incidents. through Challenging World During cyclical NAND price declines, Phison has demonstrated it can increase market share and unit shipments. Events During cyclical NAND price increases, Phison has demonstrated it can increase margin and revenue. _____________________________________ Over the past 20 years, Phison (TPEx: 8299) has endured the financial crisis of 2008, the cyclicality of NAND industry pricing related to supply and demand, and the introduction of new NAND technologies and emerging applications. Throughout these events, Phison maintained profitability while overcoming the challenges and generating business growth. Though the COVID-19 virus is currently impacting businesses worldwide, Phison continues to leverage its unique and resilient business model to generate results as it has successfully done in the past. PHISON’S BUSINESS MODEL Phison’s business model in Exhibit 1 is straightforward in simplicity but is underlined by massive engineering capability and flexible execution. Peer companies have attempted to study and replicate Phison’s model, but none have been successful to date. Exhibit 1: Phison’s unique business model of differentiated revenue and flexible execution. PHISON ELECTRONICS CORPORATION 1 March 2020 Release This model consists of 2 key elements: 1) NAND controller IC design, and 2) NAND storage module integration. Storage module integration is defined as manufacturing an entire functioning storage device including the controller, NAND and firmware under private labels for our valued customers. -

Phison Electronics Corporation 2016 ANNUAL REPORT

ި౻жዸǺ8299 ဂᖄႝηިҽԖज़Ϧљ Phison Electronics Corporation Ʉϖԃࡋ ԃ ൔ 2016 ANNUAL REPORT ԃൔ၌ᆛ֟ Ϧ໒ၗૻᢀෳઠᆛ֟Ǻhttp://mops.twse.com.tw ҁ Ϧ љ ᆛ ֟Ǻwww.phison.com т ӑ В ය Ǻ ύ ҇ ୯ Ʉ Ϥ ԃ ϖ Д Β Μ Ϥ В Ӝ/ᙍᆀ/ᖄ๎ႝ၉/ႝηແҹߞጃۉΓقz Ϧљว மדӜǺΪ ۉ ᙍ ᆀǺၗుձշ ႝ၉Ǻ(037) 586-896 ext.1019 ႝηແҹߞጃǺ[email protected] Ӝ/ᙍᆀ/ᖄ๎ႝ၉/ႝηແҹߞጃۉΓقz Ϧљжว ਁ۔ӜǺ ۉ ᙍ ᆀǺձշ ႝ၉Ǻ(037) 586-896 ext. 1029 ႝηແҹߞጃǺ[email protected] z ᕴϦљ/ϩϦљ/πቷϐӦ֟Ϸႝ၉ ᕴϦљ Ӧ ֟ǺཥԮᑜԮчѱൺᑫຉ 251 ဦ 10 ኴϐ 6 ႝ၉Ǻ(03)657-9299 ԮࠄϩϦљϷπቷ Ӧ ֟ǺभਪᑜԮࠄᙼဂကၡ 1 ဦϷभਪᑜԮࠄᙼဂကၡ 1-1 ဦ ႝ၉Ǻ(037)586-896 z ި౻ၸЊᐒᄬϐӜᆀ/Ӧ֟/ᆛ֟/ႝ၉ ҽԖज़Ϧљ ި୍жިچӜ ᆀǺֻᇻ Ӧ ֟ǺѠчѱεӼߞကၡѤࢤ 236 ဦ 3 ኴ ᆛ֟Ǻwww.honsec.com.tw ႝ၉Ǻ(02)2326-8818 Ӝᆀ/Ӧ֟/ᆛ֟/ႝ၉܌٣୍/Ӝۉz ന߈ԃࡋ୍ൔᛝीৣ ӜǺᔎߞᆢǵणԖۉीৣ ܌ӜᆀǺ༇ߞᖄӝीৣ٣୍܌٣୍ Ӧ ֟ǺѠчѱ҇ғܿၡΟࢤ 156 ဦ 12 ኴ ᆛ֟Ǻwww.deloitte.com.tw ႝ၉Ǻ(02)2545-9988 ၗૻϐБԄǺคǶچӜᆀϷ၌၀ੇѦԖሽ܌จວ፤ϐҬܰچz ੇѦԖሽ z Ϧљᆛ֟Ǻwww.phison.com ဂᖄႝηިҽԖज़Ϧљ Ʉϖԃࡋԃൔ Ҟ ᒵ ൘ǵठިܿൔਜ........................................................................................................... 1 ǵ 105 ԃࡋᔼ่݀.................................................................................................................... 1 Βǵ 106 ԃࡋᔼीჄཷा............................................................................................................ 3 ѦᝡݾᕉნǵݤೕᕉნϷᕴᡏᔼᕉნϐቹៜ ................... 4ډڙΟǵ ҂ٰϦљวౣǵ ມǵϦљᙁϟ................................................................................................................... 5 ǵ ҥВය................................................................................................................................... 5 Βǵ Ϧљݮॠ.................................................................................................................................. -

Fiscal Year 2020 Form 10-K

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 Form 10-K (Mark One) ☒ ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended February 1, 2020 or ☐ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to Commission file number 0-30877 Marvell Technology Group Ltd. (Exact name of registrant as specified in its charter) Bermuda 77-0481679 (State or other jurisdiction of (I.R.S. Employer incorporation or organization) Identification No.) Canon’s Court, 22 Victoria Street, Hamilton HM 12, Bermuda (Address of principal executive offices) (441) 296-6395 (Registrant’s telephone number, including area code) Securities registered pursuant to Section 12(b) of the Act: Title of each class Trading Symbol Name of each exchange on which registered Common shares, $0.002 par value per share MRVL The Nasdaq Stock Market LLC Securities registered pursuant to Section 12(g) of the Act: None Indicate by check mark if the registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. Yes ☐ No ☒ Indicate by check mark if the registrant is not required to file reports pursuant to Section 13 or Section 15(d) of the Act. Yes ☐ No ☒ Indicate by check mark whether the registrant (1) has filed all reports required to be filed by Section 13 or 15(d) of the Securities Exchange Act of 1934 during the preceding 12 months (or for such shorter period that the registrant was required to file such reports), and (2) has been subject to such filing requirements for the past 90 days. -

Press Release – 28 January 2019 Wibu-Systems Returns to Embedded

Press Release – 28 January 2019 The compound value of collaboration broadens the perspective on the digital transformation Wibu-Systems returns to Embedded World with an incredible lineup of solution partners Karlsruhe, Germany – Wibu-Systems will once again exhibit at Embedded World, the most iconic event for Europe’s embedded community, hosted in Nuremberg, Germany, from February 26th to 28th. The journey starts at Wibu-Systems’ principal booth (4/360) and continues at the OSADL, SD Association, Trusted Computing Group, and Wind River spaces for a fully engaging experience of the world of secure license management applied to electronic systems, distributed intelligence, the Industrial Internet of Things, e-mobility, and energy efficiency. At Wibu-Systems’ main space (Hall 4, booth 360), the company security experts will be focusing specifically on IP protection as a way to prevent attempts to pirate or reverse engineer crucial code and to ultimately ensure the lasting commercial success for businesses everywhere. They will also be sharing several case studies where IP protection was skillfully integrated into modern business models to multiply revenue streams. At the collective exhibit of OSADL, the Open Source Automation Development Lab (Hall 4, booth 168), embedded software developers will be laying out the importance of monetizing digital know-how and raising the quality of their code. Wibu-Systems, who affiliated with OSADL a couple of years ago, will join forces with them to provide their combined expertise and services to the entire OSADL community. Together with ATP, Delkin, GRL, Hagiwara, JMicron, Micron, Phison, Swissbit, Toshiba, and WD, Wibu-Systems will also present some of WIBU-SYSTEMS AG Page 1 Press Release – 28 January 2019 its many hardware secure elements at the SD Association’s group exhibit (Hall 3A, booth 524). -

FOR IMMEDIATE RELEASE Wibu‐Systems to Expand Its Presence

FOR IMMEDIATE RELEASE Wibu‐Systems to Expand its Presence at Embedded World 2019 in Close Collaboration with Solution Partners The company to focus on secure license management and IP protection January 24, 2019 ‐ Edmonds, WA – Wibu‐Systems will exhibit at Embedded World 2019, the iconic event for Europe’s embedded community, hosted in Nuremberg, Germany, from February 26 to 28. The company will focus on secure license management applied to electronic systems, distributed intelligence, the Industrial Internet of Things, e‐mobility, and energy efficiency. Wibu‐Systems’ will exhibit in its main booth (Hall 4/Booth 360) in addition to a presence at the Open Source Automation Development Lab (OSADL), SD Association, Trusted Computing Group, and Wind River exhibits. At Wibu‐Systems’ main stand, company security experts will focus specifically on IP protection as a way to prevent attempts to pirate or reverse engineer crucial code and to ultimately ensure the lasting commercial success for global businesses. They will also share several case studies where IP protection was skillfully integrated into modern business models to multiply revenue streams. At the collective exhibit of OSADL, (Hall 4, booth 168), embedded software developers will lay out the importance of monetizing digital know‐how and raise the quality of their code. Wibu‐Systems, who affiliated with OSADL a couple of years ago, will join forces with them to provide their combined expertise and services to the entire OSADL community. Together with ATP, Delkin, GRL, Hagiwara, JMicron, Micron, Phison, Swissbit, Toshiba, and WD, Wibu‐ Systems will also present some of its many hardware secure elements at the SD Association’s group exhibit (Hall 3A, booth 524). -

4 Cos. Don't Infringe Sandisk Flash Patents: ITC

Portfolio Media, Inc. | 648 Broadway, Suite 200 | New York, NY 10012 | www.law360.com Phone: +1 212 537 6331 | Fax: +1 212 537 6371 | [email protected] 4 Cos. Don't Infringe SanDisk Flash Patents: ITC By Ryan Davis Law360, New York (April 13, 2009) -- An administrative law judge for the U.S. International Trade Commission has ruled that flash memory products made by Silicon Motion Technology Corp., Phison Electronics Corp., Skymedi Corp and Imation Corp. do not infringe two patents held by SanDisk Corp., a setback for SanDisk in a patent case it originally brought against dozens of competitors. In an initial determination issued Friday, Administrative Law Judge Charles E. Bullock ruled that the four companies did not infringe the asserted claims of SanDisk's patents, and that one claim of one of the patents was invalid for obviousness. Both patents involve methods for storing and organizing data in portable flash memory devices. “SanDisk tried to coerce the flash memory industry to pay unwarranted license fees on patents of limited value,” said Mike Bettinger, an attorney for Taiwan-based Silicon Motion. “We said from the beginning that the SanDisk patents don’t cover Silicon Motion products. We are pleased with the fact that Silicon Motion came away with a complete victory.” E. Earle Thompson, SanDisk's vice president and chief intellectual property counsel, said in a statement that the company was disappointed by the ruling. “We will continue to vigorously pursue actions against companies that use SanDisk’s patented technology without a license,” Thompson said. “SanDisk expects that the Initial Determination will not adversely impact existing licensing agreements or the royalties expected from those agreements.” The patents-at-issue in the ruling are U.S. -

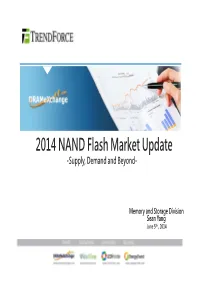

2014 NAND Flash Market Update -Supply, Demand and Beyond

2014 NAND Flash Market Update -Supply, Demand and Beyond- Memory and Storage Division Sean Yang June 5 th , 2014 Supply, Sufficiency and ASP ALL RIGHTS RESERVED. REPRODUCTION PROHIBITED WITHOUT WRITTEN PERMISSION . June, 2014 |Page 2 NAND Market Revenue Trend 2014 NAND market revenue continues to grow with solid demand from diversified applications. 60% 51% 31% 7% 23% 14% 16% 19% -7% 5% USD$bn 30 -18% NAND Revenue Growth.(%) 25 20 15 10 5 - 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014E External Drive/ Consumer Embedded Drive/ ICT Storage Source: DRAMeXchange,June2014 ALL RIGHTS RESERVED. REPRODUCTION PROHIBITED WITHOUT WRITTEN PERMISSION . June, 2014 |Page 3 2014 NAND Market: Balance is the Theme 2014: Supply growth @38% YoY, Demand grwoth@39% YoY. NAND makers are profit-oriented and conservative toward supply strategy. Supply & Demand balance is a new paradigm. 12.3% Unit: 2GB M equiv. 5.8% 6.0% 2.6% 1.9% 30,000 1.3% 1.8% -0.2% 20,000 10,000 - 2007 2008 2009 2010 2011 2012 2013 2014E Bit Supply Shipment Bit Demand Shipment Source: DRAMeXchange,June2014 ALL RIGHTS RESERVED. REPRODUCTION PROHIBITED WITHOUT WRITTEN PERMISSION . June, 2014 |Page 4 CAPEX: Preparation for 3D-NAND Era 2014 CAPEX : US$9.2 Bn with 15%yoy , mostly reserved for 3D-NAND in the future. Memory CAPEX is US$15-16 Bn level, allocation favor on NAND. NAND Flash CAPEX CAPEX: DRAM vs. NAND Unit: US$M Unit: US$M 12,000 25,000 100% 10,000 20,000 DRAM CAPEX NAND Flash CAPEX 8,000 60% 15,000 6,000 20% 10,000 4,000 -20% 5,000 2,000 0 -60% - 2008 2009 2010 2011 2012 2013 2014E 2008 2009 2010 2011 2012 2013 2014E Source: DRAMeXchange,June2014 ALL RIGHTS RESERVED. -

In the United States District Court for the Western District of Wisconsin

IN THE UNITED STATES DISTRICT COURT FOR THE WESTERN DISTRICT OF WISCONSIN - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - SANDISK CORPORATION, OPINION and ORDER Plaintiff, v. 10-cv-243-bbc KINGSTON TECHNOLOGY CO., INC. and KINGSTON TECHNOLOGY CORP., Defendants. - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - This lawsuit is the third such action brought by plaintiff SanDisk Corporation against defendants Kingston Technology Co., Inc. and Kingston Technology Corp. for infringement of plaintiff’s patents related to flash memory technology. In this lawsuit, at issue are six patents belonging to plaintiff: United States Patents Nos. 7,397,713 (‘713 patent); 7,492,660 (‘660 patent); 7,657,702 (‘702 patent); 7,532,511 (‘511 patent); 7,646,666 (‘666 patent); and 7,646,667 (‘667). These patents all share specifications with patents brought in two previous lawsuits, Cases Nos. 07-cv-605-bbc and 07-cv-607-bbc. Now before the court are defendants’ motion for summary judgment of noninfringement, plaintiff’s motion to strike portions of that motion and to strike portions of a rebuttal expert report, motions from both parties for leave to file additional briefing on the motion to strike, and defendants’ motion for leave to file corrected versions of expert reports. I will grant the motions for leave to file additional briefing but deny the motion to strike and grant the 1 motion to file corrected versions of expert reports. I will also grant defendants’ motion for summary judgment of noninfringement in full. As a result, it is not necessary to address the question of damages, and in my discretion I decline to exercise jurisdiction over the remaining invalidity claims and will thus deny the motion for summary judgment of invalidity. -

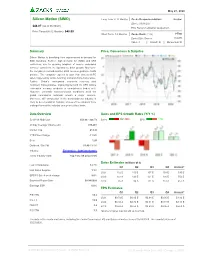

Silicon Motion

May 27, 2020 Silicon Motion (SIMO) Long Term: 6-12 Months Zacks Recommendation: Neutral (Since: 03/11/20) $44.87 (As of 05/26/20) Prior Recommendation: Outperform Price Target (6-12 Months): $48.00 Short Term: 1-3 Months Zacks Rank: (1-5) 2-Buy Zacks Style Scores: VGM:B Value: C Growth: B Momentum: B Summary Price, Consensus & Surprise Silicon Motion is benefiting from improvement in demand for SSD Solutions. Further, high demand for eMMC and UFS controllers, due to growing adoption of mobile embedded memory controllers, is expected to drive growth. Moreover, the company's second-quarter 2020 revenue guidance holds promise. The company expects to gain from increased PC sales triggered by online learning and work-from-home wave. Further, China’s anticipated economic recovery post lockdown holds promise. Improving demand for UFS mobile embedded memory products in smartphones bodes well. However, uncertain macroeconomic conditions amid the global coronavirus outbreak remain a major concern. Moreover, stiff competition in the semiconductor industry is likely to be a headwind. Notably, shares of the company have underperformed the industry on a year-to-date basis. Data Overview Sales and EPS Growth Rates (Y/Y %) 52 Week High-Low $53.04 - $26.72 Sales EPS 20 Day Average Volume (sh) 436,281 Market Cap $1.6 B YTD Price Change -11.5% Beta 1.26 Dividend / Div Yld $1.40 / 3.1% Industry Electronics - Semiconductors Zacks Industry Rank Top 15% (39 out of 253) Sales Estimates (millions of $) Last EPS Surprise 12.7% Q1 Q2 Q3 Q4 Annual* Last Sales Surprise 1.1% 2021 132 E 142 E 157 E 158 E 595 E EPS F1 Est- 4 week change 9.6% 2020 133 A 140 E 141 E 136 E 550 E Expected Report Date 08/04/2020 2019 95 A 99 A 111 A 153 A 457 A Earnings ESP 0.0% EPS Estimates Q1 Q2 Q3 Q4 Annual* P/E TTM 19.2 2021 $0.72 E $0.80 E $0.94 E $0.95 E $3.42 E P/E F1 15.9 2020 $0.80 A $0.76 E $0.81 E $0.78 E $3.18 E PEG F1 3.2 2019 $0.42 A $0.52 A $0.69 A $0.96 A $2.60 A P/S TTM 3.3 *Quarterly figures may not add up to annual. -

2013 Annual Report

SILICON MOTION TECHNOLOGY CORPORATION Annual Report 2013 Financial Highlights Product Mix % of Net Sales (2013) Mobile Storage 82 % Mobile Communications 14 % Others 4 % Net Sales US$ million 2009 89 2010 133 2011 224 2012 281 2013 225 Contents Financial Highlights 01 Letter to Shareholders 02 About Silicon Motion 04 Form 20-F Directors and Executives Gross Margin % of Net Sales 2009 41% 2010 47% 2011 48% 2012 47% 2013 47% Diluted Earnings per ADS US$ 2009 - 2.54 2010 - 0.18 2011 1.28 2012 1.40 2013 0.81 01 Letter to Shareholders Dear Shareholders, 2013 was a transitional year for Silicon Motion as sales of removable storage controllers for mature card and USB flash drive markets declined while sales of SSD plus embedded storage controllers, especially for eMMC growth markets, grew rapidly. 2013 was also a transitional year for our LTE transceiver products as the market quickly moved to the significantly enhanced LTE-Advanced standard. While the negative effects of the transitions were dramatic from the perspective of revenue and profitability, we believe we have built a strong foundation for renewed, long-term growth by focusing on eMMC, SSD, and other embedded storage applications and are confident this will lead to strong growth in upcoming years. In 2013, sales of our SSD plus embedded products grew almost 100% year-over-year to account for almost half of our Mobile Storage sales. Sales of eMMC controllers, our largest SSD plus embedded product, are now already larger than our card and USB flash drive controllers sales, and account for roughly a third of our total revenue. -

Company Vendor ID (Decimal Format) (AVL) Ditest Fahrzeugdiagnose Gmbh 4621 @Pos.Com 3765 0XF8 Limited 10737 1MORE INC

Vendor ID Company (Decimal Format) (AVL) DiTEST Fahrzeugdiagnose GmbH 4621 @pos.com 3765 0XF8 Limited 10737 1MORE INC. 12048 360fly, Inc. 11161 3C TEK CORP. 9397 3D Imaging & Simulations Corp. (3DISC) 11190 3D Systems Corporation 10632 3DRUDDER 11770 3eYamaichi Electronics Co., Ltd. 8709 3M Cogent, Inc. 7717 3M Scott 8463 3T B.V. 11721 4iiii Innovations Inc. 10009 4Links Limited 10728 4MOD Technology 10244 64seconds, Inc. 12215 77 Elektronika Kft. 11175 89 North, Inc. 12070 Shenzhen 8Bitdo Tech Co., Ltd. 11720 90meter Solutions, Inc. 12086 A‐FOUR TECH CO., LTD. 2522 A‐One Co., Ltd. 10116 A‐Tec Subsystem, Inc. 2164 A‐VEKT K.K. 11459 A. Eberle GmbH & Co. KG 6910 a.tron3d GmbH 9965 A&T Corporation 11849 Aaronia AG 12146 abatec group AG 10371 ABB India Limited 11250 ABILITY ENTERPRISE CO., LTD. 5145 Abionic SA 12412 AbleNet Inc. 8262 Ableton AG 10626 ABOV Semiconductor Co., Ltd. 6697 Absolute USA 10972 AcBel Polytech Inc. 12335 Access Network Technology Limited 10568 ACCUCOMM, INC. 10219 Accumetrics Associates, Inc. 10392 Accusys, Inc. 5055 Ace Karaoke Corp. 8799 ACELLA 8758 Acer, Inc. 1282 Aces Electronics Co., Ltd. 7347 Aclima Inc. 10273 ACON, Advanced‐Connectek, Inc. 1314 Acoustic Arc Technology Holding Limited 12353 ACR Braendli & Voegeli AG 11152 Acromag Inc. 9855 Acroname Inc. 9471 Action Industries (M) SDN BHD 11715 Action Star Technology Co., Ltd. 2101 Actions Microelectronics Co., Ltd. 7649 Actions Semiconductor Co., Ltd. 4310 Active Mind Technology 10505 Qorvo, Inc 11744 Activision 5168 Acute Technology Inc. 10876 Adam Tech 5437 Adapt‐IP Company 10990 Adaptertek Technology Co., Ltd. 11329 ADATA Technology Co., Ltd. -

Company Overview Valuation Data Source

Valuation Data Source company overview No. Company No. Company No. Company "Bank "Saint-Petersburg" Public 60 AbClon Inc. 117 Activision Blizzard, Inc. 1 Joint-Stock Company Abdullah Al-Othaim Markets 118 Actron Technology Corporation 61 2 1&1 Drillisch AG Company 119 Actuant Corporation 3 1-800-FLOWERS.COM, Inc. Abdulmohsen Al-Hokair Group for 120 Acuity Brands, Inc. 62 4 11 bit studios S.A. Tourism and Development Company 121 Acushnet Holdings Corp. 5 1st Constitution Bancorp 63 Abengoa, S.A. 122 Ad-Sol Nissin Corporation 6 1st Source Corporation 64 Abeona Therapeutics Inc. 123 Adairs Limited 7 21Vianet Group, Inc. 65 Abercrombie & Fitch Co. 124 ADAMA Ltd. 8 22nd Century Group, Inc. 66 Ability Enterprise Co., Ltd. 125 Adamas Pharmaceuticals, Inc. Ability Opto-Electronics Technology 126 Adamis Pharmaceuticals Corporation 9 2U, Inc. 67 Co.,Ltd. 127 Adani Enterprises Limited 10 3-D Matrix, Ltd. 68 Abiomed, Inc. 128 Adani Gas Limited 11 361 Degrees International Limited 69 ABIST Co.,Ltd. 129 Adani Green Energy Limited 12 3D Systems Corporation 70 ABL Bio Inc. Adani Ports and Special Economic 13 3i Group plc 130 71 Able C&C Co., Ltd. Zone Limited 14 3M Company 131 Adani Power Limited 72 ABM Industries Incorporated 15 3M India Limited 132 Adani Transmissions Limited 73 ABN AMRO Bank N.V. 16 3S KOREA Co., Ltd. 133 Adaptimmune Therapeutics plc 74 Aboitiz Equity Ventures, Inc. 17 3SBio Inc. 134 Adastria Co., Ltd. 75 Aboitiz Power Corporation 18 500.com Limited 135 ADATA Technology Co., Ltd. 76 Abraxas Petroleum Corporation 19 51 Credit Card Inc.