The Role of Fairchild in Silicon Technology in the Early Days of “Silicon Valley”

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Semiconductor Industry Social Media Review

Revealed SOCIAL SUCCESS White Paper Who’s winning the social media battle in the semiconductor industry? Issue 2, September 3, 2014 The contents of this White Paper are protected by copyright and must not be reproduced without permission © 2014 Publitek Ltd. All rights reserved Who’s winning the social media battle in the semiconductor industry? Issue 2 SOCIAL SUCCESS Who’s winning the social media battle in the semiconductor industry? Report title OVERVIEW This time, in the interest of We’ve combined quantitative balance, we have decided to and qualitative measures to This report is an update to our include these companies - Intel, reach a ranking for each original white paper from channel. Cross-channel ranking Samsung, Sony, Toshiba, Nvidia led us to the overall index. September 2013. - as well as others, to again analyse the following channels: As before, we took a company’s Last time, we took the top individual “number semiconductor companies 1. Blogs score” (quantitative measure) (according to gross turnover - 2. Facebook for a channel, and multiplied main source: Wikipedia), of this by its “good practice score” 3. Google+ which five were ruled out due (qualitative measure). 4. LinkedIn to the diversity of their offering 5. Twitter The companies were ranked by and the difficulty of segmenting performance in each channel. 6. YouTube activity relating to An average was then taken of semiconductors. ! their positions in each to create the final table. !2 Who’s winning the social media battle in the semiconductor industry? Issue 2 Due to the instantaneous nature of social media, this time we decided to analyse a narrower time frame, and picked a single month - August 2014. -

High Performance Power Distribution Networks with On-Chip Decoupling Capacitors for Nanoscale Integrated Circuits

High Performance Power Distribution Networks with On-Chip Decoupling Capacitors for Nanoscale Integrated Circuits by Mikhail Popovich Submitted in Partial Ful¯llment of the Requirements for the Degree Doctor of Philosophy Supervised by Professor Eby G. Friedman Department of Electrical and Computer Engineering The College School of Engineering and Applied Sciences University of Rochester Rochester, New York 2007 ii It has become appallingly obvious that our technology has exceeded our humanity. | Albert Einstein iii Dedication This work is dedicated to my parents, Mr. Evgeniy Antonovich and Mrs. Lyud- mila Mikhailovna, my wife Oksana, and my daughter Elizabeth Michelle. iv Curriculum Vitae Mikhail Popovich was born in Izhevsk, Russia in 1975. He received the B.S. degree in electrical engineering from Izhevsk State Technical University, Izhevsk, Russia in 1998, and the M.S. degree in electrical and computer engineering from the University of Rochester, Rochester, NY in 2002, where he is completing the Ph.D. degree in electrical engineering. He was an intern at Freescale Semiconductor Corporation, Tempe, AZ, in the summer 2005, where he worked on signal integrity in RF and mixed-signal ICs and developed design techniques and methodologies for placing distributed on-chip de- coupling capacitors. His professional experience also includes characterization of sub- strate and interconnect crosstalk noise in CMOS imaging circuits for the Eastman Kodak Company, Rochester, NY. He has authored a book and several conference and journal papers in the areas of power distribution networks in CMOS VLSI circuits, placement of on-chip decoupling capacitors, and the inductive properties of on-chip v interconnect. His research interests are in the areas of on-chip noise, signal integrity, and interconnect design including on-chip inductive e®ects, optimization of power distribution networks, and the design of on-chip decoupling capacitors. -

Introduction to the Course. in This Lecture I Would Try to Set the Course in Perspective

Introduction to the course. In this lecture I would try to set the course in perspective. Before we embark on learning something, it is good to ponder why it would be interesting, besides the fact that it can fetch useful course credits. What do you understand by VLSI? In retrospect, integrated circuits having 10s of devices were called small scale integrated circuits (SSI), a few hundreds were called medium scale few thousands large scale. The game stopped with VLSI as people lost the count (not really). What does the word VLSI bring to your mind? Discussion to follow. What do you understand by technology? Discussion to follow. Technology is the application of scientific knowledge for practical purposes. For example, why you may not call VLSI circuit design as VLSI technology? This is by convention in the semiconductor business research and business community. The convention is to treat fabrication technology as the “technology”. In this course we would discuss and try to learn how Silicon Integrated Circuits are fabricated. Integrated circuits are fabricated by a sequence of fabrication steps called unit processes. A unit process would add to or subtract from a substrate. Examples of unit processes can be cleaning of a wafer, deposition of a thin film of a material and so on. The unit processes are not uniquely applied to VLSI fabrication only. I can combine several of these unit processes to make solar cells. I can do same for making MEMS devices. So the unit processes can be thought of as pieces in a jigsaw puzzles. The outcome would depend on how you sequence the unit processes. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

Timeline of the Semiconductor Industry in South Portland

Timeline of the Semiconductor Industry in South Portland Note: Thank you to Kathy DiPhilippo, Executive Director/Curator of the South Portland Historical Society and Judith Borelli, Governmental Relations of Texas Inc. for providing some of the information for this timeline below. Fairchild Semiconductor 1962 Fairchild Semiconductor (a subsidiary of Fairchild Camera and Instrument Corp.) opened in the former Boland's auto building (present day Back in Motion) at 185 Ocean Street in June of 1962. They were there only temporarily, as the Western Avenue building was still being constructed. 1963 Fairchild Semiconductor moves to Western Avenue in February 1963. 1979 Fairchild Camera and Instrument Corp. is acquired/merged with Schlumberger, Ltd. (New York) for $363 million. 1987 Schlumberger, Ltd. sells its Fairchild Semiconductor Corp. subsidiary to National Semiconductor Corp. for $122 million. 1997 National Semiconductor sells the majority ownership interest in Fairchild Semiconductor to an investment group (made up of Fairchild managers, including Kirk Pond, and Citcorp Venture Capital Ltd.) for $550 million. Added Corporate Campus on Running Hill Road. 1999 In an initial public offering in August 1999, Fairchild Semiconductor International, Inc. becomes a publicly traded corporation on the New York Stock Exchange. 2016 Fairchild Semiconductor International, Inc. is acquired by ON Semiconductor for $2.4 billion. National Semiconductor 1987 National Semiconductor acquires Fairchild Semiconductor Corp. from Schlumberger, Ltd. for $122 million. 1995 National Semiconductor breaks ground on new 200mm factory in December 1995. 1996 National Semiconductor announces plans for a $600 million expansion of its facilities in South Portland; construction of a new wafer fabrication plant begins. 1997 Plant construction for 200mm factory completed and production starts. -

Transistors to Integrated Circuits

resistanc collectod ean r capacit foune yar o t d commercial silicon controlled rectifier, today's necessarye b relative .Th e advantage lineaf so r thyristor. This later wor alss kowa r baseou n do and circular structures are considered both for 1956 research [19]. base resistanc r collectofo d an er capacity. Parameters, which are expected to affect the In the process of diffusing the p-type substrate frequency behavior considerede ar , , including wafer into an n-p-n configuration for the first emitter depletion layer capacity, collector stage of p-n-p-n construction, particularly in the depletion layer capacit diffusiod yan n transit redistribution "drive-in" e donophasth f ro e time. Finall parametere yth s which mighe b t diffusion at higher temperature in a dry gas obtainabl comparee ear d with those needer dfo ambient (typically > 1100°C in H2), Frosch a few typical switching applications." would seriously damag r waferseou wafee Th . r surface woul e erodedb pittedd an d r eveo , n The Planar Process totally destroyed. Every time this happenee dth s e apparenlosexpressiowa th s y b tn o n The development of oxide masking by Frosch Frosch' smentiono t face t no , ourn o , s (N.H.). and Derick [9,10] on silicon deserves special We would make some adjustments, get more attention inasmuch as they anticipated planar, oxide- silicon wafers ready, and try again. protected device processing. Silicon is the key ingredien oxids MOSFEr it fo d ey an tpave wa Te dth In the early Spring of 1955, Frosch commented integrated electronics [22]. -

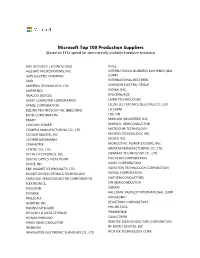

Microsoft Top 100 Production Suppliers (Based on FY14 Spend for Commercially Available Hardware Products)

Microsoft Top 100 Production Suppliers (Based on FY14 spend for commercially available hardware products) AAC ACOUSTIC TECHNOLOGIES INTEL ALLEGRO MICROSYSTEMS, INC. INTERNATIONAL BUSINESS MACHINES (IBM ALPS ELECTRIC COMPANY CORP.) AMD INTERNATIONAL RECTIFIER AMPEREX TECHNOLOGY, LTD. JOHNSON ELECTRIC GROUP AMPHENOL KIONIX, INC. ANALOG DEVICES KYOCERA/AVX ASKEY COMPUTER CORPORATION LAIRD TECHNOLOGIES ATMEL CORPORATION LELON ELECTRONICS (SUZHOU) CO., LTD BIZLINK TECHNOLOGY INC (BIZCONN) LG CHEM BOYD CORPORATION LITE-ON BRADY MARLOW INDUSTRIES, INC. CHICONY POWER MARVELL SEMICONDUCTOR COMPEQ MANUFACTURING CO., LTD. MICROCHIP TECHNOLOGY COOLER MASTER, INC. MICRON TECHNOLOGY, INC. COOPER BUSSMANN MOLEX, INC. CYMMETRIK MONOLITHIC POWER SYSTEMS, INC. CYNTEC CO., LTD. MURATA MANUFACTURING CO., LTD. DELTA ELECTRONICS, INC. NEWMAX TECHNOLOGY CO., LTD. DIGITAL OPTICS VISTA POINT NICHICON CORPORATION DIODE, INC. NIDEC CORPORATION E&E MAGNETICS PRODUCTS, LTD. NUVOTON TECHNOLOGY CORPORATION ELLINGTON ELECTRONICS TECHNOLOGY NVIDIA CORPORATION FAIRCHILD SEMICONDUCTOR CORPORATION NXP SEMICONDUCTORS FLEXTRONICS ON SEMICONDUCTOR FOXCONN OSRAM FOXLINK PALCONN, PALPILOT INTERNATIONAL CORP. FREESCALE PANASONIC GOERTEK, INC. PEGATRON CORPORATION HANNSTAR BOARD PHILIPS PLDS HITACHI-LG DATA STORAGE PRIMESENSE HONDA PRINTING QUALCOMM HYNIX SEMICONDUCTOR REALTEK SEMICONDUCTOR CORPORATION INFINEON RF MICRO DEVICES, INC. INNOVATOR ELECTRONIC SHENZHEN CO., LTD RICHTEK TECHNOLOGY CORP. ROHM CORPORATION SAMSUNG DISPLAY SAMSUNG ELECTRONICS SAMSUNG SDI SAMSUNG SEMICONDUCTOR SEAGATE SHEN ZHEN JIA AI MOTOR CO., LTD. SHENZHEN HORN AUDIO CO., LTD. SHINKO ELECTRIC INDUSTRIES CO., LTD. STARLITE PRINTER, LTD. STMICROELECTRONICS SUNG WEI SUNUNION ENVIRONMENTAL PACKAGING CO., LTD TDK TE CONNECTIVITY TEXAS INSTRUMENTS TOSHIBA TPK TOUCH SOLUTIONS, INC. UNIMICRON TECHNOLOGY CORP. UNIPLAS (SHANGHAI) CO., LTD. UNISTEEL UNIVERSAL ELECTRONICS INCORPORATED VOLEX WACOM CO., LTD. WELL SHIN TECHNOLOGY WINBOND WOLFSON MICROELECTRONICS, LTD. X-CON ELECTRONICS, LTD. YUE WAH CIRCUITS CO., LTD. -

Planar Process with Noyce’S Interconnection Via a Diffused Layer of Metal Conductors

Future Horizons Ltd Blakes Green Cottage TN15 0LQ, UK Tel: +44 1732 740440 Fax: +44 1732 608045 [email protected] www.futurehorizons.com Research Brief: 2019/01 – The Planar IC Process The Planar IC Process On 1 December 1957, Jean Hoerni, a Swiss physicist and Fairchild Semiconductor co-founder, recorded in his patent notebook an entry called "A method of protecting exposed p-n junctions at the surface of silicon transistors by oxide masking techniques." This was the first formal documentation of the planar semiconductor process, a radically new transistor design in which the oxide layer was left in place on the silicon wafer to protect the sensitive p-n junctions underneath. Focused on getting its first semiconductor devices into production, Fairchild did not pursue Hoerni’s planar approach at that time and it was not until 14 January 1959 that Hoerni finally wrote up his disclosure for what would become U.S. Patent 3025589. One week later, on 23 January 1959, Robert (Bob) Noyce, a fellow Fairchild co-founder, wrote up a disclosure for the planar IC. Fairchild’s first working planar IC was built some 16 months later in May 1960. Sixty years on, this technology remains the basis for virtually all semiconductor manufacturing today. The Early Days By the late 1950s, even though barely a decade old, transistors had already gone through several stages of development, including the material transition from germanium to silicon and the move from piece by piece to batch manufacturing through a simple photolithographic and Page 1 of 8 © Future Horizons 1989-2019, Reproduction Prohibited - All Rights Reserved The Planar IC Process The Global Semiconductor Industry Analysts Research Brief: 2019/01 etching technique known as the Mesa process. -

Discrete Semiconductor Products Fairchild@50

Fairchild Oral History Panel: Discrete Semiconductor Products Fairchild@50 (Panel Session # 3) Participants: Jim Diller Bill Elder Uli Hegel Bill Kirkham Moderated by: George Wells Recorded: October 5, 2007 Mountain View, California CHM Reference number: X4208.2008 © 2007 Computer History Museum Fairchild Semiconductor: Discrete Products George Wells: My name's George Wells. I came to Fairchild in 1969, right in the midst of the Hogan's Heroes, shall we say, subculture, at the time. It was difficult to be in that environment as a bystander, as someone watching a play unfold. It was a difficult time, but we got through that. I came to San Rafael, Wilf asked me to get my ass up to San Rafael and turn it around or shut it down. So I was up in San Rafael for a while, and then I made my way through various different divisions, collecting about 15 of them by the time I was finished. I ended up as executive vice president, working for Wilf, and left the company about a year and a half after the Schlumberger debacle. That's it in a nutshell. Let me just turn over now to Uli Hegel, who was with Fairchild for 38 years, one of the longest serving members, I believe, in the room. Maybe the longest serving member. Uli, why don't you tell us what you did when you came, when you came and what jobs you had when you were there. Uli Hegel: I came to Fairchild in 1959, September 9, and hired into R&D as a forerunner to the preproduction days. -

Fairchild Singapore Story

The Fairchild Singapore Story 1968 - 1987 “Fairchild Singapore Pte Ltd started in 1968. In 1987, it was acquired by National Semiconductor and ceased to exist. The National Semiconductor site at Lower Delta was shutdown and operations were moved to the former Fairchild site at Lorong 3, Toa Payoh. This book is an attempt to weave the hundreds of individual stories from former Fairchild employees into a coherent whole.” 1 IMPORTANT NOTE This is a draft. The final may look significantly different. Your views are welcome on how we can do better. 2 CONTENTS WHAT THIS BOOK IS ABOUT FOREWORD ?? ACKNOWLEDGEMENTS INTRODUCTION How Fairchild Singapore Came About CHAPTER 1 The Managing Directors CHAPTER 2 Official Opening 1969 CHAPTER 3 1975: Official Opening of Factory Two CHAPTER 4 1977 - 79: Bruce’s Leadership CHAPTER 5 1979: A Schlumberger Company 3 CHAPTER 6 1986: Sold to Fujitsu CHAPTER 7 1987: Sold to National Semiconductor CHAPTER 8 Birth of the Semiconductor Industry in Singapore CHAPTER 9 Aerospace & Defence Division CHAPTER 10 Memory & High Speed Logic Division CHAPTER 11 Digital Integrated Circuit Division CHAPTER 12 Design Centre CHAPTER 13 The Ceramic Division CHAPTER 14 The Quality & Reliability Division CHAPTER 15 The Mil-Aero Division CHAPTER 16 The Standard Ceramic Division CHAPTER 17 The Plastic Leaded Chip Carrier Division 4 CHAPTER 18 Retrenchments CHAPTER 19 The Expats CHAPTER 20 Personnel Department CHAPTER 21 IT Group CHAPTER 22 Life After Fairchild APPENDICES _______________________ ?? INDEX 5 What this Book is About “Fairchild Singapore plant together with other multinational corporations in Singapore have allowed the country to move from Third World to First within one generation” ingapore’s first generation of leaders did what was good for the country. -

Fairchild Symbol Computer

Anecdotes Fairchild Symbol Computer Stanley Mazor IEEE, Sr. Member Editor: Anne Fitzpatrick In 1965, Gordon Moore of Fairchild Semiconductor As it happened, Gordon Moore’s R&D computer published what is known as Moore’s law: his observation development group wanted a practicing programmer to and prediction about the growing density of IC chips, and join their staff, so I transferred to R&D in 1966.13 Our the precursor to large-scale integration.1 Moore’s predic- project team developed a new language, Symbol, and the tions about LSI chips raised questions about how complex hardware for directly executing it. The Symbol computer chips would be designed and used.2–6 As the Fairchild overcame the data handling problems that I’d encoun- R&D director, he initiated several research projects tered with the sales order entry software. At the expense addressing the following LSI design and use issues: of extra hardware, the Symbol computer removed ‘‘artifacts’’—introduced to improve execution speed— N computer-aided design tools (CAD) for LSI chips of conventional computing languages. Undesirable N cellular logic chips using standard cells programming artifacts, for example, included static data N gate array logic chips types and type declaration. N packaging for LSI chips N semiconductor memory chips Computer design project N computer design with LSI chips One of Moore’s R&D groups, Digital Systems Research (see Figure 1) under the direction of Rex Rice, focused on As testimony to Moore’s vision, most of these Fairchild chip and system packaging. This group had developed projects subsequently spawned new industries and the original Dual In-line Package (DIP). -

FAN6100Q Secondary-Side Constant Voltage and Constant Current Controller Compatible with Qualcomm® Quick Charge 2.0

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body.