Semiconductor Memories: Rams and Roms

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 Semiconductor Memories

Chapter 3 Semiconductor Memories Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline Introduction Random Access Memories Content Addressable Memories Read Only Memories Flash Memories Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Overview of Memory Types Semiconductor Memories Read/Write Memory or Random Access Memory (RAM) Read Only Memory (ROM) Random Access Non-Random Access Memory (RAM) Memory (RAM) •Mask (Fuse) ROM •Programmable ROM (PROM) •Erasable PROM (EPROM) •Static RAM (SRAM) •FIFO/LIFO •Electrically EPROM (EEPROM) •Dynamic RAM (DRAM) •Shift Register •Flash Memory •Register File •Content Addressable •Ferroelectric RAM (FRAM) Memory (CAM) •Magnetic RAM (MRAM) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Memory Elements – Memory Architecture Memory elements may be divided into the following categories Random access memory Serial access memory Content addressable memory Memory architecture 2m+k bits row decoder row decoder 2n-k words row decoder row decoder column decoder k column mux, n-bit address sense amp, 2m-bit data I/Os write buffers Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 1-D Memory Architecture S0 S0 Word0 Word0 S1 S1 Word1 Word1 S2 S2 Word2 Word2 A0 S3 S3 A1 Decoder Ak-1 Sn-2 Storage Sn-2 Wordn-2 element Wordn-2 Sn-1 Sn-1 Wordn-1 Wordn-1 m-bit m-bit Input/Output Input/Output n select signals are reduced n select signals: S0-Sn-1 to k address signals: A0-Ak-1 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Memory Architecture S0 Word0 Wordi-1 S1 A0 A1 Ak-1 Row Decoder Sn-1 Wordni-1 A 0 Column Decoder Aj-1 Sense Amplifier Read/Write Circuit m-bit Input/Output Advanced Reliable Systems (ARES) Lab. -

File Systems and Disk Layout I/O: the Big Picture

File Systems and Disk Layout I/O: The Big Picture Processor interrupts Cache Memory Bus I/O Bridge Main I/O Bus Memory Disk Graphics Network Controller Controller Interface Disk Disk Graphics Network 1 Rotational Media Track Sector Arm Cylinder Platter Head Access time = seek time + rotational delay + transfer time seek time = 5-15 milliseconds to move the disk arm and settle on a cylinder rotational delay = 8 milliseconds for full rotation at 7200 RPM: average delay = 4 ms transfer time = 1 millisecond for an 8KB block at 8 MB/s Bandwidth utilization is less than 50% for any noncontiguous access at a block grain. Disks and Drivers Disk hardware and driver software provide basic facilities for nonvolatile secondary storage (block devices). 1. OS views the block devices as a collection of volumes. A logical volume may be a partition ofasinglediskora concatenation of multiple physical disks (e.g., RAID). 2. OS accesses each volume as an array of fixed-size sectors. Identify sector (or block) by unique (volumeID, sector ID). Read/write operations DMA data to/from physical memory. 3. Device interrupts OS on I/O completion. ISR wakes up process, updates internal records, etc. 2 Using Disk Storage Typical operating systems use disks in three different ways: 1. System calls allow user programs to access a “raw” disk. Unix: special device file identifies volume directly. Any process that can open thedevicefilecanreadorwriteany specific sector in the disk volume. 2. OS uses disk as backing storage for virtual memory. OS manages volume transparently as an “overflow area” for VM contents that do not “fit” in physical memory. -

Error Detection and Correction Methods for Memories Used in System-On-Chip Designs

International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-8, Issue-2S2, January 2019 Error Detection and Correction Methods for Memories used in System-on-Chip Designs Gunduru Swathi Lakshmi, Neelima K, C. Subhas ABSTRACT— Memory is the basic necessity in any SoC Static Random Access Memory (SRAM): It design. Memories are classified into single port memory and consists of a latch or flipflop to store each bit of multiport memory. Multiport memory has ability to source more memory and it does not required any refresh efficient execution of operation and high speed performance operation. SRAM is mostly used in cache memory when compared to single port. Testing of semiconductor memories is increasing because of high density of current in the and in hand-held devices. It has advantages like chips. Due to increase in embedded on chip memory and memory high speed and low power consumption. It has density, the number of faults grow exponentially. Error detection drawback like complex structure and expensive. works on concept of redundancy where extra bits are added for So, it is not used for high capacity applications. original data to detect the error bits. Error correction is done in Read Only Memory (ROM): It is a non-volatile memory. two forms: one is receiver itself corrects the data and other is It can only access data but cannot modify data. It is of low receiver sends the error bits to sender through feedback. Error detection and correction can be done in two ways. One is Single cost. Some applications of ROM are scanners, ID cards, Fax bit and other is multiple bit. -

Low Voltage, One-Time Programmable, Read-Only Memory

Features • Fast read access time – 90ns • Dual voltage range operation – Low voltage power supply range, 3.0V to 3.6V, or – Standard power supply range, 5V 10% • Compatible with JEDEC standard Atmel® AT27C512R • Low-power CMOS operation – 20µA max standby (less than 1µA, typical) for VCC = 3.6V – 29mW max active at 5MHz for VCC = 3.6V 512K (64K x 8) • JEDEC standard package – 32-lead PLCC Low Voltage, • High-reliability CMOS technology One-time – 2,000V ESD protection Programmable, – 200mA latchup immunity • Rapid programming algorithm – 100µs/byte (typical) Read-only Memory • CMOS- and TTL-compatible inputs and outputs – JEDEC standard for LVTTL • Integrated product identification code Atmel AT27LV512A • Industrial temperature range • Green (Pb/halide-free) packaging option 1. Description The Atmel AT27LV512A is a high-performance, low-power, low-voltage, 524,288-bit, one- time programmable, read-only memory (OTP EPROM) organized as 64K by 8 bits. It requires only one supply in the range of 3.0 to 3.6V in normal read mode operation, making it ideal for fast, portable systems using battery power. The Atmel innovative design techniques provide fast speeds that rival 5V parts, while keep- ing the low power consumption of a 3.3V supply. At VCC = 3.0V, any byte can be accessed in less than 90ns. With a typical power dissipation of only 18mW at 5MHz and VCC = 3.3V, the AT27LV512A consumes less than one-fifth the power of a standard, 5V EPROM. Standby mode supply current is typically less than 1µA at 3.3V. The AT27LV512A is available in industry-standard, JEDEC-approved, one-time programmable (OTP) PLCC package. -

Semiconductor Memories

Semiconductor Memories Prof. MacDonald Types of Memories! l" Volatile Memories –" require power supply to retain information –" dynamic memories l" use charge to store information and require refreshing –" static memories l" use feedback (latch) to store information – no refresh required l" Non-Volatile Memories –" ROM (Mask) –" EEPROM –" FLASH – NAND or NOR –" MRAM Memory Hierarchy! 100pS RF 100’s of bytes L1 1nS SRAM 10’s of Kbytes 10nS L2 100’s of Kbytes SRAM L3 100’s of 100nS DRAM Mbytes 1us Disks / Flash Gbytes Memory Hierarchy! l" Large memories are slow l" Fast memories are small l" Memory hierarchy gives us illusion of large memory space with speed of small memory. –" temporal locality –" spatial locality Register Files ! l" Fastest and most robust memory array l" Largest bit cell size l" Basically an array of large latches l" No sense amps – bits provide full rail data out l" Often multi-ported (i.e. 8 read ports, 2 write ports) l" Often used with ALUs in the CPU as source/destination l" Typically less than 10,000 bits –" 32 32-bit fixed point registers –" 32 60-bit floating point registers SRAM! l" Same process as logic so often combined on one die l" Smaller bit cell than register file – more dense but slower l" Uses sense amp to detect small bit cell output l" Fastest for reads and writes after register file l" Large per bit area costs –" six transistors (single port), eight transistors (dual port) l" L1 and L2 Cache on CPU is always SRAM l" On-chip Buffers – (Ethernet buffer, LCD buffer) l" Typical sizes 16k by 32 Static Memory -

Via-Programmable Read-Only Memory Design for Full Code Coverage Using a Dynamic Bit-Line Shielding Technique

Via-Programmable Read-Only Memory Design for Full Code Coverage Using A Dynamic Bit-Line Shielding Technique Meng-Fan Chang1, 2, Ding-Ming Kwai2, and Kuei-Ann Wen1 1 Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 2 Intellectual Property Library Company, Hsinchu, Taiwan [email protected] Abstract 0-cell 1-cell 0-cell Crosstalk between bit lines leads to read-1 failure Metal-3 (BL) in a high-speed via-programmable read only memory (ROM) and limits the coverage of applicable code Via-2 (Code) patterns. Due to the fluctuations in bit-line intrinsic Metal-2 and coupling capacitances, the amount of noise coupled to a selected bit line may vary, resulting in the Via-1 reduction of sensing margin. In this paper, we propose a dynamic bit-line shielding (DBS) technique, suitable Metal-1 to be implemented in compliable ROM, to eliminate the Contact crosstalk-induced read failure and to achieve full code coverage. Experiments of the 256Kb instances with Diffusion Diffusion Diffusion and without the DBS circuit were undertaken using STI STI STI STI 0.25µm and 0.18µm standard CMOS processes. The test results demonstrate the read-1 failures and Fig. 1. Cross-sectional view of ROM array with via-2 confirm that the DBS technique can remove them codes and metal-3 bit lines. successfully, allowing the ROM to operate under a wide range of supply voltage. sectional view of the memory array with via-2 codes 1. Introduction and metal-3 bit lines. This leads to more severe bit-line crosstalk, since the contact and via at the lower levels Mask-programmable read-only memory (ROM) must be stacked and the metal islands for them to land macros are commonly embedded into system-on-chip upon contribute considerable side-wall capacitances to (SoC) designs today. -

Refresh Operation and Semi-Conductor Rom Memories

REFRESH OPERATION AND SEMI-CONDUCTOR ROM MEMORIES The Refresh control block periodically generates Refresh, requests, causing the access control block to start a memory cycle in the normal way. This block allows the refresh operation by activating the Refresh Grant line. The access control block arbitrates between Memory Access requests and Refresh requests, with priority to Refresh requests in the case of a tie to ensure the integrity of the stored data. As soon as the Refresh control block receives the Refresh Grant signal, it activates the Refresh line. This causes the address multiplexer to select the Refresh counter as the source and its contents are thus loaded into the row address latches of all memory chips when the RAS signal is activated. During this time the R/ W line may be low, causing an inadvertent write operation. One way to prevent this is to use the Refresh line to control the decoder block to deactivate all the chip select lines. The rest of the refresh cycle is the same as in a normal cycle. At the end, the Refresh control block increments the refresh counter in preparation for the next Refresh cycle. Even though the row address has 8 bits, the Refresh counter need only be 7 bits wide because of the cell organization inside the memory chips. In a 64k x 1 memory chip, the 256x256 cell array actually consists of two 128x256 arrays. The low order 7 bits of the row address select a row from both arrays and thus the row from both arrays is refreshed! Ideally, the refresh operation should be transparent to the CPU. -

EEPROM Emulation

...the world's most energy friendly microcontrollers EEPROM Emulation AN0019 - Application Note Introduction This application note demonstrates a way to use the flash memory of the EFM32 to emulate single variable rewritable EEPROM memory through software. The example API provided enables reading and writing of single variables to non-volatile flash memory. The erase-rewrite algorithm distributes page erases and thereby doing wear leveling. This application note includes: • This PDF document • Source files (zip) • Example C-code • Multiple IDE projects 2013-09-16 - an0019_Rev1.09 1 www.silabs.com ...the world's most energy friendly microcontrollers 1 General Theory 1.1 EEPROM and Flash Based Memory EEPROM stands for Electrically Erasable Programmable Read-Only Memory and is a type of non- volatile memory that is byte erasable and therefore often used to store small amounts of data that must be saved when power is removed. The EFM32 microcontrollers do not include an embedded EEPROM module for byte erasable non-volatile storage, but all EFM32s do provide flash memory for non-volatile data storage. The main difference between flash memory and EEPROM is the erasable unit size. Flash memory is block-erasable which means that bytes cannot be erased individually, instead a block consisting of several bytes need to be erased at the same time. Through software however, it is possible to emulate individually erasable rewritable byte memory using block-erasable flash memory. To provide EEPROM functionality for the EFM32s in an application, there are at least two options available. The first one is to include an external EEPROM module when designing the hardware layout of the application. -

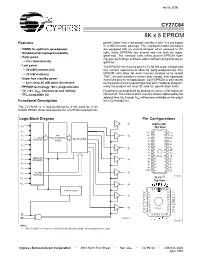

8K X 8 EPROM Features Powers Down Into a Low-Power Standby Mode

1CY 27C6 4 fax id: 3006 CY27C64 8K x 8 EPROM Features powers down into a low-power standby mode. It is packaged in a 600-mil-wide package. The reprogrammable packages • CMOS for optimum speed/power are equipped with an erasure window; when exposed to UV • Windowed for reprogrammability light, these EPROMs are erased and can then be repro- • High speed grammed. The memory cells utilize proven EPROM float- ing-gate technology and byte-wide intelligent programming al- — 0 ns (commercial) gorithms. • Low power The EPROM cell requires only 12.5V for the super voltage and — 40 mW (commercial) low–current requirements allow for gang programming. The — 30 mW (military) EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly • Super low standby power exercised prior to encapsulation. Each EPROM is also tested — Less than 85 mW when deselected for AC performance to guarantee that after customer program- • EPROM technology 100% programmable ming, the product will meet DC and AC specification limits. ± • 5V 10% VCC, commercial and military Reading is accomplished by placing an active LOW signal on • TTL-compatible I/O OE and CE. The contents of the memory location addressed by the address lines (A0 through A12) will become available on the output Functional Description lines (O0 through O7). The CY27C64 is a high-performance 8192 word by 8 bit CMOS PROM. When deselected, the CY27C64 automatically Logic Block Diagram Pin Configurations O7 DIP/CerDIP A0 Top View A1 VCC 1 28 VCC 2 27 A2 64K O6 A12 VCC ROW PROGRAMMABLE A7 3 26 NC A ADDRESS MULTIPLEXER 3 ARRAY A 4 6 25 A8 A5 5 24 A9 A4 A 6 4 23 A11 O5 A5 A3 7 22 OE A2 8 21 A10 A6 A1 9 27C64 20 CE ADDRESS A A7 O 0 10 19 O7 DECODER 4 O0 11 18 O6 A8 O1 12 17 O5 O 13 16 O A9 2 4 GND 14 15 O3 O A10 COLUMN 3 ADDRESS [1] 27C64-2 A11 PLCC Top View A 12 O2 4 POWER DOWN 32132 31 30 A A 6 5 29 8 A 5 6 28 A9 O1 A 4 7 27 A11 A 3 8 26 NC A 2 9 25 OE A A 1 10 24 10 A0 23 CE O0 11 27C64 NC 12 22 O7 O0 13 21 O6 14 15 16 17 18 19 20 CE OE 27C64-1 27C64-3 Notes: 1. -

A Hybrid Swapping Scheme Based on Per-Process Reclaim for Performance Improvement of Android Smartphones (August 2018)

Received August 19, 2018, accepted September 14, 2018, date of publication October 1, 2018, date of current version October 25, 2018. Digital Object Identifier 10.1109/ACCESS.2018.2872794 A Hybrid Swapping Scheme Based On Per-Process Reclaim for Performance Improvement of Android Smartphones (August 2018) JUNYEONG HAN 1, SUNGEUN KIM1, SUNGYOUNG LEE1, JAEHWAN LEE2, AND SUNG JO KIM2 1LG Electronics, Seoul 07336, South Korea 2School of Software, Chung-Ang University, Seoul 06974, South Korea Corresponding author: Sung Jo Kim ([email protected]) This work was supported in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education under Grant 2016R1D1A1B03931004 and in part by the Chung-Ang University Research Scholarship Grants in 2015. ABSTRACT As a way to increase the actual main memory capacity of Android smartphones, most of them make use of zRAM swapping, but it has limitation in increasing its capacity since it utilizes main memory. Unfortunately, they cannot use secondary storage as a swap space due to the long response time and wear-out problem. In this paper, we propose a hybrid swapping scheme based on per-process reclaim that supports both secondary-storage swapping and zRAM swapping. It attempts to swap out all the pages in the working set of a process to a zRAM swap space rather than killing the process selected by a low-memory killer, and to swap out the least recently used pages into a secondary storage swap space. The main reason being is that frequently swap- in/out pages use the zRAM swap space while less frequently swap-in/out pages use the secondary storage swap space, in order to reduce the page operation cost. -

AN-1471 Application Note

AN-1471 APPLICATION NOTE One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com ADuCM4050 Flash EEPROM Emulation by Pranit Jadhav and Rafael Lajara INTRODUCTION provides assurance that the flash initialization function works as Nonvolatile data storage is a necessity in many embedded expected. An ECC check is enabled for the entire user space in systems. Data, such as boot up configuration, calibration constants, the flash memory of the ADuCM4050. If ECC errors are reported and network related information, is normally stored on an during any read operation, the ECC engine automatically corrects electronically erasable programmable read only memory 1-bit errors and only reports on detection of 2-bit errors. When a (EEPROM) device. The advantage of using the EEPROM to store read occurs on the flash, appropriate flags are set in the status this data is that a single byte on an EEPROM device can be register of the ADuCM4050. If interrupts are generated, the source rewritten or updated without affecting the contents in the other address of the ECC error causing an interrupt is available in the locations. FLCC0_ECC_ADDR register for the interrupt service routine (ISR) to read. The ADuCM4050 is an ultra low power microcontroller unit (MCU) with integrated flash memory. The ADuCM4050 includes Emulation of the EEPROM on the integrated flash memory 512 kB of embedded flash memory with a 72-bit wide data bus reduces the bill of material (BOM) cost by omitting the EEPROM that provides two 32-bits words of data and one corresponding in the design. -

File System Layout

File Systems Main Points • File layout • Directory layout • Reliability/durability Named Data in a File System index !le name directory !le number structure storage o"set o"set block Last Time: File System Design Constraints • For small files: – Small blocks for storage efficiency – Files used together should be stored together • For large files: – ConCguous allocaon for sequenCal access – Efficient lookup for random access • May not know at file creaon – Whether file will become small or large File System Design Opons FAT FFS NTFS Index Linked list Tree Tree structure (fixed, asym) (dynamic) granularity block block extent free space FAT array Bitmap Bitmap allocaon (fixed (file) locaon) Locality defragmentaon Block groups Extents + reserve Best fit space defrag MicrosoS File Allocaon Table (FAT) • Linked list index structure – Simple, easy to implement – SCll widely used (e.g., thumb drives) • File table: – Linear map of all blocks on disk – Each file a linked list of blocks FAT MFT Data Blocks 0 1 2 3 !le 9 block 3 4 5 6 7 8 9 !le 9 block 0 10 !le 9 block 1 11 !le 9 block 2 12 !le 12 block 0 13 14 15 16 !le 12 block 1 17 18 !le 9 block 4 19 20 FAT • Pros: – Easy to find free block – Easy to append to a file – Easy to delete a file • Cons: – Small file access is slow – Random access is very slow – Fragmentaon • File blocks for a given file may be scaered • Files in the same directory may be scaered • Problem becomes worse as disk fills Berkeley UNIX FFS (Fast File System) • inode table – Analogous to FAT table • inode – Metadata • File owner, access permissions,