Crack-Junctions Doctoral Thesis Valentin Dubois 2018

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nanoparticle Arrays on Surfaces for Electronic, Optical, and Sensor Applications** Andrew N

18 WILEY-VCH-Verlag GmbH, D-69451 Weinheim, 2000 1439-4235/00/01/01 $ 17.50+.50/0 CHEMPHYSCHEM 2000,1,18±52 Nanoparticle Arrays on Surfaces for Electronic, Optical, and Sensor Applications** Andrew N. Shipway,[a] Eugenii Katz,[a] and Itamar Willner*[a] Particles in the nanometer size range are attracting increasing their organization on surfaces for the construction of functional attention with the growth of interest in nanotechnological interfaces. In this review, we address the research that has led to disciplines. Nanoparticles display fascinating electronic and optical numerous sensing, electronic, optoelectronic, and photoelectronic properties as a consequence of their dimensions and they may be interfaces, and also take time to cover the synthesis and easily synthesized from a wide range of materials. The dimensions characterization of nanoparticles and nanoparticle arrays. of these particles makes them ideal candidates for the nano- engineering of surfaces and the fabrication of functional nano- KEYWORDS: structures. In the last five years, much effort has been expended on colloids ´ interfaces ´ monolayers ´ nanostructures ´ sensors 1. Introduction The emerging disciplines of nanoengineering,[1] nanoelectron- optical,[7, 10±13] and catalytic[14] properties originating from their ics,[2] and nanobioelectronics[3] require suitably sized and func- quantum-scale dimensions.[15] tional building blocks with which to construct their architectures In order to tailor the new generation of nanodevices and and devices. This need has encouraged -

Designing a Nanoelectronic Circuit to Control a Millimeter-Scale Walking Robot

Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 McLean, Virginia Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 MITRE Nanosystems Group e-mail: [email protected] WWW: http://www.mitre.org/tech/nanotech Sponsor MITRE MSR Program Project No. 51MSR89G Dept. W809 Approved for public release; distribution unlimited. Copyright © 2004 by The MITRE Corporation. All rights reserved. Gates, Alexander Abstract A novel nanoelectronic digital logic circuit was designed to control a millimeter-scale walking robot using a nanowire circuit architecture. This nanoelectronic circuit has a number of benefits, including extremely small size and relatively low power consumption. These make it ideal for controlling microelectromechnical systems (MEMS), such as a millirobot. Simulations were performed using a SPICE circuit simulator, and unique device models were constructed in this research to assess the function and integrity of the nanoelectronic circuit’s output. It was determined that the output signals predicted for the nanocircuit by these simulations meet the requirements of the design, although there was a minor signal stability issue. A proposal is made to ameliorate this potential problem. Based on this proposal and the results of the simulations, the nanoelectronic circuit designed in this research could be used to begin to address the broader issue of further miniaturizing circuit-micromachine systems. i Gates, Alexander I. Introduction The purpose of this paper is to describe the novel nanoelectronic digital logic circuit shown in Figure 1, which has been designed by this author to control a millimeter-scale walking robot. -

DNA-Based Artificial Nanostructures: Fabrication, Properties And

(Invited) Chapter V in “Handbook of Nanostructured Biomaterials and Their Applications in Nanobiotechnology,” Vols. 1-2 (ISBN: 1-58883-033-0), edited by Nalwa, American Scientific Publishers (2005). DNA-based Artificial Nanostructures: Fabrication, Properties, and Applications Young Sun and Ching-Hwa Kiang* Department of Physics & Astronomy, Rice University 6100 Main Street - MS61, Houston, TX 77005, USA Phone: (713) 348-4130, Fax: (713) 348-4150, E-mail: [email protected] Keywords: DNA; nanostructure; self-assembly; nanoparticle; carbon nanotube; biosensor. *To whom correspondence should be addressed: [email protected]. 1 Table of Content 1. Introduction 2. DNA fundamentals 3. Attachment of DNA to surface 4. Fabrication of nanostructures using DNA 4.1 Nanostructures of pure DNA 4.2 DNA-based assembly of metal nanoparticles 4.3 Construction of semiconductor particle arrays using DNA 4.4 DNA-directed nanowires 4.5 DNA-functionalized carbon nanotubes 4.6 Field-transistor based on DNA 4.7 Nanofabrication using artificial DNA 5. DNA-based nanostructures as biosensors 6. Properties of DNA-linked gold nanoparticles 6.1 Aggregation of DNA-modified gold nanoparticles 6.2 Melting of DNA-linked gold nanoparticle aggregations 6.3 Effects of external variables on the melting properties 7. Conclusion 2 1. Introduction The integration of nanotechnology with biology and bioengineering is producing many advances. The essence of nanotechnology is to produce and manipulate well- defined structures on the nanometer scale with high accuracy. Conventional technologies based on the "top-down” approaches, such as the photolithographyic method, are difficult to continue to scale down due to real physical limitations including size of atoms, wavelengths of radiation used for lithography, and interconnect schemes. -

Metal and Semiconductor Nanoparticle Self-Assembly

Metal and Semiconductor Nanoparticle Self-Assembly by G. Daniel Lilly A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Chemical Engineering) in The University of Michigan 2009 Doctoral Committee: Professor Nicholas A. Kotov, Chair Professor Sharon C. Glotzer Professor Xiaoqing Pan Assistant Professor Suljo Linic © G. Daniel Lilly 2009 To my wife, Michelle M. Lilly, Ph.D. To my mother and father, Nancy N. and G. Bud Lilly ii ACKNOWLEDGEMENTS I would like to thank my loving and lovely wife Michelle for her support through the process of obtaining my Ph.D. If not for her support and advice I most likely would not have finished this process. I value her as a friend and partner and am forever appreciative of her actions. I would also like to thank my parents for laying the groundwork in my life to accomplish this. They taught me the value of hard work and persistence when reaching toward your goals, and without these lessons I most likely would not have even gone to graduate school, much less finished. I am appreciative for all the help and support my fellow lab members have given me over the last five years. Former lab members Jaebeom Lee, Zhiyong Tang, Paul Podsiadlo, Bongsup Ship, Jungwoo Lee and Kevin Critchley helped teach me new lab techniques, NP synthesis and conjugation techniques, and numerous analysis procedures, and allowed me a venue to discuss my hypotheses concerning these approaches. Current lab members Meghan Cuddihy, Edward Jan, Peter Ho, Ashish Agarwal, Christine Andres, Jian Zhu, Huanan Zhang, Elizabeth Stewart, Yichun Wang, Inigo Alvarez, Shimei Xu, and Anna Fernandez aided with various collaborations, techniques, procedures, and experiences for which I am grateful. -

Directed Self-Assembly of Block Copolymers for the Fabrication of Nanomechanical Structures

ADVERTIMENT. Lʼaccés als continguts dʼaquesta tesi queda condicionat a lʼacceptació de les condicions dʼús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page_id=184 ADVERTENCIA. El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/ WARNING. The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en Directed self-assembly of block copolymers for the fabrication of nanomechanical structures Christian Pinto Gómez Dissertation for the degree of Doctor in Electronic and Telecommunication Engineering Advisor: Marta Fernández Regúlez Academic tutor: Joan Bausells Roigé Department of Electronic Engineering Universitat Autònoma de Barcelona 2021 This is to certify that this thesis has been written by Christian Pinto Gómez and is submitted to obtain the degree of Doctor of Philosophy in Electronic and Telecommunication Engineering under guidance and supervision of Dr. Marta Fernández Regúlez (IMB-CNM, CSIC). Advisor: Marta Fernández Regúlez Christian Pinto Gómez Academic tutor: Joan Bausells Roigé i ii Abstract The main goal of this dissertation, entitled “Directed self-assembly of block copolymers for the fabrication of nanomechanical structures”, is to demonstrate the possibility of fabricating nanomechanical functional structures by employing the directed self- assembly (DSA) of block copolymers (BCPs) as a nanopatterning tool. DSA is a bottom-up nanolithography technique based on the ability of BCPs to segregate into domains at the micro/nanoscale, and it has attracted high interest due to its inherent simplicity, high throughput, low cost and potential for sub-10 nm resolution. -

Viral Surveillance and Discovery (Current Opinion in Virology)

Available online at www.sciencedirect.com Viral surveillance and discovery Walter Ian Lipkin and Cadhla Firth The field of virus discovery has burgeoned with the advent of applications given recent improvements in drugs and high throughput sequencing platforms and bioinformatics vaccines. The lack of effective therapies once made programs that enable rapid identification and molecular the diagnosis of viral infection primarily an academic characterization of known and novel agents, investments in exercise; however, the expanding armamentarium of global microbial surveillance that include wildlife and domestic countermeasures for specific viruses promises unprece- animals as well as humans, and recognition that viruses may be dented opportunities to reduce morbidity, mortality and implicated in chronic as well as acute diseases. Here we review the economic costs of viral infections. methods for viral surveillance and discovery, strategies and pitfalls in linking discoveries to disease, and identify Tools for the hunt opportunities for improvements in sequencing instrumentation Tissue culture and analysis, the use of social media and medical informatics Although this classical method for viral discovery is dis- that will further advance clinical medicine and public health. missed by some investigators as cumbersome, expensive Addresses and quaint, we continue to use it for several reasons. First, Center for Infection and Immunity, Mailman School of Public Health of the growth of an agent in culture provides an excellent Columbia University, 722 West 168th Street, New York, NY 10025, USA source of enriched template for molecular characteriz- ation. Additionally, having an inoculum for animal model Corresponding author: Lipkin, Walter Ian ([email protected]) studies, a cell-based assay for serology or a titered stock for neutralization tests greatly aids the pursuit of the proof of disease causation [11–14]. -

Nanoscience and Genomics

NANOSCIENCE AND GENOMICS LIST OF NEW COURSES (2020) Sl. No Course Code Name of the Course Credits 1 20NT3001 Vacuum and Thin Film Technology 3:0:0 2 20NT3002 Semiconductors, Instrumentation and Advanced Design 3:0:0 3 20NT3003 Analytical Methods and Spectroscopy 3:0:0 4 20NT3004 Nanomaterials in Biology and Medicine 3:0:0 5 20NT3005 Synthesis and Functionalization of Nanomaterials 3:0:0 6 20NT3006 Biomolecules in Nanoscience 3:0:0 7 20NT3007 Thin Film Lab 0:0:2 8 20NT3008 Synthesis and Functionalization of Nanomaterials Laboratory 0:0:2 9 20NT3009 Magnetic Nanomaterials 3:0:0 10 20NT3010 Human Physiology 3:0:0 11 20NT3011 Nanoelectronics and Micro-Nanofabrications 3:0:0 12 20NT3012 Microbiology and Immunology 3:0:0 13 20NT3013 Self-assembled and Functional Nanostructures 3:0:0 14 20NT3014 Molecular and Nanoscale Thermodynamics 3:0:0 15 20NT3015 Nanoelectronics Lab 0:0:2 16 20NT3016 Characterization of Nanomaterials Laboratory 0:0:2 17 20NT3017 Luminescent Nanomaterials 3:0:0 18 20NT3018 Commercialization of Nanotechnology Products 3:0:0 19 20NT3019 Cancer Nanomedicine 3:0:0 20 20NT3020 Nanomaterial-Based Energy Devices 3:0:0 21 20NT3021 Nano-Bio Lab 0:0:2 L T P C 20NT3001 VACUUM AND THIN FILM TECHNOLOGY 3 0 0 3 Course objectives: 1. To introduce students to the theory and practice of high vacuum systems as well as thin film deposition 2. To study the physical behavior of gases and the technology of vacuum systems including system operation and design 3. To learn the thin film deposition techniques including physical, chemical methods and its applications in various fields. -

Aligned Silicon Nanofins Via the Directed Self-Assembly of PS-B

Nanoscale Accepted Manuscript This is an Accepted Manuscript, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication. Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available. You can find more information about Accepted Manuscripts in the Information for Authors. Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal’s standard Terms & Conditions and the Ethical guidelines still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this Accepted Manuscript or any consequences arising from the use of any information it contains. www.rsc.org/nanoscale Page 1 of 13 Nanoscale Journal Name RSCPublishing ARTICLE Aligned Silicon Nanofins via the Directed Self- Assembly of PS-b-P4VP Block Copolymer and Metal Cite this: DOI: 10.1039/x0xx00000x Oxide Enhanced Pattern Transfer Cian Cummins,a* Anushka Gangnaik,b Roisin A. Kelly,b Dipu Borah, a,c John Received 00th b b b b,c O‟Connell, Nikolay Petkov, Yordan M. Georgiev, Justin D. Holmes and Accepted 00th Michael A. Morrisa,c* DOI: 10.1039/x0xx00000x „Directing‟ block copolymer (BCP) patterns is a possible option for future semiconductor www.rsc.org/ device patterning, but pattern transfer of BCP masks is somewhat hindered by the inherently low etch contrast between blocks. -

Nanolithography

Chapter 8 Nanolithography Gunasekaran Venugopal and Sang-Jae Kim Additional information is available at the end of the chapter http://dx.doi.org/10.5772/55527 1. Introduction Nanolithography is the branch of nanotechnology concerned with the study and application of the nanofabrication of nanometer-scale structures, meaning nanopatterning with at least one lateral dimension between the size of an individual atom and approximately 100 nm. The term nanolithography is derived from the Greek words “nanos”, meaning dwarf; “lithos”, meaning rock or stone; and “graphein” meaning to write. Therefore the literal translation is "tiny writing on stone", however nowadays one understands something different whenever this term is associated with nanotechnology. Nanolithography is used e.g. during the nano‐ fabrication of leading-edge semiconductor integrated circuits (nanocircuitry), for nanoelec‐ tromechanical systems (NEMS) or for almost any other fundamental application across various scientific disciplines in nanoresearch. This technology can be suitable to use in nanofabrication of various semiconducting Integrated Circuits (ICs), NEMS and for various applications in research. The modification in semicon‐ ductor chips at the nano-scale (in the range of 10-9 meter) is also possible. This method is contrasting to various existing nanolithographic techniques like Photolithography (Venugo‐ pal, 2011), Nanoimprint lithography (NIL), Scanning Probe Lithography (SPL), Atomic Force Microscope (AFM) nanolithography, Extreme Ultraviolet Lithography (EUVL) and X-ray Lithography. In this chapter, the various nanolithographic fabrication techniques will be discussed in detail in which we will focus the various nano-patterning techniques/procedures suitable for device fabrication and their engineering applications. This technique is mainly used for nanofabrica‐ tion. -

Coherent Control of Plasmon Propagation in a Nanocircuit

PHYSICAL REVIEW APPLIED 1, 014007 (2014) Coherent Control of Plasmon Propagation in a Nanocircuit Christian Rewitz,1 Gary Razinskas,2 Peter Geisler,2 Enno Krauss,2 Sebastian Goetz,1 Monika Pawłowska,1 † Bert Hecht,2,3,* and Tobias Brixner1,3, 1Institut für Physikalische und Theoretische Chemie, Universität Würzburg, Am Hubland, 97074 Würzburg, Germany 2Nano-Optics and Biophotonics Group, Experimentelle Physik 5, Universität Würzburg, Am Hubland, 97074 Würzburg, Germany 3Röntgen Center for Complex Material Systems (RCCM), Am Hubland, 97074 Würzburg, Germany (Received 12 December 2013; published 27 February 2014) The miniaturization of optical devices is a prerequisite for broadband data-processing technology to compete with cutting-edge nanoelectronic circuits. For these future nano-optical circuits, controlling the spatial and temporal evolution of surface plasmons, i.e., propagating optical near fields at metal-insulator interfaces, is a key feature. Here, we design, optimize, and fabricate a nanoscale directional coupler with one input and two output ports, a device that is an essential element of nano-optical circuits. The directional coupler is based on a two-wire transmission line supporting two plasmonic eigenmodes that can be selectively excited. By manipulating the input polarization of ultrashort pulses and pulse pairs and by characterizing the light emitted from both output ports, we demonstrate open-loop ultrafast spatial and spatiotemporal coherent control of plasmon propagation. Because of the intuitive and optimized design, which exploits a controlled near-field interference mechanism, varying the linear input polarization is enough to switch between both output ports of the nanoscale directional coupler. Since we exploit the interference of a finite spectrum of eigenmodes, our experiments represent a very intuitive classical analogue to quantum control in molecules. -

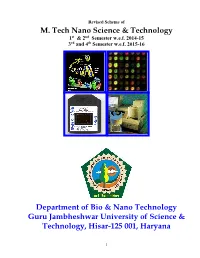

M. Tech Nano Science & Technology Department Of

Revised Scheme of M. Tech Nano Science & Technology 1st & 2nd Semester w.e.f. 2014-15 rd th 3 and 4 Semester w.e.f. 2015-16 Department of Bio & Nano Technology Guru Jambheshwar University of Science & Technology, Hisar-125 001, Haryana 1 REVISED SCHEME OF M. Tech (NANO SCIENCE & TECHNOLOGY) w.e.f 2014-15 Program core (PC) Program Elective (PE) Total Credit 84 8 92 FIRST SEMESTER Sr. No. Course No. Title L P Credits 1 MNL-701 Introduction to Biotechnology & Nanotechnology 5 0 5 2 MNL -702 Bionanotechnology-An Introduction 5 0 5 3 MNL -703 Physics & Chemistry of Solids 5 0 5 4 MNL-704 Quantum & Statistical Mechanics 5 0 5 5 MNP-705 (Lab-I Basic Techniques in Bionanotechnology) 0 12 6 Total 20 12 26 SECOND SEMESTER Sr. No. Course No. Title L P Credits 1 MNL -711 Carbon based Nanostructures & Thin Films 4 0 4 2 MNL -712 Nanomaterials- Synthesis, Properties & Applications 4 0 4 3 MNL -713 Instrumentation Techniques for Nanotechnology 4 0 4 4 MNL -714 Nanosensors and Nanodevices 4 0 4 5 MNL -715 Nanoparticles in Microorganisms & Biosystems 4 0 4 6 MNP-716 (Lab-II Nanomaterials/ CNT & Thin Films) 0 6 3 7 MNP-717 (Lab-III Advanced Instrumentation Techniques ) 0 6 3 Total 20 12 26 THIRD SEMESTER Sr. No. Course No. Title L P Credits 1 MNL – 721 to 722 *Program Elective-I 4 0 4 2 MNL – 723 to 724 *Program Elective-II 4 0 4 3 MNP-725 (Lab-IV Applied Nanotechnology) 0 12 6 4 MND -800 Thesis (starts) 0 6 6 5 MNS -791 Credit Seminar 2 Total 8 17 22 *For each of the Program Elective courses I and II Student can opt for any one out of the two courses FOURTH SEMESTER Sr. -

Fabrication and Manipulation of Metallic Nanofeatures and CVD Graphene Through Nanopatterning and Templating

Fabrication and Manipulation of Metallic Nanofeatures and CVD Graphene through Nanopatterning and Templating by Copyright 2014 Christina M. Edwards Submitted to the graduate degree program in Chemistry and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Doctor of Philosophy. Chairperson Cindy L. Berrie Michael A. Johnson Susan M. Lunte Timothy A. Jackson Prajna Dhar Date Defended: July 16, 2014 The Dissertation Committee for Christina M. Edwards certifies that this is the approved version of the following dissertation: Fabrication and Manipulation of Metallic Nanofeatures and CVD Graphene through Nanopatterning and Templating Chairperson Cindy L. Berrie Date Defended: July 16, 2014 ii Abstract Nanotechnology holds exciting potential to significantly advance research in many fields such as sensors, environmental sustainability and cleanup, energy harvesting and storage, as well as nanoelectronics. The resulting high demand for implementation into these areas has simultaneously created a large need for effective fabrication methods for nanostructured materials. It is important the fabrication methods are capable of significant control over size, orientation, and structural configuration of nanomaterials for effective function in these applications. Nanopatterning and templating are a promising means to achieve extreme selectivity over these parameters, and additionally be used as tools to control the growth and structure of large-scale materials through nanoscale manipulation. In this research, nanopatterning and templating are implemented to create metallic nanowire structures on surfaces of silicon substrates with highly selectivity over nanowire placement and design. Additionally, templating is incorporated in graphene growth on metallic substrates to influence the quality of graphene films,and further film patterning is used to improve the graphene electrical and optical properties.