Designs for Ultra-Tiny, Special-Purpose Nanoelectronic Circuits Shamik Das, Member, IEEE, Alexander J

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nanoparticle Arrays on Surfaces for Electronic, Optical, and Sensor Applications** Andrew N

18 WILEY-VCH-Verlag GmbH, D-69451 Weinheim, 2000 1439-4235/00/01/01 $ 17.50+.50/0 CHEMPHYSCHEM 2000,1,18±52 Nanoparticle Arrays on Surfaces for Electronic, Optical, and Sensor Applications** Andrew N. Shipway,[a] Eugenii Katz,[a] and Itamar Willner*[a] Particles in the nanometer size range are attracting increasing their organization on surfaces for the construction of functional attention with the growth of interest in nanotechnological interfaces. In this review, we address the research that has led to disciplines. Nanoparticles display fascinating electronic and optical numerous sensing, electronic, optoelectronic, and photoelectronic properties as a consequence of their dimensions and they may be interfaces, and also take time to cover the synthesis and easily synthesized from a wide range of materials. The dimensions characterization of nanoparticles and nanoparticle arrays. of these particles makes them ideal candidates for the nano- engineering of surfaces and the fabrication of functional nano- KEYWORDS: structures. In the last five years, much effort has been expended on colloids ´ interfaces ´ monolayers ´ nanostructures ´ sensors 1. Introduction The emerging disciplines of nanoengineering,[1] nanoelectron- optical,[7, 10±13] and catalytic[14] properties originating from their ics,[2] and nanobioelectronics[3] require suitably sized and func- quantum-scale dimensions.[15] tional building blocks with which to construct their architectures In order to tailor the new generation of nanodevices and and devices. This need has encouraged -

Biomedical Nanotechnology.Pdf

BIOMEDICAL NANOTECHNOLOGY BIOMEDICAL NANOTECHNOLOGY Edited by Neelina H. Malsch Boca Raton London New York Singapore CRC PRESS, a Taylor & Francis title, part of the Taylor and Francis Group. Published in 2005 by CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742 © 2005 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10987654321 International Standard Book Number-10: 0-8247-2579-4 (Hardcover) International Standard Book Number-13: 978-0-8247-2579-2 (Hardcover) Library of Congress Card Number 2005045702 This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use. No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers. For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. -

Fundamentals of Nanoelectronics (Fone)

ESF EUROCORES Programme Fundamentals of NanoElectronics (FoNE) Highlights European Science Foundation (ESF) Physical and Engineering Sciences (PESC) The European Science Foundation (ESF) is an The Physical and Engineering Sciences are key drivers independent, non-governmental organisation, the for research and innovation, providing fundamental members of which are 78 national funding agencies, insights and creating new applications for mankind. research performing agencies, academies and learned The goal of the ESF Standing Committee for Physical societies from 30 countries. and Engineering Sciences (PESC) is to become the The strength of ESF lies in its influential membership pan-European platform for innovative research and and in its ability to bring together the different domains competitive new ideas while addressing societal of European science in order to meet the challenges of issues in a more effective and sustainable manner. the future. The Committee is a unique cross-disciplinary Since its establishment in 1974, ESF, which has its group, with networking activities comprising a good headquarters in Strasbourg with offices in Brussels mix of experimental and theoretical approaches. and Ostend, has assembled a host of organisations It distinguishes itself by focusing on fundamental that span all disciplines of science, to create a research and engineering. PESC covers the following common platform for cross-border cooperation in broad spectrum of fields: chemistry, mathematics, Europe. informatics and the computer sciences, physics, ESF is dedicated to promoting collaboration in fundamental engineering sciences and materials scientific research, funding of research and science sciences. policy across Europe. Through its activities and instruments ESF has made major contributions to science in a global context. -

PDF Downloads

Engineering Advances, 2021, 1(1), 26-30 http://www.hillpublisher.com/journals/ea/ ISSN Online: ****-**** ISSN Print: ****-**** Nanofabrics—The Smart Textile Nida Tabassum Khan1,*, Muhammad Jibran Khan2 1Department of Biotechnology, Faculty of Life Sciences and Informatics, Balochistan University of Information Technology En- gineering and Management Sciences, (BUITEMS), Quetta, Pakistan. 2Department of Electrical Engineering, Faculty of Information and Communication Technology, Balochistan University of Infor- mation Technology Engineering and Management Sciences, (BUITEMS), Quetta, Pakistan. How to cite this paper: Nida Tabassum Khan, Muhammad Jibran Khan. (2021) Abstract Nanofabrics—The Smart Textile. Engi- Nanotechnology is tied in with improving and carrying the up and coming bril- neering Advances, 1(1), 26-30. DOI: 10.26855/ea.2021.06.005 liant answers for nanoscale-level merchandise. It is tied in with organizing the particles to change measurements and improvement attributes, for example, bril- Received: April 28, 2021 liant texture. These textures can help makers with the additional significance of Accepted: May 25, 2021 expectations for everyday comforts, visual intrigue, and framework needed inno- Published: June 18, 2021 vative creations. Particles of nano size may uncover unexpected qualities unlike *Corresponding author: Nida Tabas- the mass material. Nanotechnology has multifunctional highlights in the produc- sum Khan, Department of Biotechnol- tion of textures in the advancement of resistance stain and wrinkles, fire resistant, ogy, Faculty of Life Sciences and In- antimicrobial and antistatic properties, dampness guideline, bright security and formatics, Balochistan University of Information Technology Engineering discharge attributes. Inside the texture the nanomaterials could impact various and Management Sciences, characteristics, including decrease electrical conductivity, combustibility and (BUITEMS), Quetta, Pakistan. -

Engineered Carbon Nanotubes and Graphene for Nanoelectronics And

Engineered Carbon Nanotubes and Graphene for Nanoelectronics and Nanomechanics E. H. Yang Stevens Institute of Technology, Castle Point on Hudson, Hoboken, NJ, USA, 07030 ABSTRACT We are exploring nanoelectronic engineering areas based on low dimensional materials, including carbon nanotubes and graphene. Our primary research focus is investigating carbon nanotube and graphene architectures for field emission applications, energy harvesting and sensing. In a second effort, we are developing a high-throughput desktop nanolithography process. Lastly, we are studying nanomechanical actuators and associated nanoscale measurement techniques for re-configurable arrayed nanostructures with applications in antennas, remote detectors, and biomedical nanorobots. The devices we fabricate, assemble, manipulate, and characterize potentially have a wide range of applications including those that emerge as sensors, detectors, system-on-a-chip, system-in-a-package, programmable logic controls, energy storage systems, and all-electronic systems. INTRODUCTION A key attribute of modern warfare is the use of advanced electronics and information technologies. The ability to process, analyze, distribute and act upon information from sensors and other data at very high- speeds has given the US military unparalleled technological superiority and agility in the battlefield. While recent advances in materials and processing methods have led to the development of faster processors and high-speed devices, it is anticipated that future technological breakthroughs in these areas will increasingly be driven by advances in nanoelectronics. A vital enabler in generating significant improvements in nanoelectronics is graphene, a recently discovered nanoelectronic material. The outstanding electrical properties of both carbon nanotubes (CNTs) [1] and graphene [2] make them exceptional candidates for the development of novel electronic devices. -

The Views of Experts and the Public Regarding Societal Preferences for Innovation in Nanotechnology

The views of experts and the public regarding societal preferences for innovation in nanotechnology Nidhi Gupta Thesis committee Promoter Prof. Dr L.J. Frewer Professor emeritus, Food Safety and Consumer Behaviour Wageningen University Professor of Food & Society Newcastle University, UK Co-promotors Dr A.R.H. Fischer Assistant Professor, Marketing and Consumer Behaviour Group Wageningen University Dr F.W.H. Kampers Director, Biotechnology Center for Food and Health Innovation Wageningen University Other members Prof. Dr G. Antonides, Wageningen University Dr H.J.P Marvin, RIKILT, Wageningen University and Research Center Prof. Dr H. van Lente, Utrecht University Dr Q. Chaudhry, Food & Environment Research Agency (FERA), North Yorkshire,UK This research was conducted under the auspices of the Graduate School of Wageningen Social Sciences (WASS) The views of experts and the public regarding societal preferences for innovation in nanotechnology Nidhi Gupta Thesis submitted in fulfilment of the requirements for the degree of doctor at Wageningen University by the authority of the Rector Magnificus Prof. Dr M.J. Kropff, in the presence of the Thesis Committee appointed by the Academic Board to be defended in public on Monday 9 December 2013 at 1.30 p.m. in the Aula. Nidhi Gupta The views of experts and the public regarding societal preferences for innovation in nanotechnology, 188 pages PhD thesis, Wageningen University, Wageningen, NL (2013) With references, with summaries in English and Dutch ISBN: 978-94-6173-762-5 To Ma, Pa, Mannu and Mannat Contents A Abstract iii 1 General Introduction 1 1.1 Nanotechnology: exploring the future with key stakeholders . 3 1.2 Scope and outline of the thesis . -

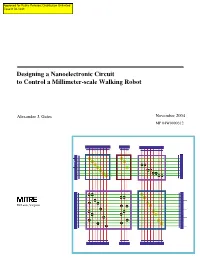

Designing a Nanoelectronic Circuit to Control a Millimeter-Scale Walking Robot

Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 McLean, Virginia Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 MITRE Nanosystems Group e-mail: [email protected] WWW: http://www.mitre.org/tech/nanotech Sponsor MITRE MSR Program Project No. 51MSR89G Dept. W809 Approved for public release; distribution unlimited. Copyright © 2004 by The MITRE Corporation. All rights reserved. Gates, Alexander Abstract A novel nanoelectronic digital logic circuit was designed to control a millimeter-scale walking robot using a nanowire circuit architecture. This nanoelectronic circuit has a number of benefits, including extremely small size and relatively low power consumption. These make it ideal for controlling microelectromechnical systems (MEMS), such as a millirobot. Simulations were performed using a SPICE circuit simulator, and unique device models were constructed in this research to assess the function and integrity of the nanoelectronic circuit’s output. It was determined that the output signals predicted for the nanocircuit by these simulations meet the requirements of the design, although there was a minor signal stability issue. A proposal is made to ameliorate this potential problem. Based on this proposal and the results of the simulations, the nanoelectronic circuit designed in this research could be used to begin to address the broader issue of further miniaturizing circuit-micromachine systems. i Gates, Alexander I. Introduction The purpose of this paper is to describe the novel nanoelectronic digital logic circuit shown in Figure 1, which has been designed by this author to control a millimeter-scale walking robot. -

DNA-Based Artificial Nanostructures: Fabrication, Properties And

(Invited) Chapter V in “Handbook of Nanostructured Biomaterials and Their Applications in Nanobiotechnology,” Vols. 1-2 (ISBN: 1-58883-033-0), edited by Nalwa, American Scientific Publishers (2005). DNA-based Artificial Nanostructures: Fabrication, Properties, and Applications Young Sun and Ching-Hwa Kiang* Department of Physics & Astronomy, Rice University 6100 Main Street - MS61, Houston, TX 77005, USA Phone: (713) 348-4130, Fax: (713) 348-4150, E-mail: [email protected] Keywords: DNA; nanostructure; self-assembly; nanoparticle; carbon nanotube; biosensor. *To whom correspondence should be addressed: [email protected]. 1 Table of Content 1. Introduction 2. DNA fundamentals 3. Attachment of DNA to surface 4. Fabrication of nanostructures using DNA 4.1 Nanostructures of pure DNA 4.2 DNA-based assembly of metal nanoparticles 4.3 Construction of semiconductor particle arrays using DNA 4.4 DNA-directed nanowires 4.5 DNA-functionalized carbon nanotubes 4.6 Field-transistor based on DNA 4.7 Nanofabrication using artificial DNA 5. DNA-based nanostructures as biosensors 6. Properties of DNA-linked gold nanoparticles 6.1 Aggregation of DNA-modified gold nanoparticles 6.2 Melting of DNA-linked gold nanoparticle aggregations 6.3 Effects of external variables on the melting properties 7. Conclusion 2 1. Introduction The integration of nanotechnology with biology and bioengineering is producing many advances. The essence of nanotechnology is to produce and manipulate well- defined structures on the nanometer scale with high accuracy. Conventional technologies based on the "top-down” approaches, such as the photolithographyic method, are difficult to continue to scale down due to real physical limitations including size of atoms, wavelengths of radiation used for lithography, and interconnect schemes. -

Metal and Semiconductor Nanoparticle Self-Assembly

Metal and Semiconductor Nanoparticle Self-Assembly by G. Daniel Lilly A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Chemical Engineering) in The University of Michigan 2009 Doctoral Committee: Professor Nicholas A. Kotov, Chair Professor Sharon C. Glotzer Professor Xiaoqing Pan Assistant Professor Suljo Linic © G. Daniel Lilly 2009 To my wife, Michelle M. Lilly, Ph.D. To my mother and father, Nancy N. and G. Bud Lilly ii ACKNOWLEDGEMENTS I would like to thank my loving and lovely wife Michelle for her support through the process of obtaining my Ph.D. If not for her support and advice I most likely would not have finished this process. I value her as a friend and partner and am forever appreciative of her actions. I would also like to thank my parents for laying the groundwork in my life to accomplish this. They taught me the value of hard work and persistence when reaching toward your goals, and without these lessons I most likely would not have even gone to graduate school, much less finished. I am appreciative for all the help and support my fellow lab members have given me over the last five years. Former lab members Jaebeom Lee, Zhiyong Tang, Paul Podsiadlo, Bongsup Ship, Jungwoo Lee and Kevin Critchley helped teach me new lab techniques, NP synthesis and conjugation techniques, and numerous analysis procedures, and allowed me a venue to discuss my hypotheses concerning these approaches. Current lab members Meghan Cuddihy, Edward Jan, Peter Ho, Ashish Agarwal, Christine Andres, Jian Zhu, Huanan Zhang, Elizabeth Stewart, Yichun Wang, Inigo Alvarez, Shimei Xu, and Anna Fernandez aided with various collaborations, techniques, procedures, and experiences for which I am grateful. -

Directed Self-Assembly of Block Copolymers for the Fabrication of Nanomechanical Structures

ADVERTIMENT. Lʼaccés als continguts dʼaquesta tesi queda condicionat a lʼacceptació de les condicions dʼús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page_id=184 ADVERTENCIA. El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/ WARNING. The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en Directed self-assembly of block copolymers for the fabrication of nanomechanical structures Christian Pinto Gómez Dissertation for the degree of Doctor in Electronic and Telecommunication Engineering Advisor: Marta Fernández Regúlez Academic tutor: Joan Bausells Roigé Department of Electronic Engineering Universitat Autònoma de Barcelona 2021 This is to certify that this thesis has been written by Christian Pinto Gómez and is submitted to obtain the degree of Doctor of Philosophy in Electronic and Telecommunication Engineering under guidance and supervision of Dr. Marta Fernández Regúlez (IMB-CNM, CSIC). Advisor: Marta Fernández Regúlez Christian Pinto Gómez Academic tutor: Joan Bausells Roigé i ii Abstract The main goal of this dissertation, entitled “Directed self-assembly of block copolymers for the fabrication of nanomechanical structures”, is to demonstrate the possibility of fabricating nanomechanical functional structures by employing the directed self- assembly (DSA) of block copolymers (BCPs) as a nanopatterning tool. DSA is a bottom-up nanolithography technique based on the ability of BCPs to segregate into domains at the micro/nanoscale, and it has attracted high interest due to its inherent simplicity, high throughput, low cost and potential for sub-10 nm resolution. -

Nanoelectronics

Highlights from the Nanoelectronics for 2020 and Beyond (Nanoelectronics) NSI April 2017 The semiconductor industry will continue to be a significant driver in the modern global economy as society becomes increasingly dependent on mobile devices, the Internet of Things (IoT) emerges, massive quantities of data generated need to be stored and analyzed, and high-performance computing develops to support vital national interests in science, medicine, engineering, technology, and industry. These applications will be enabled, in part, with ever-increasing miniaturization of semiconductor-based information processing and memory devices. Continuing to shrink device dimensions is important in order to further improve chip and system performance and reduce manufacturing cost per bit. As the physical length scales of devices approach atomic dimensions, continued miniaturization is limited by the fundamental physics of current approaches. Innovation in nanoelectronics will carry complementary metal-oxide semiconductor (CMOS) technology to its physical limits and provide new methods and architectures to store and manipulate information into the future. The Nanoelectronics Nanotechnology Signature Initiative (NSI) was launched in July 2010 to accelerate the discovery and use of novel nanoscale fabrication processes and innovative concepts to produce revolutionary materials, devices, systems, and architectures to advance the field of nanoelectronics. The Nanoelectronics NSI white paper1 describes five thrust areas that focus the efforts of the six participating agencies2 on cooperative, interdependent R&D: 1. Exploring new or alternative state variables for computing. 2. Merging nanophotonics with nanoelectronics. 3. Exploring carbon-based nanoelectronics. 4. Exploiting nanoscale processes and phenomena for quantum information science. 5. Expanding the national nanoelectronics research and manufacturing infrastructure network. -

Supporting Information

Electronic Supplementary Material (ESI) for RSC Advances. This journal is © The Royal Society of Chemistry 2016 Supporting Information For RSC Adv. “Green” Nano-Filters: Fine Nanofibers of Natural Protein for High Efficiency Filtration of Particulate Pollutants and Toxic Gases Hamid Souzandeh, Yu Wang*and Wei-Hong Zhong * School of Mechanical and Materials Engineering Washington State University, Pullman, WA 99164 (USA) E-mail: [email protected] [email protected] S0 Gelatin solution and nanofiber mat preparation. Gelatin was dissolved in mixed solvent (volume ratio, acetic acid : DI water = 80 : 20) with a concentration of 18 wt% at 65 °C. The mixed solvent was used to achieve a good electrospinning of the gelatin solution. With that ratio between water and acetic acid, it was found that a homogenous yellow solution and stable electrospinning of the solution can be achieved. The electrospinning of gelatin solution is a well- known process and the effect of viscosity on electrospinning of gelatin has been studied before.1 After the homogenous gelatin solution (18 wt%) is prepared, the nanofibers were spun at room temperature on an aluminum mesh substrate. The areal density of the nanofabrics was controlled by controlling the volume of the solution that was electrospun on the substrate. The gelatin nanofabrics possessed a thickness within the range of 8 – 20 μm. In particular, the sample with the best air filtration properties (areal density = 3.43 g/m2) possesses a thickness of about 16 μm. The gelatin nanofabrics can be handled manually even though they are not crosslinked, but it is challenging due to very high electrostatic charge of the nanofibers.