Pin Information for the Intel® Agilex™ AGFA022 Device

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

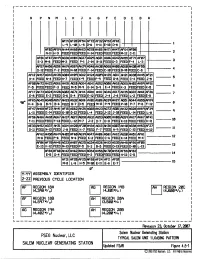

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

Radiation, Protection of the Public and the Environment (Poster Session 1) Origin and Migration of Cs-137 in Jordanian Soils

Major scientific thematic areas: TA6 – Radiation, Protection of the Public and the Environment (Poster session 1) Origin and Migration of Cs-137 in Jordanian Soils Ahmed Qwasmeh, Helmut W. Fischer IUP- Institute for Environmental Physics, Bremen University, Germany Abstract Whilst some research and publication has been done and published about natural radioactivity in Jordan, only one paper has been published about artificial radioactivity in Jordanian soils (Al Hamarneh 2003). It reveals high concentrations of 137Cs and 90Sr in some regions in the northwest section of Jordan. The origin of this contamination was not determined. Two sets of soil samples were collected and brought from northwest section of Jordan for two reasons, namely; the comparable high concentration of 137Cs in this region according to the above-mentioned paper and because most of the population concentrates in this region. The first set of samples was collected in April 2004 from eleven different sites of this region of Jordan. The second set of samples has been brought in July 2005 from six of the previous sites where we had found higher 137Cs contamination. The second set was collected as thinner sliced soil samples for further studying and to apply a suitable model for 137Cs migration in soil. Activity of 137Cs was measured using a HpGe detector of 50% relative efficiency and having resolution of 2keV at 1.33MeV. Activity of 90Sr was measured for the samples of four sites of the first set of samples, using a gas-filled proportional detector with efficiency of 21.3% cps/Bq. The total inventory of 137Cs in Bq/m2 has been calculated and the correlation between 137Cs inventory and annual rainfall and site Altitude has been studied. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

International Society for Soil Mechanics and Geotechnical Engineering

INTERNATIONAL SOCIETY FOR SOIL MECHANICS AND GEOTECHNICAL ENGINEERING This paper was downloaded from the Online Library of the International Society for Soil Mechanics and Geotechnical Engineering (ISSMGE). The library is available here: https://www.issmge.org/publications/online-library This is an open-access database that archives thousands of papers published under the Auspices of the ISSMGE and maintained by the Innovation and Development Committee of ISSMGE. Dynamic centrifuge model test for performance-based design of grid-form deep mixing walls supporting a tall building Junji Hamada & Tsuyoshi Honda Takenaka Research & Development Institute, Takenaka Corporation, Inzai, Chiba, Japan ABSTRACT Dynamic centrifuge model tests in the 50 g field were conducted to investigate a failure behavior of DMWs in liquefiable sand during large earthquakes. A miniature model of DMWs was made of soil-cement with an unconfined compressive strength of about 4,000 kPa in order to investigate the behavior/toughness of the DMWs after yield and failure on seismic performance. The DMWs model that support the superstructure’s weight of 206 kPa, the natural period of 0.6 second were set in a laminar shear box, and repeatedly tested by increasing the acceleration level of the input motion recorded at TAFT earthquakes. The relationship between shear stress and shear strain of the DMWs, namely the nonlinearity of the DMWs was investigated. No significant settlement of the structure was observed even if the normal and shear stresses in the DMWs were assumed to have locally reached the tensile or shear criteria of soil-cement. 1 INTRODUCTION potential for liquefaction mitigation. However, the local failures of the DMWs are not acceptable in the existing Grid-form DMWs (Deep cement Mixing Walls) which is method of allowable stress design. -

Greenhouse Or Windowsill Growing

Volume 57 Illustrated with more than 150 photographs and drawings- Dwarfed Fr'uit Trees 9y HAROLD BRADFORD TUKEY. In this authoritative guide the author identifies the important dwarfing rootstocks and describes their propagation and growth in the nursery, He discusses the selection and spacing of trees, bracing and trellising, and fruit trees grown under glass, as bonsai and as ornamentals. He also covers tree structure and physiology, modern scientific theories of dwarfing, soils, fertilizers , pollination, costs, yields, and the locations where dwarfed fruit trees are most likely to succeed. Originally published in 1964 and now reissued , this book is unique in its field. 150 black-and-white photographs, 7V2 x 10. Society member's price: $26.55 (Regularly $29.50). "Highly recommended for those interested in maintaining ornamental trees and shrubs." -UbraryJourna/ Insects That Feed on TliAT FEED ON INSECTS AND SHRUBS ~traled An l/Ius Trees and Shrubs By WARREN T. JOHNSON and HOWARD H, LYON. "A beautiful book. It is of high quality stylistically-of folio size, with good paper, of excellent design, and with every other page being a ~;A:";~~: full-color plate .. .. There is no question about the authority and competence of Johnson and Lyon _:.::~:._ _ or of the scientific validity of the book." -Choice. 212 color plates, 9 x 12. Society member}'s price: $31 .50 through June 30, 1978; $34.65 thereafter (Regularly $35.00; $38.50 after June 30 . Of related interest- - ----_._-------- --- __ ----J AGrowth Chamber Manual Environmental Control for Plants Edited by ROBEIH W. LANGHANS. Focusing primarily how to provide precise control, and how to keep a chamber on sophisticated growth chambers used for experimental running at optimum conditions. -

Information to Users

A quantitative figure-of-merit approach for optimization of an unmanned Mars Sample Return mission Item Type text; Thesis-Reproduction (electronic) Authors Preiss, Bruce Kenneth, 1964- Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction or presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 11/10/2021 06:15:49 Link to Item http://hdl.handle.net/10150/278010 INFORMATION TO USERS This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer. The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction. In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion. Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. -

The Eurasec Transport Corridors

Îñíîâíûå âûâîäû îáçîðà The EurAsEC Transport Corridors Sector Report March 2009 The Eurasian Development Bank is an international financial institution established to promote economic growth and integration processes in Eurasia. The Bank was founded by the intergovernmental agreement signed in January 2006 by the Russian Federation and the Republic of Kazakhstan. Negotiations are currently under way with a number of neighbouring countries. Electric power, water and energy, transportation infrastructure and high-tech and innovative industries are the key areas for Bank’s financing activity. The Bank, as part of its mission, provides quality research and analysis of contemporary development issues and trends in the region with particular focus on Eurasian integration. The Bank conducts regular conferences and round tables addressing various aspects of integration. In 2008, the Bank launched quarterly academic and analytical Journal of Eurasian Economic Integration and an annual EDB Eurasian Integration Yearbook. In addition, the Bank publishes regular analytical digests covering regional integration, development banks’ activities and investment projects in the post-Soviet space. The Bank’s Strategy and Research Department publishes detailed Sector and Country Analytical Reports. It also plans to realise a number of research and technical assistance projects. The “System of Indicators of Eurasian Integration” project is the first in the project pipeline. Address: Republic of Kazakhstan 050000, Almaty, Panfilov St. 98 Eurasian Development Bank Tel.: +7 (727) 244 40 44 ext. 6146 Fax: +7 (727) 244 65 70, 291 42 63 E-mail: [email protected] http://www.eabr.org No part of this publication may be reprinted or reproduced or utilized in any form, including reprinting and recording of any kind without due reference to this publication. -

Auction 14A Final Draft.Vp

OUR STAFF Stephen Album Paul Montz Director of Islamic & Early Indian Numismatics Director of World Coins Steve has been serving the Paul joined the staff in January numismatic community since 2011. He attended UC Davis 1960. In 1976 he began dealing from 1975-80, earning bachelor's nearly exclusively in Islamic and and master's degrees in Indian coins. He has authored Agricultural Science & several books including the Management and Agronomy, Catalogue of California Trade respectively. He began working Tokens, Volumes I & II in 1972 in the numismatic field in the and 1974 respectively. 1977 saw 1970's. In 1981, he founded the release of his complete rewrite of Marsden's Olde World Numismatics in Chico, CA, a business he Numismata Orientalia Illustrata, a guide to Islamic ran for 30 years, focusing on A-Z world coins, before and Oriental coins with values. In 1993 he published merging with Stephen Album Rare Coins. He has put A Checklist of Islamic Coins, which now in its second out price lists for many years and has been a fixture edition is the standard for collectors of Islamic coins. at major shows since the 1980's. Paul is a life Mr. Album is currently a senior fellow at the member of the American Numismatic Association Worcester College, Oxford, England, and in this and is a member of other organizations. He has been position has authored three of the ten volumes of the a contributing editor for the Standard Catalog of Sylloge of Islamic Coins in the Ashmolean (Museum) World Coins since 1998. Paul brings experience in beginning in 1999. -

The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV **

Eurasian Journal of Business and Economics 2008, 1 (2), 85-101. The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV ** Abstract This paper investigates an impact of road upgrading and improvement on overland trade in 18 out of 32 Asian Highway Network member countries. A regression based cost model was developed. The results indicate that approximately 6.5 billion US dollars is required to upgrade and improve surface condition of the selected roads with total length of 15,842 km. The gravity model approach was adopted to quantitatively evaluate overland trade expansion assuming pessimistic and optimistic scenarios: improvements in road quality indices up to 50 and up to 75, respectively. The results suggests that in the first scenario total intra-regional trade will increase by about 20 percent or 48.7 billion US dollars annually, while second scenario predicts that trade will increase by about 35 percent or 89.5 billion US dollars annually. Keywords: Asian Highway Network, road transport, gravity model. Jel Classification: F12, F15, F17. ∗ Advisor-Economist, UNDP Uzbekistan Country Office, Email: [email protected] ** Chief Engineer, Road Research Institute, Tashkent, Uzbekistan The views expressed in this paper are those of the author(s) and do not necessarily represent those of organizations the authors are associated with. Ziyodullo PARPIEV & Jamshid SODIKOV 1. Introduction In 1992, the United Nations Economic and Social Commission for Asia and the Pacific (ESCAP) endorsed the Asian Land Transport Infrastructure Development (ALTID) project comprising of the Asian Highway and the Trans-Asian Railway network. The formalization of the Asian Highway, through the Intergovernmental Agreement on Asian Highway Network (AHN), was adopted in November 2003. -

Growing Together Articulates a Number of Proposals That Can Help the Region Exploit Its Huge Untapped Potential for Regional Economic Integration

i Photo by Warren Field ii FOREWORD For the global economy, these are difficult times. The world is emerging from a crisis whose aftershocks continue to resonate – trapping some of the richest economies in recession and shaking the foundations of one of the world’s major currencies. Here at ESCAP, there are historical echoes. What is now the Economic and Social Commission for Asia and the Pacific was founded more than 60 years ago – also in the aftermath of a global crisis. The countries of Asia and the Pacific established their new Commission partly to assist them in rebuilding their economies as they came out of the yoke of colonialism and the Second World War. The newly established ECAFE, as ESCAP was called then, held a ministerial conference on regional economic cooperation in 1963 that resolved to set up the Asian Development Bank with the aim of assisting the countries in the region in rebuilding their economies. Fifty years later, the Asia-Pacific region is again at a crossroads, on this occasion seeking ways and means to sustain its dynamism in a dramatically changed global context in the aftermath of a global financial and economic crisis. An important change is the fact that, burdened by huge debts and global imbalances, the advanced economies of the West are no longer able to play the role of engines of growth for the Asia-Pacific region that they played in the past. Hence, the Asia-Pacific region has to look for new engines of growth. The secretariat of ESCAP has argued over the past few years that regional developmental challenges, such as poverty and wide disparities in social and physical infrastructure, can be turned into opportunities for sustaining growth in the future. -

Multi-Hazard Mitigation Plan 2020 Update

LUMMI NATION MULTI-HAZARD MITIGATION PLAN 2020 UPDATE Prepared For: Lummi Indian Business Council (LIBC) Funded By: U.S. Environmental Protection Agency Performance Partnership Grant (Grant No. BG-01J57901-0) Prepared By: Water Resources Division Lummi Natural Resources Department Contributors: Kara Kuhlman CFM, Water Resources Manager Andy Ross, LG, LHg, CFM, Water Resources Specialist III/Hydrologist Gerald Gabrisch GISP, GIS Manager Adopted by the Lummi Indian Business Council: September 15, 2020 Approved by the Federal Emergency Management Agency: October 1, 2020 This project has been funded wholly or in part by the United States Environmental Protection Agency under Assistance Agreement BG-01J57901-0 to the Lummi Nation. The contents of this document do not necessarily reflect the views and policies of the Environmental Protection Agency, nor does mention of trade names or commercial products constitute endorsement or recommendation for use. TABLE OF CONTENTS 1. Introduction ......................................................................................................................... 9 1.1. Goals and Objectives .....................................................................................................10 1.2. Sections .........................................................................................................................11 2. Planning Process ...............................................................................................................13 2.1. Plan Preparation ............................................................................................................13 -

Asian Highway Network Development

Mongolia Training Course of Railway Personnel BIMSTEC and Mekong-Ganga Cooperation Countries 20-31 March 2006 Asian Highway Network Development John Moon Transport and Tourism Division UNESCAP Development of the International Highway Linkages: Issues and Challenges • Standards and condition of infrastructure • Maintenance and upgrading of infrastructure • Financing development and maintenance of highway infrastructure • Facilitation of border crossings • Coordination among countries and agencies 2 Kazakhstan Asian Highway • Conceived in 1959 • Revitalized in 1992; ALTID • Goal: To promote regional cooperation/trade • Criteria for identification of routes: – Capital to capital links – Industrial and agricultural centres – Sea, river and air ports – Container terminals & depots – Tourism attractions • Maximize use of existing infrastructure • Coordinated plan for development Formulation of the Asian Highway 141,000 km, 32 countries North-East Asia 2002 Central Asia 1995 South East and South Asia 19934 Intergovernmental Agreement Turkey • Contracting Parties – Adopt AH network – Negotiating procedures – Conform to AH design standards – Display AH signs • Working Group on the Asian Highway – Provides negotiating forum – Proposals for revisions of network • 28 member States have signed and 18 ratified, approved or accepted the Agreement – Afghanistan, Armenia, Azerbaijan, Bhutan, Cambodia, China, Georgia, India, Japan, Mongolia, Myanmar, Pakistan, Republic of Korea, Russian Federation, Sri Lanka, Thailand, Uzbekistan and Viet Nam. • Agreement