1 2 3 4 5 6 7 8 9 10 11 12 13 S5-155U Cpu 948 Simatic S5

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Proposal for Addition of Group Mark Symbol Introduction

Proposal for addition of Group Mark symbol Ken Shirriff github.com/shirriff/groupmark Feb 14, 2015 Abstract The group mark symbol was part of the character set of important computers of the 1960s and 1970s, such as the IBM 705, 7070, 1401 and 1620. Books about these computers and manuals for them used the symbol to represent the group mark in running text. Unfortunately, this symbol does not exist in Unicode, making it difficult to write about technical details of these historical computers. Introduction The group mark was introduced in the 1950s as a separator character for I/O operations. In written text, the group mark is indicated by the symbol: . Unicode doesn't include this symbol, which is inconvenient when writing about the group mark or the character set of these computers. The group mark became part of IBM's Standard BCD Interchange Code (BCDIC) in 1962. [1, page 20 and figure 56]. This standard was used by the IBM 1401, 1440, 1410, 1460, 7010, 7040, and 7044 data processing systems [2]. The BCDIC standard provided consistent definitions of codes and the relation between these codes and printed symbols, including uniform graphics for publications.[2, page A-2]. Unicode can represent all the characters in BCDIC, except for the group mark. This proposal is for a Unicode code point for the group mark for use in running text with an associated glyph . This is orthogonal to the use of the group mark as a separator in data files. While the proposed group mark could be used in data files, that is not the focus of this proposal. -

DS8108 Digital Scanner Product Reference Guide (En)

DS8108 Digital Scanner Product Reference Guide MN-002926-02 DS8108 DIGITAL SCANNER PRODUCT REFERENCE GUIDE MN-002926-02 Revision A March 2018 ii DS8108 Digital Scanner Product Reference Guide No part of this publication may be reproduced or used in any form, or by any electrical or mechanical means, without permission in writing from Zebra. This includes electronic or mechanical means, such as photocopying, recording, or information storage and retrieval systems. The material in this manual is subject to change without notice. The software is provided strictly on an “as is” basis. All software, including firmware, furnished to the user is on a licensed basis. Zebra grants to the user a non-transferable and non-exclusive license to use each software or firmware program delivered hereunder (licensed program). Except as noted below, such license may not be assigned, sublicensed, or otherwise transferred by the user without prior written consent of Zebra. No right to copy a licensed program in whole or in part is granted, except as permitted under copyright law. The user shall not modify, merge, or incorporate any form or portion of a licensed program with other program material, create a derivative work from a licensed program, or use a licensed program in a network without written permission from Zebra. The user agrees to maintain Zebra’s copyright notice on the licensed programs delivered hereunder, and to include the same on any authorized copies it makes, in whole or in part. The user agrees not to decompile, disassemble, decode, or reverse engineer any licensed program delivered to the user or any portion thereof. -

Iso/Iec Jtc1/Sc 22/Wg 20 N 619665

ISO/IEC JTC1/SC 22/WG 20 N 619665 Date: 16 November 19981999-04-21 ISO ORGANISATION INTERNATIONALE DE NORMALISATION INTERNATIONAL ORGANIZATION FOR STANDARDIZATION ÌÅÆÄÓÍÀÐÎÄÍÀß ÎÐÃÀÍÈÇÀÖÈß ÏÎ ÑÒÀÍÄÀÐÒÈÇÀÖÈÈ CEI (IEC) COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE INTERNATIONAL ELECTROTECHNICAL COMMISSION ÌÅÆÄÓ•€•Ž„ÍÀß ÇËÅÊÒÐÎÒÅÕÍÈ×ÅÑÊÀß ÊÎÌÈÑÑÈß Title Proposed editorial changes to ISO/IEC FCD 14651.2 - International String Ordering - Method for comparing Character Strings and Description of the Common Template Tailorable Ordering [ISO/CEI CD 14651 - Classement international de chaînes de caractères - Méthode de comparaison de chaînes de caractères et description du modèle commun d’ordre de classement] Status: Final Committee DocumentExpert contribution Reference: SC22/WG20 N 568R (Disposition of comments on first FCD ballot)619 Date: 1998-11-161999-04-21 Project: 22.30.02.02 Editor: Alain LaBonté Gouvernement du Québec Secrétariat du Conseil du trésor 875, Grande-Allée Est, Secteur 3C Québec, QC G1R 5R8 CanadaMichael Everson Email: [email protected]@indigo.ie ISO/IEC 14651:1999(E) ÓISO/IEC Contents: FOREWORD......................................................................................................................................iii INTRODUCTION ................................................................................................................................iv 1 Scope .............................................................................................................................................1 -

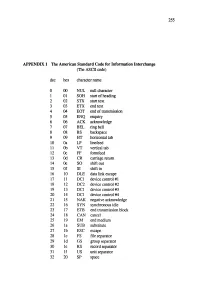

The ASCII Code)

255 APPENDIX! The American Standard Code for Information Interchange (The ASCII code) dec hex character name 0 00 NUL null character 1 01 SOH start of heading 2 02 STX start text 3 03 ETX end text 4 04 EOT end of transmission 5 05 ENQ enquiry 6 06 ACK acknowledge 7 07 BEL ring bell 8 08 BS backspace 9 09 HT horiwntal tab 10 Oa LF linefeed 11 Ob VT vertical tab 12 Oc FF fonnfeed 13 Od CR carriage return 14 Oe SO shift out 15 Of SI shift in 16 10 OLE data link escape 17 11 DCI device control #1 18 12 DC2 device control #2 19 13 DC1 device control #3 20 14 DCI device control #4 21 15 NAK negative acknowledge 22 16 SYN synchronous idle 23 17 ETB end transmission block 24 18 CAN cancel 25 19 EM end medium 26 1a SUB substitute 27 Ib ESC escape 28 lc FS file separator 29 Id GS group separator 30 Ie RS record separator 31 If US unit separator 32 20 SP space 256 APPENDICES The ASOI code (contd.) dec hex char dec hex char dec hex char 33 21 65 41 A 97 61 a 34 22 .. 66 42 B 98 62 b 35 23 # 67 43 C 99 63 c 36 24 $ 68 44 D 100 64 d 37 25 % 69 45 E 101 65 e 38 26 & 70 46 F 102 66 f 39 27 71 47 G 103 67 g 40 28 ( 72 48 H 104 68 h 41 29 ) 73 49 I 105 69 i 42 2a * 74 4a J 106 6a j 43 2b + 75 4b K 107 6b k 44 2c 76 4c L 108 6c I 45 2d - 77 4d M 109 6d m 46 2e 78 4e N 110 6e n 47 2f / 79 4f 0 111 6f 0 48 30 0 80 50 P 112 70 P 49 31 1 81 51 Q 113 71 q 50 32 2 82 52 R 114 72 r 51 33 3 83 53 S 115 73 s 52 34 4 84 54 T 116 74 t 53 35 5 85 55 U 117 75 u 54 36 6 86 56 V 118 76 v 55 37 7 87 57 W 119 77 w 56 38 8 88 58 X 120 78 x 57 39 9 89 59 Y 121 79 Y 58 3a -

ASCII, Unicode, and in Between Douglas A. Kerr Issue 3 June 15, 2010 ABSTRACT the Standard Coded Character Set ASCII Was Formall

ASCII, Unicode, and In Between Douglas A. Kerr Issue 3 June 15, 2010 ABSTRACT The standard coded character set ASCII was formally standardized in 1963 and, in its “complete” form, in 1967. It is a 7-bit character set, including 95 graphic characters. As personal computers emerged, they typically had an 8-bit architecture. To exploit that, they typically came to use character sets that were “8-bit extensions of ASCII”, providing numerous additional graphic characters. One family of these became common in computers using the MS-DOS operating system. Another similar but distinct family later became common in computers operating with the Windows operating system. In the late 1980s, a true second-generation coded character set, called Unicode, was developed, and was standardized in 1991. Its structure provides an ultimate capacity of about a million graphic characters, catering thoroughly to the needs of hundreds of languages and many specialized and parochial uses. Various encoding techniques are used to represent characters from this set in 8- and 16-bit computer environments. In this article, we will describe and discuss these coded character sets, their development, their status, the relationships between them, and practical implications of their use. Information is included on the entry, in Windows computer systems, of characters not directly accessible from the keyboard. BEFORE ASCII As of 1960, the interchange of data within and between information communication and processing systems was made difficult by the lack of a uniform coded character set. Information communication in the traditional “teletypewriter” sense generally used a 5-bit coded character set, best described as the “Murray code” (although as a result of historical misunderstandings it is often called the “Baudot code”). -

Mysql Globalization Abstract

MySQL Globalization Abstract This is the MySQL Globalization extract from the MySQL 8.0 Reference Manual. For legal information, see the Legal Notices. For help with using MySQL, please visit the MySQL Forums, where you can discuss your issues with other MySQL users. Document generated on: 2021-09-27 (revision: 70895) Table of Contents Preface and Legal Notices .................................................................................................................. v 1 Character Sets, Collations, Unicode ................................................................................................. 1 1.1 Character Sets and Collations in General .............................................................................. 2 1.2 Character Sets and Collations in MySQL ............................................................................... 3 1.2.1 Character Set Repertoire ........................................................................................... 5 1.2.2 UTF-8 for Metadata ................................................................................................... 7 1.3 Specifying Character Sets and Collations .............................................................................. 8 1.3.1 Collation Naming Conventions .................................................................................... 9 1.3.2 Server Character Set and Collation .......................................................................... 10 1.3.3 Database Character Set and Collation ..................................................................... -

Reference Card

eg1 Mm#$w&m" SPECIAL SYMBOLS SYMBOL IO.COLUMN USE PUNCH * ln col!mn lr indicatesprima'y contiol statement In any other columnr indicalescontinuation of conlrolstatement A I 1.7-8 Separates notes t!om slatemenl on primary conlol card Indicat€s terminalion of Darameterson PRAM contol card 0-3-8 S€parales specification fields: two commas (,,) in succession requiredto indicateblank specification{except last) ! In columnl, lollowedby mnemonicoperator: indicatessecondary (blank) contol statementand delimits its operatol In prinary conlol statement: delimitsoptions tield; two blanks(ti) il successionrequirsd for blank optionfield lollowedby specilications Indicates termination of slatement 0i SeDaratessubfields within a so€cification PFIIMARY CC]NTROL PRTXARYCOtTiOf iCALLtoptionsiname/vers ion, I ibrary,ti le,parameter,parameter,... ccoFoptionstname'versron,ribrary aE-) option3: X: abort job il no find or activationot unit recordroutrne optioni: A-E: loSicallest switches no X: use no'maloutout unit fecordrouline if io lind or activatlonand iSnoreICAL R = clerr switches tilc: P : primary output steam H, M, or L = serviceand selectionpfioiity (high,medium, or low) S = secondary output stean XorY P = go-column FORTRAN input cards dCOREtopl i onstl ibrary,name,/ve rs ion,v,v,v,...v O ' COREttn in imum,har.m!m options: A = coileclion to memory localion: v: conectron address '€lative to system base address/co(ections nininum: ninimrn erlension (no, ot words) of core r€quir€d lor task €lemenl (NoA) norimufr: marim!m exlensiondesir€d X, Z, ot P = cofrect -

Number Systems

Number Systems PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 09 Mar 2013 02:39:37 UTC Contents Articles Two's complement 1 Ones' complement 10 Binary-coded decimal 14 Gray code 24 Hexadecimal 39 Octal 50 Binary number 55 References Article Sources and Contributors 70 Image Sources, Licenses and Contributors 72 Article Licenses License 73 Two's complement 1 Two's complement Two's complement is a mathematical operation on binary numbers, as well as a binary signed number representation based on this operation. The two's complement of an N-bit number is defined as the complement with respect to 2N, in other words the result of subtracting the number from 2N. This is also equivalent to taking the ones' complement and then adding one, since the sum of a number and its ones' complement is all 1 bits. The two's complement of a number behaves like the negative of the original number in most arithmetic, and positive and negative numbers can coexist in a natural way. In two's-complement representation, negative numbers are represented by the two's complement of their absolute value;[1] in general, negation (reversing the sign) is performed by taking the two's complement. This system is the most common method of representing signed integers on computers.[2] An N-bit two's-complement numeral system can represent every integer in the range −(2N − 1) to +(2N − 1 − 1) while ones' complement can only represent integers in the range −(2N − 1 − 1) to +(2N − 1 − 1). -

DS3678 Product Reference Guide (EN)

DS3678 Digital Scanner Product Reference Guide MN-002689-01 DS3678 DIGITAL SCANNER PRODUCT REFERENCE GUIDE MN-002689-01 Revision A June 2016 ii DS3678 Digital Scanner Product Reference Guide No part of this publication may be reproduced or used in any form, or by any electrical or mechanical means, without permission in writing from Zebra. This includes electronic or mechanical means, such as photocopying, recording, or information storage and retrieval systems. The material in this manual is subject to change without notice. The software is provided strictly on an “as is” basis. All software, including firmware, furnished to the user is on a licensed basis. Zebra grants to the user a non-transferable and non-exclusive license to use each software or firmware program delivered hereunder (licensed program). Except as noted below, such license may not be assigned, sublicensed, or otherwise transferred by the user without prior written consent of Zebra. No right to copy a licensed program in whole or in part is granted, except as permitted under copyright law. The user shall not modify, merge, or incorporate any form or portion of a licensed program with other program material, create a derivative work from a licensed program, or use a licensed program in a network without written permission from Zebra. The user agrees to maintain Zebra’s copyright notice on the licensed programs delivered hereunder, and to include the same on any authorized copies it makes, in whole or in part. The user agrees not to decompile, disassemble, decode, or reverse engineer any licensed program delivered to the user or any portion thereof. -

Lecture Packed ASCII Arithmetic

Assembly Language for Intel-Based Computers, 4th Edition Kip R. Irvine Unpacked and Packed Integers Slides prepared by Kip R. Irvine Revision date: 07/11/2002 Modified 2006, Dr. Nikolay Metodiev Sirakov • Chapter corrections (Web) Assembly language sources (Web) (c) Pearson Education, 2002. All rights reserved. You may modify and copy this slide show for your personal use, or for use in the classroom, as long as this copyright statement, the author's name, and the title are not changed. ASCII and Packed Decimal Arithmetic • Unpacked BCD • ASCII Decimal • AAA Instruction • AAS Instruction • AAM Instruction • AAD Instruction • Packed Decimal Integers • DAA Instruction • DAS Instruction Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples 2 Unpacked BCD • Binary-coded decimal (BCD) numbers use 4 binary bits to represent each decimal digit • A number using unpacked BCD representation stores a decimal digit in the lower four bits of each byte • For example, 5,678 is stored as the following sequence of hexadecimal bytes: 05 06 07 08 Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples 3 ASCII Decimal • A number using ASCII Decimal representation stores a single ASCII digit in each byte • For example, 5,678 is stored as the following sequence of hexadecimal bytes: 35 36 37 38 Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples 4 AAA Instruction • The AAA (ASCII adjust after addition) instruction adjusts the binary result of an ADD or ADC instruction. It makes the result in AL consistent with ASCII digit representation. -

Unit 3 Binary Representation

3.1 3.2 Unit 3 Binary Representation ANALOG VS. DIGITAL 3.3 3.4 Analog vs. Digital Analog vs. Digital • The analog world is based on continuous • Q. Which is better? events. Observations can take on (real) any • A. Depends on what you are trying to do. value. • Some tasks are better handled with analog • The digital world is based on discrete events. data, others with digital data. Observations can only take on a finite number Analog means continuous/real valued signals with of discrete values – an infinite number of possible values – Digital signals are discrete [i.e. 1 of n values] 3.5 3.6 Analog vs. Digital Analog vs. Digital • How much money is in my checking account? • How much do you love me? – Analog: I love you with all my heart!!!! – Analog: Oh, some, but not too much. – Digital: 3.2 x 10 3 MegaHearts – Digital: $243.67 3.7 3.8 The Real (Analog) World Digital is About Numbers • The real world is inherently analog. • In a digital world, numbers are used to represent all the possible discrete events • To interface with it, our digital systems need Numerical values to: – – Computer instructions (ADD, SUB, BLE, …) – Convert analog signals to digital values (numbers) – Characters ('a', 'b', 'c', …) at the input. – Conditions (on, off, ready, paper jam, …) – Convert digital values to analog signals at the • Numbers allow for easy manipulation output. – Add, multiply, compare, store, … • Analog signals can come in many forms • Results are repeatable – Voltage, current, light, color, magnetic fields, – Each time we add the same two number we get pressure, temperature, acceleration, orientation the same result 3.9 3.10 Interpreting Binary Strings • Given a string of 1’s and 0’s, you need to know the representation system being used, before you can understand the value of those 1’s and 0’s. -

Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype

Signals Codes Analog and Digital Signals Compression Data integrity Powerline communications Skype Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype Cristian S. Calude March{May 2008 Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype 1 / 209 Signals Codes Analog and Digital Signals Compression Data integrity Powerline communications Skype Thanks to Nevil Brownlee and Ulrich Speidel for stimulating discussions and critical comments. Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype 2 / 209 Signals Codes Analog and Digital Signals Compression Data integrity Powerline communications Skype Assignment and exam Test (3 questions): 24 April, 1.30 - 2.20 pm. Exam: prepare all results discussed in class Exam: try to solve as many problems as possible from the proposed list Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype 3 / 209 Signals Codes Analog and Digital Signals Compression Data integrity Powerline communications Skype Goals Understand digital and analog signals Understand codes and encoding schemes Understand compression, its applications and limits Understand flow-control and routing Discuss recent issues related to the above topics Data Communications Fundamentals: Signals, Codes, Compression, Integrity, Powerline Communications, and Skype 4 / 209 Signals Codes Analog and Digital Signals Compression Data integrity Powerline communications Skype References 1 S. A. Baset, H. Schulzrinne. An analysis of the Skype Peer- to-Peer Internet Telephony Protocol, 15 Sept. 2004, 12 pp. 2 B. A. Forouzan. Data Communications and Networking, McGraw Hill, 4th edition, New York, 2007. 3 S. Huczynska. Powerline communication and the 36 officers problem, Phil. Trans. R. Soc. A 364 (2006), 3199{3214.