AMD Turion 64 Mobile Technology Product Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Low-Power X86 Solutions for Networked Storage and Media Servers

Low-Power x86 Solutions for Networked Storage and Media Servers OVERVIEW fEAtuRE-RIch cApAbIlItIEs Whether at the office or at home, everyone seems to be using, AMD Processors support Microsoft® and Linux® operating systems creating, and sharing content. Information such as financial that are tailored for these markets to be easy-to-use, protect data records, email, marketing collateral, home video, music and and serve applications. For SMB users, Windows® Small Business pictures must be organized, secure and accessible. And this Server 2011 Essentials is an ideal fit. Automatic backup and information must be protected from hardware failures using recovery protects business information. Organize information, techniques such as RAID and protected from software issues serve business applications such as accounting software and by using snapshots and backup to ensure nothing is lost. connect to online services such as email and CRM. This content requires new embedded solutions to manage, Windows® Home Server organizes, protects and streams digital manipulate and store data. This embedded network storage media content throughout the home. Centralize the iTunes® folder, appliance needs to be affordable, scalable, and easy to use videos, photos and financial spreadsheets. Automatically backup for managing information for business and home users. files to a server to protect from system disk failure or recover from a software or virus attack. AMD plAtfORM sOlutIOns To help meet the wide range of performance, power and price AMD’s pROcEssOR sOlutIOns provide thE fOllowing requirements for SoHo and home users, AMD offers a selection bEnEfIts fOR nEtworkED stORAgE AnD MEDIA sERVERs ™ of processor and chipset solutions. -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

Processor Check Utility for 64-Bit Compatibility

Processor Check Utility for 64-Bit Compatibility VMware Workstation Processor Check Utility for 64-Bit Compatibility VMware Workstation version 5.5 supports virtual machines with 64-bit guest operating systems, running on host machines with the following processors: • AMD™ Athlon™ 64, revision D or later • AMD Opteron™, revision E or later • AMD Turion™ 64, revision E or later • AMD Sempron™, 64-bit-capable revision D or later (experimental support) • Intel™ EM64T VT-capable processors (experimental support) When you power on a virtual machine with a 64-bit guest operating system, Workstation performs an internal check: if the host CPU is not a supported 64-bit processor, you cannot power on the virtual machine. VMware also provides this standalone processor check utility, which you can use without Workstation to perform the same check and determine whether your CPU is supported for virtual machines with 64-bit guest operating systems. Note: On hosts with EM64T VT-capable processors, you may not be able to power on a 64-bit guest, even though the processor check utility indicates that the processor is supported for 64- bit guests. VT functionality can be disabled via the BIOS, but the processor check utility cannot read the appropriate model-specific register (MSR) to detect that the VT functionality has been disabled in the BIOS. Note: In shopping for a processor that is compatible with Workstation 5.5 64-bit guests, you may be unable to determine the revision numbers of a given vendor's offering of AMD Athlon 64, Opteron, Turion 64, or Sempron processors. At this time, the only reliable way to determine whether any of these processors is a revision supported by Workstation 5.5, is by the manufacturing technology (CMOS): any of the AMD Athlon 64, Opteron, Turion 64, or Sempron processors whose manufacturing technology is 90nm SOI (.09 micron SOI) is compatible with Workstation 5.5 64-bit guests. -

HP Compaq 6715S Notebook PC Overview

QuickSpecs HP Compaq 6715s Notebook PC Overview HP recommends Windows Vista® Business 1. WLAN Antennas (with WLAN option) 7. Hard drive activity LED 2. RJ-11/modem Port 8. Battery charging LED 3. Optical drive 9. Power/standby LED 4. Integrated stereo speakers 10. Wireless on/off LED 5. Touchpad with scroll zone 11. Power button with LED 6. Touchpad buttons 12. Wireless on/off Button with LED DA - 12688 Worldwide — Version 12 — February 12, 2008 Page 1 QuickSpecs HP Compaq 6715s Notebook PC Overview 1. Power connector 6. PC Card eject button 2. 2 USB 2.0 ports 7. VGA/external monitor connector 3. Stereo headphone/line out 8. RJ-45/Ethernet Port 4. Stereo microphone in 9. Kensington Lock slot 5. Type I/II PC Card slot At A Glance Genuine Windows Vista Business*, Genuine Windows Vista Home Basic, or FreeDOS Widescreen 15.4-inch diagonal display with wide-viewing angle, BrightView and HP Privacy Filter support Wireless connectivity options: Integrated 802.11a/b/g or 802.11b/g wireless LAN module Bluetooth® AMD Turion™ 64 X2 Dual-Core Mobile Technology, AMD Athlon™ 64 X2 Dual-Core Processors for Notebook PCs, or Mobile AMD Sempron™ processors Thin, lightweight design starting at 5.7 lb/2.59 kg and 1.37 in/34.9 mm thin at front Security features including HP ProtectTools Security Manager and Device Access Manager for HP ProtectTools Integrated optical drive, including optional DVD+/-RW SuperMulti DL LightScribe Drive HP 90W Smart AC Adapter Up to 250-GB 5400 rpm user-removable hard drive with HP DriveGuard protection Up to 4 GB of 667-MHz DDR2 SDRAM, dual channel memory support ATI Radeon X1250 graphics, with up to 831 MB shared system memory (select models) Broadcom NetLink Fast Ethernet Controller Touchpad with scroll zone * At initial boot, either 32- or 64-bit can be selected. -

Take a Way: Exploring the Security Implications of AMD's Cache Way

Take A Way: Exploring the Security Implications of AMD’s Cache Way Predictors Moritz Lipp Vedad Hadžić Michael Schwarz Graz University of Technology Graz University of Technology Graz University of Technology Arthur Perais Clémentine Maurice Daniel Gruss Unaffiliated Univ Rennes, CNRS, IRISA Graz University of Technology ABSTRACT 1 INTRODUCTION To optimize the energy consumption and performance of their With caches, out-of-order execution, speculative execution, or si- CPUs, AMD introduced a way predictor for the L1-data (L1D) cache multaneous multithreading (SMT), modern processors are equipped to predict in which cache way a certain address is located. Conse- with numerous features optimizing the system’s throughput and quently, only this way is accessed, significantly reducing the power power consumption. Despite their performance benefits, these op- consumption of the processor. timizations are often not designed with a central focus on security In this paper, we are the first to exploit the cache way predic- properties. Hence, microarchitectural attacks have exploited these tor. We reverse-engineered AMD’s L1D cache way predictor in optimizations to undermine the system’s security. microarchitectures from 2011 to 2019, resulting in two new attack Cache attacks on cryptographic algorithms were the first mi- techniques. With Collide+Probe, an attacker can monitor a vic- croarchitectural attacks [12, 42, 59]. Osvik et al. [58] showed that tim’s memory accesses without knowledge of physical addresses an attacker can observe the cache state at the granularity of a cache or shared memory when time-sharing a logical core. With Load+ set using Prime+Probe. Yarom et al. [82] proposed Flush+Reload, Reload, we exploit the way predictor to obtain highly-accurate a technique that can observe victim activity at a cache-line granu- memory-access traces of victims on the same physical core. -

Passmark® Software

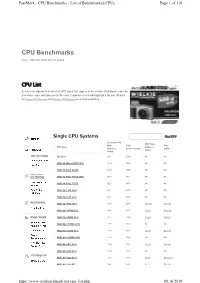

Software BurnInTest PC Reliability and Load Testing Learn More Free Trial Buy PerformanceTest Easy PC Benchmarking Learn More Free Trial Buy OSForensics Extract forensic data from a PC Learn More Free Trial Buy MemTest86 Industry standard for memory testing Learn More Free Trial Buy WirelessMon Monitor WiFi hot spots in real time Learn More Free Trial Buy Zoom Search Engine Add search to your site, DVD, or Intrane tLearn More Free Trial Buy All Software Products Hardware USB3.0 Loopback Plugs Learn More Buy USB2.0 Loopback Plugs Learn More Buy PCIe Test Cards Learn More Buy USB Power Delivery Tester Learn More Buy Serial, Parallel Loopback Plugs Learn More Buy USB Short Circuit Testers Learn More Buy All Hardware Products Benchmarks CPU Benchmarks Learn More Video Card Benchmarks Learn More Hard Drive Benchmarks Learn More RAM Benchmarks Learn More PC Systems Benchmarks Learn More Android Benchmarks Learn More iOS / iPhone Benchmarks Learn More Services Software Customization Independent Benchmarking Labs Hardware & Software Market Trends Benchmark Reports Store Purchase Products Major software\hardware products Learn More Upgrades Purchasing Software Upgrades Learn More Site Licenses Purchasing Site Licenses Learn More Support Purchasing Support \ Support for site licenses Learn More INFO Purchase Orders How to order with a PO Learn More FAQ Information about ordering & shipping Learn More Specials Monthly specials Learn More Support About Us Company Contact Us The Press Room Forums Search entire site... 0 CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android iOS / iPhone 0 CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. -

CPU Benchmarks - List of Benchmarked Cpus Page 1 of 110

PassMark - CPU Benchmarks - List of Benchmarked CPUs Page 1 of 110 CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific Stop seeing this ad processor name will take you to the chart it appears in and will highlight it for you. Results for Single CPU Systems and Multiple CPU Systems are listed separately. Why this ad? Single CPU Systems Find CPU Passmark CPU CPU Value Mark Rank Price CPU Name (higher is (higher is (lower is better) (USD) better) better) 686 Gen 288 2793 NA NA AMD A4 Micro-6400T APU 1544 1983 NA NA AMD A4 PRO-3340B 2402 1590 NA NA AMD A4 PRO-7300B APU 2353 1611 NA NA AMD A4 PRO-7350B 2227 1664 NA NA AMD A4-1200 APU 632 2473 NA NA AMD A4-1250 APU 619 2480 NA NA AMD A4-3300 APU 1503 2008 115.71 $12.99 AMD A4-3300M APU 1188 2172 39.62 $29.99* AMD A4-3305M APU 1227 2150 39.84 $30.81 AMD A4-3310MX APU 1286 2114 NA NA AMD A4-3320M APU 1253 2136 34.93 $35.90 AMD A4-3330MX APU 1218 2154 NA NA AMD A4-3400 APU 1594 1967 18.13 $87.95 AMD A4-3420 APU 1664 1928 NA NA AMD A4-4000 APU 1835 1838 14.31 $128.27* AMD A4-4020 APU 1909 1799 21.21 $90.00 https://www.cpubenchmark.net/cpu_list.php 09. 10. 2019 PassMark - CPU Benchmarks - List of Benchmarked CPUs Page 2 of 110 Passmark CPU CPU Value Mark Rank Price CPU Name (higher is (higher is (lower is better) (USD) better) better) AMD A4-4300M APU 1612 1956 40.44 $39.86 AMD A4-4355M APU 1177 2176 NA NA AMD A4-5000 APU 1916 1794 NA NA AMD A4-5050 APU 2113 1706 NA NA AMD A4-5100 APU 2060 1730 NA -

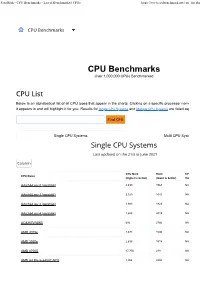

CPU Benchmarks - List of Benchmarked Cpus

PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Benchmarks Over 1,000,000 CPUs Benchmarked Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific processor name will take you to the ch it appears in and will highlight it for you. Results for Single CPU Systems and Multiple CPU Systems are listed separately. Single CPU Systems Multi CPU Systems CPU Mark Rank CPU Value CPU Name (higher is better) (lower is better) (higher is better) AArch64 rev 0 (aarch64) 2,499 1567 NA AArch64 rev 1 (aarch64) 2,320 1642 NA AArch64 rev 2 (aarch64) 1,983 1823 NA AArch64 rev 4 (aarch64) 1,653 2019 NA AC8257V/WAB 693 2766 NA AMD 3015e 2,678 1506 NA AMD 3020e 2,635 1518 NA AMD 4700S 17,756 238 NA AMD A4 Micro-6400T APU 1,004 2480 NA PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Mark Rank CPU Value CPU Name (higher is better) (lower is better) (higher is better) AMD A4 PRO-7300B APU 1,481 2133 NA AMD A4 PRO-7350B 1,024 2465 NA AMD A4-1200 APU 445 3009 NA AMD A4-1250 APU 428 3028 NA AMD A4-3300 APU 961 2528 9.09 AMD A4-3300M APU 686 2778 22.86 AMD A4-3305M APU 815 2649 39.16 AMD A4-3310MX APU 785 2680 NA AMD A4-3320M APU 640 2821 16.42 AMD A4-3330MX APU 681 2781 NA AMD A4-3400 APU 1,031 2458 9.51 AMD A4-3420 APU 1,052 2443 7.74 AMD A4-4000 APU 1,158 2353 38.60 AMD A4-4020 APU 1,214 2310 13.34 AMD A4-4300M APU 997 2486 33.40 AMD A4-4355M APU 816 2648 NA AMD A4-5000 APU 1,282 2257 NA AMD A4-5050 APU 1,328 2219 NA AMD A4-5100 -

AMD in Embedded: Proven Leadership and Solutions

AMD in Embedded: Proven Leadership and Solutions A long history of high-performance low-power solutions for embedded applications For over two decades AMD has been a leader in the embedded market: in the early 1990’s with the introduction of the Am386 and Am486 and their adoption in embedded designs, and followed in 1995 with the introduction of the Am5x86 processor. The AM5x86 processor was one of the fastest and most universally-compatible upgrade paths for users of 486 systems when it was introduced. AMD continued to expand their E86 (Embedded x86) product family in the late 90’s with the release of the Élan™SC520 microcontroller for data communications, telecommunications, and information appliance markets. The ÉlanSC520 microcontroller extended the options available to embedded systems designers by providing fifth-generation x86 performance and was designed to run both 16-bit and 32-bit software. The AMD embedded group grew significantly in early 2000 with the acquisition of Alchemy Semiconductor for its Alchemy line of MIPS processors for the hand-held and portable media player markets. In order to augment its existing line of embedded x86 processor products, AMD also purchased the AMD Geode™ business in August 2003 which was originally part of National Semiconductor. During the second quarter of 2004, AMD launched the new low- power AMD Geode™ NX processors which were based on the AMD-K7™ Thoroughbred architecture with speeds up to 1.4 GHz. These AMD Geode NX processors offered a high performance option in the AMD Geode product line that was still sufficiently low power to be designed into fan-less applications. -

![CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU](https://docslib.b-cdn.net/cover/8530/cpu-history-tualatin-banias-dothan-yonah-jonah-conroe-allendale-yorkfield-xe-intel-created-pentium-from-quad-core-cpu-3058530.webp)

CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel Created Pentium (From Quad-Core CPU

2nd Generation 4th Generation 5th Generation 6th Generation 7th Generation 3rd Generation Intel Pentium III-S Intel Pentium-M (Centrino) Intel Pentium-M (Centrino) Intel Core Duo (Viiv) Intel Core 2 Duo (Viiv)/Xeon Intel Core 2 Duo (Viiv) Intel Core 2 Extreme (Viiv) Intel had the first consumer CPU History [Tualatin] [Banias] [Dothan] [Yonah (Jonah)] [Conroe] [Allendale] [Yorkfield XE] Intel created Pentium (from quad-core CPU. x86/CISC Microprocessors Greek penta which means (2001) (2003) (2004) (2006) (2006) (2007) (2007) 1st Generation Intel Pentium II Xeon Intel Pentium III Xeon Centrino is not a CPU; it is Begin Core five) to distinguish the Intel [P6] [Tanner] a mobile Intel CPU paired nomeclature brand from clones. Names (1998) (1999) Intel Celeron with an Intel Wi-Fi adapter. Intel Celeron Intel Core Solo can be copyrighted, product [Tualeron] [Dothan-1024] Intel Xeon LV Intel Celeron Intel Celeron [Yonah] ID's cannot. (2001) (2004) [Sossaman] [Banias-512] [Shelton (Banias-0)] (2006) (2006) Intel Core 2 Duo Intel Core 2 Extreme Intel Celeron Intel 80386 DX Intel 80486 DX Intel Pentium Intel Pentium Pro Intel Pentium II Intel Pentium II Intel Pentium III Intel Pentium III Intel Pentium 4 Intel Pentium 4 (2004) (2004) Intel Pentium 4 Intel Pentium 4 Intel 4004 Intel 8008 Intel 8086 Intel 80286 [Conroe XE] [Conroe-L] [P3] [P4] [P5/P54/P54C] [P6] [Klamath] [Deuschutes] [Katmai] [Coppermine] [Williamette] [Northwood] [Prescott] [Cedar Mill] END-OF-LINE (Centrino Duo) (1971) (1972) (1978) (1982) (2006) (2007) (1985) (1989) (1993) (1995) (1997) (1998) (1999) (1999) (2000) (2002) (2004) (2006) [Merom] (2006) Yonah is Hebrew for Jonah. -

Socket E Slot Per

Socket e Slot per CPU Socket e Slot per CPU Socket 1 Socket 2 Socket 3 Socket 4 Socket 5 Socket 6 Socket 7 e Super Socket 7 Socket 8 Slot 1 (SC242) Slot 2 (SC330) Socket 370 (PGA-370) Slot A Socket A (Socket 462) Socket 423 Socket 478 Socket 479 Socket 775 (LGA775) Socket 603 Socket 604 PAC418 PAC611 Socket 754 Socket 939 Socket 940 Socket AM2 (Socket M2) Socket 771 (LGA771) Socket F (Socket 1207) Socket S1 A partire dai processori 486, Intel progettò e introdusse i socket per CPU che, oltre a poter ospitare diversi modelli di processori, ne consentiva anche una rapida e facile sostituzione/aggiornamento. Il nuovo socket viene definito ZIF (Zero Insertion Force ) in quanto l'inserimento della CPU non richiede alcuna forza contrariamente ai socket LIF ( Low Insertion Force ) i quali, oltre a richiedere una piccola pressione per l'inserimento del chip, richiedono anche appositi tool per la sua rimozione. Il modello di socket ZIF installato sulla motherboard è, in genere, indicato sul socket stesso. Tipi diversi di socket accettano famiglie diverse di processori. Se si conosce il tipo di zoccolo montato sulla scheda madre è possibile sapere, grosso modo, che tipo di processori può ospitare. Il condizionale è d'obbligo in quanto per sapere con precisione che tipi di processore può montare una scheda madre non basta sapere solo il socket ma bisogna tenere conto anche di altri fattori come le tensioni, il FSB, le CPU supportate dal BIOS ecc. Nel caso ci si stia apprestando ad aggiornare la CPU è meglio, dunque, attenersi alle informazioni sulla compatibilità fornite dal produttore della scheda madre. -

Stakes Claim to Processor Performance

Stakes Claim To Processor AMDPerformance Chipmaker makes gains in the desktop and notebook markets Advanced Micro Devices is living up to its name — and corporate IT leaders are taking notice. MD’s family of AMD64 processors for the server, Aworkstation and PC markets has consistently surpassed Intel on performance since its introduction in 2003, analysts say, which has resulted in record-high sales for the company, increasing market share and a growing popularity among buyers. While Intel still dominates with nearly 81 percent of the overall market, AMD is chipping away at Intel’s lead. AMD outsold Intel in U.S. retail stores last October, capturing 49.8 percent of PCs sold compared with Intel’s 48.5 percent, according to analyst firm Current Analysis, in Washington, D.C. In the corporate market, AMD has grabbed 12.7 percent of the server market since entering the space with its Opteron processor three years ago, according to Mercury Research, in Cave Creek, Ariz. Now the company is trying to leverage its growth in consumer PCs and server sales to increase sales of its desktop and notebook PCs in 70 • AMD Processors the corporate market. AMD executives say 85 of the top 100 “We’ve taken the memory out of the front side bus and companies in the Forbes Global 2000 used AMD processors in connected it to the processor and eliminated a 20-year-old its hardware in the third quarter of 2005. In the previous year, bottleneck,” he says. that figure was only 25. AMD’s processors also feature power management capabilities, “For AMD, from a mobile, desktop, server and workstation which use less electricity, create less heat and allow cooling fans perspective, our processors are more and more desired by to spin less.