Analysis and Design of Common-Diode Tapped-Inductor Pwm Buck Converter in Ccm

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Buck-Boost Transformerless DC–DC Converter Based on IGBT Modules for Fast Charge of Electric Vehicles

electronics Article A Buck-Boost Transformerless DC–DC Converter Based on IGBT Modules for Fast Charge of Electric Vehicles Borislav Dimitrov 1,* , Khaled Hayatleh 1, Steve Barker 1, Gordana Collier 1, Suleiman Sharkh 2 and Andrew Cruden 2 1 School of Engineering, Computing and Mathematics, Oxford Brookes University, Wheatley campus, Oxford OX33 1HX, UK; [email protected] (K.H.); [email protected] (S.B.); [email protected] (G.C.) 2 Faculty of Engineering and the Environment, University of Southampton, University Road, Southampton SO17 1BJ, UK; [email protected] (S.S.); [email protected] (A.C.) * Correspondence: [email protected]; Tel.: +44-(0)1865-482962 Received: 9 January 2020; Accepted: 25 February 2020; Published: 28 February 2020 Abstract: A transformer-less Buck-Boost direct current–direct current (DC–DC) converter in use for the fast charge of electric vehicles, based on powerful high-voltage isolated gate bipolar transistor (IGBT) modules is analyzed, designed and experimentally verified. The main advantages of this topology are: simple structure on the converter’s power stage; a wide range of the output voltage, capable of supporting contemporary vehicles’ on-board battery packs; efficiency; and power density accepted to be high enough for such a class of hard-switched converters. A precise estimation of the loss, dissipated in the converter’s basic modes of operation Buck, Boost, and Buck-Boost is presented. The analysis shows an approach of loss minimization, based on switching frequency reduction during the Buck-Boost operation mode. Such a technique guarantees stable thermal characteristics during the entire operation, i.e., battery charge cycle. -

VIDE. TEHNOLOĢIJA. RESURSI IX Starptautiskās Zinātniski Praktiskās Konferences Materiāli 2013.Gada 20.-22.Jūnijs

RĒZEKNES AUGSTSKOLA INŽENIERU FAKULTĀTE RĒZEKNES AUGSTSKOLAS REĢIONĀLISTIKAS ZINĀTNISKAIS INSTITŪTS REZEKNE HIGHER EDUCATION INSTITUTION FACULTY OF ENGINEERING SCIENTIFIC INSTITUTE FOR REGIONAL STUDIES VIDE. TEHNOLOĢIJA. RESURSI IX starptautiskās zinātniski praktiskās konferences materiāli 2013.gada 20.-22.jūnijs 2. SĒJUMS ENVIRONMENT. TECHNOLOGY. RESOURCES Proceedings of the 9th International Scientific and Practical Conference June 20-22, 2013 VOLUME II Rēzekne 2013 VIDE. TEHNOLOĢIJA. RESURSI: 9. starptautiskās zinātniski praktiskās konferences materiāli 2013. gada 20.-22. jūnijs. 2. sējums. Rēzekne, 2013. 148 lpp. ENVIRONMENT. TECHNOLOGY. RESOURCES: Proceedings of the 9th International Scientific and Practical Conference June 20-22, 2013. Volume II. Rezekne, 2013. p. 148. Zinātnisko rakstu krājumā iekļauti IX starptautiskās zinātniski praktiskās konferences “Vide. Tehnoloģija. Resursi” raksti. Rakstu tematika saistīta ar vides kvalitāti un monitoringu, piesārņojuma novēršanas tehnoloģijām, tīrāku ražošanu, ilgtspējīgo lauksaimniecību, vides izglītību un ekonomiku. Rakstu krājumā pārstāvēti referāti, kas ir saistīti ar datorzinātnes, matemātikas, mehānikas, elektrotehnikas, elektronikas un mehatronikas pielietošanu vides zinātnē, metālapstrādē un citu nozaru problēmu risināšanā. Proceedings include papers presented at the 9th International Conference “Environment. Technology. Resources.” The themes of the papers are – the environmental quality and monitoring, pollution prevention technologies, cleaner production, sustainable agriculture, -

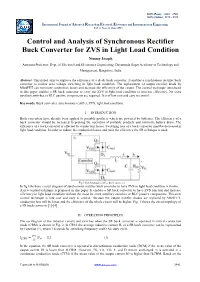

Control and Analysis of Synchronous Rectifier Buck Converter for ZVS in Light Load Condition Nimmy Joseph Assistant Professor, Dept

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875 International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 2, Issue 6, June 2013 Control and Analysis of Synchronous Rectifier Buck Converter for ZVS in Light Load Condition Nimmy Joseph Assistant Professor, Dept. of Electrical and Electronics Engineering, Dayananda Sagar Academy of Technology and Management, Bangalore, India Abstract- This paper aims to improve the efficiency of a dc-dc buck converter. It enables a synchronous rectifier buck converter to realize zero voltage switching in light load condition. The replacement of output rectifier diode by MOSFET can minimize conduction losses and increase the efficiency of the circuit. The control technique introduced in this paper enables a SR buck converter to carry out ZVS in light load condition to increase efficiency. No extra auxiliary switches or RLC passive components are required. It is of low cost and easy to control. Keywords: Buck converter, synchronous rectifier, ZVS, light load condition. I. INTRODUCTION Buck converters have already been applied to portable products which are powered by batteries. The efficiency of a buck converter should be increased to prolong the operation of portable products and minimize battery drain. The efficiency of a buck converter is affected by conduction losses. Switching loss of a buck converter must be decreased in light load condition. In order to reduce the conduction losses and raise the efficiency the SR technique is used. Fig.1 Synchronous rectifier buck converter In fig.1the basic circuit diagram of synchronous rectifier buck converter to have ZVS in light load condition is shown. -

Selecting the Optimal Inductor for Power Converter Applications

Selecting the Optimal Inductor for Power Converter Applications BACKGROUND SDR Series Power Inductors Today’s electronic devices have become increasingly power hungry and are operating at SMD Non-shielded higher switching frequencies, starving for speed and shrinking in size as never before. Inductors are a fundamental element in the voltage regulator topology, and virtually every circuit that regulates power in automobiles, industrial and consumer electronics, SRN Series Power Inductors and DC-DC converters requires an inductor. Conventional inductor technology has SMD Semi-shielded been falling behind in meeting the high performance demand of these advanced electronic devices. As a result, Bourns has developed several inductor models with rated DC current up to 60 A to meet the challenges of the market. SRP Series Power Inductors SMD High Current, Shielded Especially given the myriad of choices for inductors currently available, properly selecting an inductor for a power converter is not always a simple task for designers of next-generation applications. Beginning with the basic physics behind inductor SRR Series Power Inductors operations, a designer must determine the ideal inductor based on radiation, current SMD Shielded rating, core material, core loss, temperature, and saturation current. This white paper will outline these considerations and provide examples that illustrate the role SRU Series Power Inductors each of these factors plays in choosing the best inductor for a circuit. The paper also SMD Shielded will describe the options available for various applications with special emphasis on new cutting edge inductor product trends from Bourns that offer advantages in performance, size, and ease of design modification. -

Capacitors and Inductors

DC Principles Study Unit Capacitors and Inductors By Robert Cecci In this text, you’ll learn about how capacitors and inductors operate in DC circuits. As an industrial electrician or elec- tronics technician, you’ll be likely to encounter capacitors and inductors in your everyday work. Capacitors and induc- tors are used in many types of industrial power supplies, Preview Preview motor drive systems, and on most industrial electronics printed circuit boards. When you complete this study unit, you’ll be able to • Explain how a capacitor holds a charge • Describe common types of capacitors • Identify capacitor ratings • Calculate the total capacitance of a circuit containing capacitors connected in series or in parallel • Calculate the time constant of a resistance-capacitance (RC) circuit • Explain how inductors are constructed and describe their rating system • Describe how an inductor can regulate the flow of cur- rent in a DC circuit • Calculate the total inductance of a circuit containing inductors connected in series or parallel • Calculate the time constant of a resistance-inductance (RL) circuit Electronics Workbench is a registered trademark, property of Interactive Image Technologies Ltd. and used with permission. You’ll see the symbol shown above at several locations throughout this study unit. This symbol is the logo of Electronics Workbench, a computer-simulated electronics laboratory. The appearance of this symbol in the text mar- gin signals that there’s an Electronics Workbench lab experiment associated with that section of the text. If your program includes Elec tronics Workbench as a part of your iii learning experience, you’ll receive an experiment lab book that describes your Electronics Workbench assignments. -

Researching the Efficiency of Buck Converter Synchronous Rectifier

INDUSTRIAL AND TECHNOLOGY SYSTEMS: ISSN 2664-9969 REPORTS ON RESEARCH PROJECTS UDC 621.314 DOI: 10.15587/2706-5448.2020.207893 Zheliazkov Y. RESEARCHING THE EFFICIENCY OF BUCK CONVERTER SYNCHRONOUS RECTIFIER The object of study is synchronous buck-voltage converter with digital control system. One of the most prob- lematic things is energy changing and transmission in converters to reach certain numerical range with minimal losses in the components of the electrical circuit. An enormous calculated parameters of electrical scheme. There was advised and described both structure and electrical scheme of synchronous converter, which, thanks to digi- tal system, provides dates with more accuracy connected with an impact on working scheme. There was shown detailed analysis example with a numerical value for the certain elements of electrical scheme. It’s a fundament in order to choose certain parts of electrical scheme according to the certain categories. During research there was used selection of hardware and software tools: elements for buck-converter – key, diode and capacitor; certain voltage and frequency range for microcontroller; control of the power keys of the circuit with the corresponding operating parameters for driver. There was analyzed and calculated all over the possible losses during the process bucking of the voltage to the certain level, an enormous losses in the components of the converter electrical scheme – induction coil, keys and capacitors. It’s an important part of synchronous buck-converter. There was calculated power losses and efficiency through the received graphics of keys com- mutation in electrical scheme. There were received graphic dependence of converter efficiency on output power; time characteristics of the control signal pulse-width modulation (PWM) and output voltage; dependence on the commutation losses. -

Class D Audio Amplifier Application Note with Ferroxcube Gapped Toroid Output Filter

Class D audio amplifier Application Note with Ferroxcube gapped toroid output filter Class D audio amplifier with Ferroxcube gapped toroid output filter The concept of a Class D amplifier has input signal shape but with larger bridge configuration. Each topology been around for a long time, however amplitude. And audio amplifier is spe- has pros and cons. In brief, a half bridge only fairly recently have they become cially design for reproducing audio fre- is potentially simpler,while a full bridge commonly used in consumer applica- quencies. is better in audio performance.The full tions. Due to improvements in the bridge topology requires two half- speed, power capacity and efficiency of Amplifier circuits are classified as A, B, bridge amplifiers, and thus more com- modern semiconductor devices, appli- AB and C for analog designs, and class ponents. cations using Class D amplifiers have D and E for switching devices. For the become affordable for the common analog classes, each type defines which A Class D amplifier works in the same person.The mainly benefit of this kind proportion of the input signal cycle is way as a PWM power supply, except of amplifier is the efficiency, the theo- used to switch on the amplifying device: that the reference signal is the audio retical maximum efficiency of a class D Class A 100% wave instead of the accurate voltage design is 100%, and over 90% is Class AB Between 50% and 100% reference. achieve in practice. Class B 50% Class C less than 50% Let’s start with an assumption that the Other benefits of these amplifiers are input signal is a standard audio line level the reduction in consumption, their The letter D used to designate the class signal.This audio line level signal is sinu- smaller size and the lower weight. -

Effect of Source Inductance on MOSFET Rise and Fall Times

Effect of Source Inductance on MOSFET Rise and Fall Times Alan Elbanhawy Power industry consultant, email: [email protected] Abstract The need for advanced MOSFETs for DC-DC converters applications is growing as is the push for applications miniaturization going hand in hand with increased power consumption. These advanced new designs should theoretically translate into doubling the average switching frequency of the commercially available MOSFETs while maintaining the same high or even higher efficiency. MOSFETs packaged in SO8, DPAK, D2PAK and IPAK have source inductance between 1.5 nH to 7 nH (nanoHenry) depending on the specific package, in addition to between 5 and 10 nH of printed circuit board (PCB) trace inductance. In a synchronous buck converter, laboratory tests and simulation show that during the turn on and off of the high side MOSFET the source inductance will develop a negative voltage across it, forcing the MOSFET to continue to conduct even after the gate has been fully switched off. In this paper we will show that this has the following effects: • The drain current rise and fall times are proportional to the total source inductance (package lead + PCB trace) • The rise and fall times arealso proportional to the magnitude of the drain current, making the switching losses nonlinearly proportional to the drain current and not linearly proportional as has been the common wisdom • It follows from the above two points that the current switch on/off is predominantly controlled by the traditional package's parasitic -

How to Select a Proper Inductor for Low Power Boost Converter

Application Report SLVA797–June 2016 How to Select a Proper Inductor for Low Power Boost Converter Jasper Li ............................................................................................. Boost Converter Solution / ALPS 1 Introduction Traditionally, the inductor value of a boost converter is selected through the inductor current ripple. The average input current IL(DC_MAX) of the inductor is calculated using Equation 1. Then the inductance can be [1-2] calculated using Equation 2. It is suggested that the ∆IL(P-P) should be 20%~40% of IL(DC_MAX) . V x I = OUT OUT(MAX) IL(DC_MAX) VIN(TYP) x η (1) Where: • VOUT: output voltage of the boost converter. • IOUT(MAX): the maximum output current. • VIN(TYP): typical input voltage. • ƞ: the efficiency of the boost converter. V x() V+ V - V L = IN OUT D IN ΔIL(PP)- xf SW x() V OUT+ V D (2) Where: • ƒSW: the switching frequency of the boost converter. • VD: Forward voltage of the rectify diode or the synchronous MOSFET in on-state. However, the suggestion of the 20%~40% current ripple ratio does not take in account the package size of inductor. At the small output current condition, following the suggestion may result in large inductor that is not applicable in a real circuit. Actually, the suggestion is only the start-point or reference for an inductor selection. It is not the only factor, or even not an important factor to determine the inductance in the low power application of a boost converter. Taking TPS61046 as an example, this application note proposes a process to select an inductor in the low power application. -

TSEK03: Radio Frequency Integrated Circuits (RFIC) Lecture 7: Passive

TSEK03: Radio Frequency Integrated Circuits (RFIC) Lecture 7: Passive Devices Ted Johansson, EKS, ISY [email protected] "2 Overview • Razavi: Chapter 7 7.1 General considerations 7.2 Inductors 7.3 Transformers 7.4 Transmission lines 7.5 Varactors 7.6 Constant capacitors TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "3 7.1 General considerations • Reduction of off-chip components => Reduction of system cost. Integration is good! • On-chip inductors: • With inductive loads (b), we can obtain higher operating frequency and better operation at low supply voltages. TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "4 Bond wires = good inductors • High quality • Hard to model • The bond wires and package pins connecting chip to outside world may experience significant coupling, creating crosstalk between parts of a transceiver. TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "5 7.2 Inductors • Typically realized as metal spirals. • Larger inductance than a straight wire. • Spiral is implemented on top metal layer to minimize parasitic resistance and capacitance. TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "6 • A two dimensional square spiral inductor is fully specified by the following four quantities: • Outer dimension, Dout • Line width, W • Line spacing, S • Number of turns, N • The inductance primarily depends on the number of turns and the diameter of each turn TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "7 Magnetic Coupling Factor TSEK03 Integrated Radio Frequency Circuits 2019/Ted Johansson "8 Inductor Structures in RFICs • Various inductor geometries shown below are result of improving the trade-offs in inductor design, specifically those between (a) quality factor and the capacitance, (b) inductance and the dimensions. -

AN826 Crystal Oscillator Basics and Crystal Selection for Rfpic™ And

AN826 Crystal Oscillator Basics and Crystal Selection for rfPICTM and PICmicro® Devices • What temperature stability is needed? Author: Steven Bible Microchip Technology Inc. • What temperature range will be required? • Which enclosure (holder) do you desire? INTRODUCTION • What load capacitance (CL) do you require? • What shunt capacitance (C ) do you require? Oscillators are an important component of radio fre- 0 quency (RF) and digital devices. Today, product design • Is pullability required? engineers often do not find themselves designing oscil- • What motional capacitance (C1) do you require? lators because the oscillator circuitry is provided on the • What Equivalent Series Resistance (ESR) is device. However, the circuitry is not complete. Selec- required? tion of the crystal and external capacitors have been • What drive level is required? left to the product design engineer. If the incorrect crys- To the uninitiated, these are overwhelming questions. tal and external capacitors are selected, it can lead to a What effect do these specifications have on the opera- product that does not operate properly, fails prema- tion of the oscillator? What do they mean? It becomes turely, or will not operate over the intended temperature apparent to the product design engineer that the only range. For product success it is important that the way to answer these questions is to understand how an designer understand how an oscillator operates in oscillator works. order to select the correct crystal. This Application Note will not make you into an oscilla- Selection of a crystal appears deceivingly simple. Take tor designer. It will only explain the operation of an for example the case of a microcontroller. -

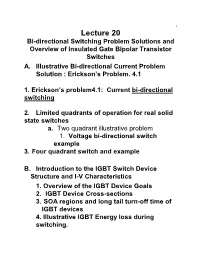

Lecture 20 Bi-Directional Switching Problem Solutions and Overview of Insulated Gate Bipolar Transistor Switches A

1 Lecture 20 Bi-directional Switching Problem Solutions and Overview of Insulated Gate Bipolar Transistor Switches A. Illustrative Bi-directional Current Problem Solution : Erickson’s Problem. 4.1 1. Erickson’s problem4.1: Current bi-directional switching 2. Limited quadrants of operation for real solid state switches a. Two quadrant illustrative problem 1. Voltage bi-directional switch example 3. Four quadrant switch and example B. Introduction to the IGBT Switch Device Structure and I-V Characteristics 1. Overview of the IGBT Device Goals 2. IGBT Device Cross-sections 3. SOA regions and long tail turn-off time of IGBT devices 4. Illustrative IGBT Energy loss during switching. 2 A. Illustrative Problem Solution : Problem. 4.1 (1) Erickson’s problem 4.1: Current bi-directional switching For Chapter 2 of Erickson in problems #4 & #5 you solved for VOFF and ION of switches leading to the transistor circuit. Follow the same procedure as your old homework. C 1 L 2 Vg + v - i 2 L 1 R L I1 I1 I2 + - - vL I IC - C - V L v C R v Vg C R v g L + + + SW1 on/SW2 off SW1 off/SW2 on Time DT Time D’T s 2 1 s VL = Vg - V VL = - Vg V V V I = I - g I = - c 1 R c R 1 2 Volt-sec balance on L: <VL> = 0, D’ = 1 - D D(Vg - V) - D¢ V = 0 ® DVg - Dg + DVg = 0 3 DV = 2 Dvg - Vg Vg(2D- 1) V = output voltage in steady state D Charge balance on the capacitor: <ic> = 0 V V V V V D (I - ) - D¢ = 0 ® DI - D - + D = 0 1 R R 1 R R R V Vg(2D- 1) D > ½ Þ Gives bipolar current I1 = = D < ½ Þ when on DR D2R a b + - + IL + - IC + VL L V d C R V g c - + - + - - SW a ® Va = Vg - V SW b ® Vb = V - Vg Ia = IL Ib = IL SW c ® VC = - Vg SW d ® Vd = Vg Ic = IL Id = IL (a) (b) (c) (d) I I L IL L IL Vg-V V V-V -V g g g -I -IL -IL L -IL KEY: Show why Vtr(OFF) is unipolar IL = IR is bipolar 4 A bipolar implementation of the bi-directional current switch is shown below: a b + C R V V - g c d - For HW#4 you do Erickson Problem 4.5 another two quadrant example with bipolar current.