Evaluating Performance Portability of Openmp for SNAP on NVIDIA, Intel, and AMD Gpus Using the Roofline Methodology

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

Future-ALCF-Systems-Parker.Pdf

Future ALCF Systems Argonne Leadership Computing Facility 2021 Computational Performance Workshop, May 4-6 Scott Parker www.anl.gov Aurora Aurora: A High-level View q Intel-HPE machine arriving at Argonne in 2022 q Sustained Performance ≥ 1Exaflops DP q Compute Nodes q 2 Intel Xeons (Sapphire Rapids) q 6 Intel Xe GPUs (Ponte Vecchio [PVC]) q Node Performance > 130 TFlops q System q HPE Cray XE Platform q Greater than 10 PB of total memory q HPE Slingshot network q Fliesystem q Distributed Asynchronous Object Store (DAOS) q ≥ 230 PB of storage capacity; ≥ 25 TB/s q Lustre q 150PB of storage capacity; ~1 TB/s 3 The Evolution of Intel GPUs 4 The Evolution of Intel GPUs 5 XE Execution Unit qThe EU executes instructions q Register file q Multiple issue ports q Vector pipelines q Float Point q Integer q Extended Math q FP 64 (optional) q Matrix Extension (XMX) (optional) q Thread control q Branch q Send (memory) 6 XE Subslice qA sub-slice contains: q 16 EUs q Thread dispatch q Instruction cache q L1, texture cache, and shared local memory q Load/Store q Fixed Function (optional) q 3D Sampler q Media Sampler q Ray Tracing 7 XE 3D/Compute Slice qA slice contains q Variable number of subslices q 3D Fixed Function (optional) q Geometry q Raster 8 High Level Xe Architecture qXe GPU is composed of q 3D/Compute Slice q Media Slice q Memory Fabric / Cache 9 Aurora Compute Node • 6 Xe Architecture based GPUs PVC PVC (Ponte Vecchio) • All to all connection PVC PVC • Low latency and high bandwidth PVC PVC • 2 Intel Xeon (Sapphire Rapids) processors Slingshot -

Hardware Developments V E-CAM Deliverable 7.9 Deliverable Type: Report Delivered in July, 2020

Hardware developments V E-CAM Deliverable 7.9 Deliverable Type: Report Delivered in July, 2020 E-CAM The European Centre of Excellence for Software, Training and Consultancy in Simulation and Modelling Funded by the European Union under grant agreement 676531 E-CAM Deliverable 7.9 Page ii Project and Deliverable Information Project Title E-CAM: An e-infrastructure for software, training and discussion in simulation and modelling Project Ref. Grant Agreement 676531 Project Website https://www.e-cam2020.eu EC Project Officer Juan Pelegrín Deliverable ID D7.9 Deliverable Nature Report Dissemination Level Public Contractual Date of Delivery Project Month 54(31st March, 2020) Actual Date of Delivery 6th July, 2020 Description of Deliverable Update on "Hardware Developments IV" (Deliverable 7.7) which covers: - Report on hardware developments that will affect the scientific areas of inter- est to E-CAM and detailed feedback to the project software developers (STFC); - discussion of project software needs with hardware and software vendors, completion of survey of what is already available for particular hardware plat- forms (FR-IDF); and, - detailed output from direct face-to-face session between the project end- users, developers and hardware vendors (ICHEC). Document Control Information Title: Hardware developments V ID: D7.9 Version: As of July, 2020 Document Status: Accepted by WP leader Available at: https://www.e-cam2020.eu/deliverables Document history: Internal Project Management Link Review Review Status: Reviewed Written by: Alan Ó Cais(JSC) Contributors: Christopher Werner (ICHEC), Simon Wong (ICHEC), Padraig Ó Conbhuí Authorship (ICHEC), Alan Ó Cais (JSC), Jony Castagna (STFC), Godehard Sutmann (JSC) Reviewed by: Luke Drury (NUID UCD) and Jony Castagna (STFC) Approved by: Godehard Sutmann (JSC) Document Keywords Keywords: E-CAM, HPC, Hardware, CECAM, Materials 6th July, 2020 Disclaimer:This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement. -

Marc and Mentat Release Guide

Marc and Mentat Release Guide Marc® and Mentat® 2020 Release Guide Corporate Europe, Middle East, Africa MSC Software Corporation MSC Software GmbH 4675 MacArthur Court, Suite 900 Am Moosfeld 13 Newport Beach, CA 92660 81829 Munich, Germany Telephone: (714) 540-8900 Telephone: (49) 89 431 98 70 Toll Free Number: 1 855 672 7638 Email: [email protected] Email: [email protected] Japan Asia-Pacific MSC Software Japan Ltd. MSC Software (S) Pte. Ltd. Shinjuku First West 8F 100 Beach Road 23-7 Nishi Shinjuku #16-05 Shaw Tower 1-Chome, Shinjuku-Ku Singapore 189702 Tokyo 160-0023, JAPAN Telephone: 65-6272-0082 Telephone: (81) (3)-6911-1200 Email: [email protected] Email: [email protected] Worldwide Web www.mscsoftware.com Support http://www.mscsoftware.com/Contents/Services/Technical-Support/Contact-Technical-Support.aspx Disclaimer User Documentation: Copyright 2020 MSC Software Corporation. All Rights Reserved. This document, and the software described in it, are furnished under license and may be used or copied only in accordance with the terms of such license. Any reproduction or distribution of this document, in whole or in part, without the prior written authorization of MSC Software Corporation is strictly prohibited. MSC Software Corporation reserves the right to make changes in specifications and other information contained in this document without prior notice. The concepts, methods, and examples presented in this document are for illustrative and educational purposes only and are not intended to be exhaustive or to apply to any particular engineering problem or design. THIS DOCUMENT IS PROVIDED ON AN “AS-IS” BASIS AND ALL EXPRESS AND IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID. -

Intro to Parallel Computing

Intro To Parallel Computing John Urbanic Parallel Computing Scientist Pittsburgh Supercomputing Center Copyright 2021 Purpose of this talk ⚫ This is the 50,000 ft. view of the parallel computing landscape. We want to orient you a bit before parachuting you down into the trenches. ⚫ This talk bookends our technical content along with the Outro to Parallel Computing talk. The Intro has a strong emphasis on hardware, as this dictates the reasons that the software has the form and function that it has. Hopefully our programming constraints will seem less arbitrary. ⚫ The Outro talk can discuss alternative software approaches in a meaningful way because you will then have one base of knowledge against which we can compare and contrast. ⚫ The plan is that you walk away with a knowledge of not just MPI, etc. but where it fits into the world of High Performance Computing. FLOPS we need: Climate change analysis Simulations Extreme data • Cloud resolution, quantifying uncertainty, • “Reanalysis” projects need 100 more computing understanding tipping points, etc., will to analyze observations drive climate to exascale platforms • Machine learning and other analytics • New math, models, and systems support are needed today for petabyte data sets will be needed • Combined simulation/observation will empower policy makers and scientists Courtesy Horst Simon, LBNL Exascale combustion simulations ⚫ Goal: 50% improvement in engine efficiency ⚫ Center for Exascale Simulation of Combustion in Turbulence (ExaCT) – Combines simulation and experimentation – -

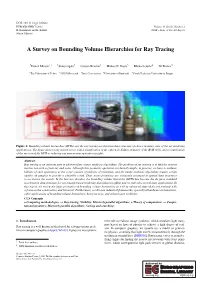

A Survey on Bounding Volume Hierarchies for Ray Tracing

DOI: 10.1111/cgf.142662 EUROGRAPHICS 2021 Volume 40 (2021), Number 2 H. Rushmeier and K. Bühler STAR – State of The Art Report (Guest Editors) A Survey on Bounding Volume Hierarchies for Ray Tracing yDaniel Meister1z yShinji Ogaki2 Carsten Benthin3 Michael J. Doyle3 Michael Guthe4 Jiríˇ Bittner5 1The University of Tokyo 2ZOZO Research 3Intel Corporation 4University of Bayreuth 5Czech Technical University in Prague Figure 1: Bounding volume hierarchies (BVHs) are the ray tracing acceleration data structure of choice in many state of the art rendering applications. The figure shows a ray-traced scene, with a visualization of the otherwise hidden structure of the BVH (left), and a visualization of the success of the BVH in reducing ray intersection operations (right). Abstract Ray tracing is an inherent part of photorealistic image synthesis algorithms. The problem of ray tracing is to find the nearest intersection with a given ray and scene. Although this geometric operation is relatively simple, in practice, we have to evaluate billions of such operations as the scene consists of millions of primitives, and the image synthesis algorithms require a high number of samples to provide a plausible result. Thus, scene primitives are commonly arranged in spatial data structures to accelerate the search. In the last two decades, the bounding volume hierarchy (BVH) has become the de facto standard acceleration data structure for ray tracing-based rendering algorithms in offline and recently also in real-time applications. In this report, we review the basic principles of bounding volume hierarchies as well as advanced state of the art methods with a focus on the construction and traversal. -

Intro to Parallel Computing

Intro To Parallel Computing John Urbanic Parallel Computing Scientist Pittsburgh Supercomputing Center Copyright 2021 Purpose of this talk ⚫ This is the 50,000 ft. view of the parallel computing landscape. We want to orient you a bit before parachuting you down into the trenches to deal with MPI. ⚫ This talk bookends our technical content along with the Outro to Parallel Computing talk. The Intro has a strong emphasis on hardware, as this dictates the reasons that the software has the form and function that it has. Hopefully our programming constraints will seem less arbitrary. ⚫ The Outro talk can discuss alternative software approaches in a meaningful way because you will then have one base of knowledge against which we can compare and contrast. ⚫ The plan is that you walk away with a knowledge of not just MPI, etc. but where it fits into the world of High Performance Computing. FLOPS we need: Climate change analysis Simulations Extreme data • Cloud resolution, quantifying uncertainty, • “Reanalysis” projects need 100 more computing understanding tipping points, etc., will to analyze observations drive climate to exascale platforms • Machine learning and other analytics • New math, models, and systems support are needed today for petabyte data sets will be needed • Combined simulation/observation will empower policy makers and scientists Courtesy Horst Simon, LBNL Exascale combustion simulations ⚫ Goal: 50% improvement in engine efficiency ⚫ Center for Exascale Simulation of Combustion in Turbulence (ExaCT) – Combines simulation and -

Software Development for Performance in the Energy Exascale Earth System Model

Software development for performance in the Energy Exascale Earth System Model Robert Jacob Argonne National Laboratory Lemont, IL, USA (Conveying work from many people in the E3SM project.) E3SM: Energy Exascale Earth System Model • 8 U.S. DOE labs + universities. Total ~50 FTEs spread over 80 staff • Atmosphere, Land, Ocean and Ice (land and sea) component models • Development and applications driven by DOE-SC mission interests: Energy/water issues looking out 40 years • Computational goal: Ensure an Earth system model will run well on upcoming DOE pre-exascale and exascale computers • https://github.com/E3SM-Project/E3SM – Open source and open development • http://e3sm.org E3SM v1 (released April, 2018) • New MPAS Ocean/Sea Ice/Land Ice components • Atmosphere – Spectral Element (HOMME) dynamical core – Increased vertical resolution: 72L, 40 tracers. – MAM4 aerosols, MG2 microphysics, RRTMG radiation, CLUBBv1 boundary layer, Zhang-McFarlane deep convection. • Land – New river routing (MOSART), soil hydrology (VSFM), dynamic rooting distribution, dynamic C:N:P stoichiometry option • 2 Resolutions: – Standard: Ocean/sea-ice is 30 to 60km quasi-uniform. 60L, 100km atm/land – High: Ocean/sea-ice is 6 to 18 km, 80L, 25 km atm/land. Integrations ongoing • Code: Fortran with MPI/OpenMP (including some nested OpenMP threading) Golaz, J.-C., et al. (2019). ”The DOE E3SM coupled model version 1: Overview and evaluation at standard resolution.” J. Adv. Model. Earth Syst., 11, 2089-2129. https://doi.org/10.1029/2018MS001603 E3SM v2 Development E3SMv2 was supposed to incorporate minor changes compared to v1 • Not quite… significant structural changes have taken place • Tri-grid configuration – Land and river component now on separate common ½ deg grid – Increased land resolution, especially over Northern land areas – Enables closer coupling between land and river model: water management, irrigation, inundation, … – 3 grids: atmosphere, land/river, ocean/sea-ice. -

Long Term Vision for Larsoft: Overview

Long term vision for LArSoft: Overview Adam Lyon LArSoft Workshop 2019 25 June 2019 Long term computing vision • You already know this… https://www.karlrupp.net/2018/02/42-years-of-microprocessor-trend-data/ !2 The response - Multicore processors 1 S = 1 − p Examples… Intel Xeon “Haswell”: 16 cores @ 2.3 GHz; 32 threads; Two 4-double vector units Intel Xeon Phi “Knights Landing (KNL)”: 68 cores @ 1.4 GHz; 272 threads; Two 8-double vector units Nvidia Volta “Tesla V100” GPU: 5120 CUDA cores; 640 Tensor cores @ ~1.2 GHz https://upload.wikimedia.org/wikipedia/commons/e/ea/AmdahlsLaw.svg Grid computing uses one or more “cores” (really threads) per job Advantages of multi-threading… • Main advantage is memory sharing • If you are looking for speedup, remember Amdahl’s law Vectorization is another source of speedup … maybe https://cvw.cac.cornell.edu/vector/performance_amdahl !3 High Performance Computing (next 5 years) ORNL AMD/Cray https://www.slideshare.net/insideHPC/exascale-computing-project-software-activities !4 Heterogenous Computing • Future: multi-core, limited power/core, limited memory/core, memory bandwidth increasingly limiting • The old days are not coming back • The DOE is spending $2B on new “Exascale” machines (1018 floating point operations/sec) … - OLCF: Summit IBM CPUs & 27K NVIDIA Volta GPUs (#1 supercomputer in the world) - NERSC: Perlmutter AMD CPUs & NVIDIA Tensor GPUs (2020) - ALCF: Aurora Intel CPUs & Intel Xe GPUs (early 2021) — first US Exascale machine - OLCF: Frontier AMD CPUs & AMD GPUs (later 2021) - Exascale -

Multi-Platform Performance Portability for QCD Simulations Aka How I Learned to Stop Worrying and Love the Compiler

Multi-Platform Performance Portability for QCD Simulations aka How I learned to stop worrying and love the compiler Peter Boyle Theoretical Particle Physics University of Edinburgh • DiRAC funded by UK Science and Technology Facilities Council (STFC) • National computing resource for Theoretical Particle Physics, Nuclear Physics, Astronomy and Cosmology • Installations in Durham, Cambridge, Edinburgh and Leicester • 3 system types with domain focused specifications • Memory Intensive: simulate largest universe possible, memory capacity • Extreme Scaling: scalable, high delivered high floating point, strong scaling • Data Intensive : throughput, heterogenous, high speed I/O • Will discuss: Extreme Scaling system for QCD simulation (2018, upgrade 208) Portability to future hardware Convergence of HPC and AI needs Data motion is the rate determining step 4. Performance Results fact may have an impact on both machine intercomparisons and the selection of systems for procurement. In the former case, architec- 4.1 STREAM tures become compared based largely on their peak memory band- To measure the memory bandwidth performance, which can signif- width and not the inherent computational advantages available on icantly impact many scientific codes, we ran the STREAM bench- each processor. In the latter case, application developers and sys- mark• onFloating each of the point test platforms. is now For free each platform, we config- tem procurement teams may find it easier to choose machines with ured the test to utilize 60% of the on–node memory. For Hopper higher peak memory bandwidth rather than refactoring their appli- and Edison,• Data we motion ran separate is now copies key of STREAM on each of the cations, or researching new algorithms, to better use the CPU. -

Intel Rendering Framework and Intel Xe Architecture Poised to Advance S

Intel Rendering Framework and Intel Xe architecture poised to advance s... https://www.guru3d.com/news-story/intel-rendering-framework-and-inte... Guru3D.com » News » Intel Rendering Framework and Intel Xe architecture poised to advance studio workflows by Hilbert Hagedoorn on: 05/01/2019 10:00 AM | source: | 4 comment(s) Xe architecture roadmap for data center optimized rendering includes ray tracing hardware acceleration support for the Intel Rendering Framework family of API’s and libraries. -- Intel -- Intel Rendering Framework and Intel Xe architecture poised to advance studio workflows By Jim Jeffers | May 1, 2019 New Reviews As the world’s visually creative leaders come together at FMX’19 in Stuttgart this week, I would like to share some Samsung 970 EVO Plus 2TB NVMe M.2. SSD review exciting news regarding Intel and its partners’ efforts to continue delivering leadership solutions for advanced, feature Guru3D Rig of the Month - May 2019 rich, photorealistic and high-performance workflows for studio quality asset creation. As I announced in my Promo: URCDKey Summer Sale Windows 10 Pro for SIGGRAPH’18 blog, Intel® Rendering Framework open source software libraries continue to increase in features, $11 performance and ease of use. DeepCool Matrexx 70 Chassis review Intel® Embree, Intel® OSPRay, Intel® OpenSWR, and the recently released Intel® Open Image Denoise provide Noctua NH-U12A cooler review open source rendering kernels and middleware mapped to Intel® architecture multi-core parallel processors for Cooler Master MasterBox NR600 review maximum flexibility, performance and technical transparency. Intel® Xeon® processors running Embree supported MSI to unveil 10th Anniversary RTX 2080 Ti Lightning renderers are used to provide state-of-the-art visual effects in animated movies, including Dreamworks* MoonRay* Edition renderer, used to render How to Train Your Dragon: The Hidden World that is in theatres now. -

2021 H1 Brochure

2021 H1 BROCHURE MSI Exclusive Stores Bengaluru Kolkata #906, 6th Block, GNR , 6th Block, GNR Plaza, 80 Feet Road, Koramangala 31, Chittaranjan Avenue, Beside Chandi Chowk Metro Station Gate No 5 Delhi Lucknow G-5 Pragati House, Ground Floor, Nehru Place Shop no 4, 1st Floor, One Awadh Centre Mall, Vibhuti Khand, Gomtinagar Hyderabad Pune 110' Sarojini Devi Road' Secunderabad Shop No. 4, Pinacle Prestige, Sadashiv Peth, Pune, Maharashtra MASTERPIECE IN PROCESS MSI has devoted countless resources into research and development not only to pursue innovative features, but also to ensure ultimate stability. Over 1900 strict tests are run throughout the production process as a way to provide gamers the best gaming experience. BEST-SELLING GAMING LAPTOP BRAND MSI gaming laptops are built with state-of-the-art gaming technology that promises quality and performance that has been continuously well-recognized by media and gamers around the world. With a full range of selection, from portable powerhouses to high-end desktop replacements, any gaming enthusiast can expect to have their needs met. ”Micro-Star International (MSI) shipped a total of 1.2 million gaming notebooks in 2018, fending off the competitions from Asustek Computer with devices from its gaming sub-brands to become the largest supplier in the gaming notebook market in terms of shipments and profitability.”- DIGITIMES Survey by UFC-Que Choisir across 43,000 people in Europe reveals MSI as the most reliable PC brand. *https://www.macg.co/materiel/2019/03/ufc-que-choisir-un-indice-de-fiabilite-pas-tendre-pour-apple-105660 No.1 Most Reliable PC Brand in EU SUPPORT & VALUE & REVIEWS DESIGN WARRANTY INNOVATION SELECTION +7 34/40 13/15 12/20 8/10 11/15 4TH “MSI...fully propelled itself into the top 5 best laptop brands.