PPR for AMD Family 17H Model 01H B1

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Titan X Amd 1.2 V4 Ig 20210319

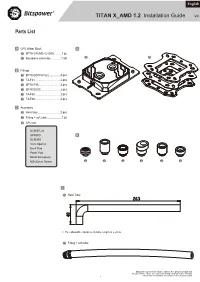

English TITAN X_AMD 1.2 Installation Guide V4 Parts List A CPU Water Block A A-1 BPTA-CPUMS-V2-SKA ..........1 pc A-1 A-2 A-2 Backplane assembly ..............1 set B Fittings B-1 BPTA-DOTFH1622 ...............4 pcs B-2 TA-F61 ...................................2 pcs B-3 BPTA-F95 ..............................2 pcs B-4 BP-RIGOS5 ...........................2 pcs B-5 TA-F60 ..................................2 pcs B-6 TA-F40 ..................................2 pcs C Accessory C-1 Hard tube ..............................2 pcs C-2 Fitting + soft tube ....................1 pc C-3 CPU set SCM3FL20 SPRING B SCM3F6 1mm Spacer Back Pad Paste Pad Metal Backplane M3x32mm Screw B-1 B-2 B-3 B-4 B-5 B-6 C C-1 Hard Tube ※ The allowable variance in tube length is ± 2mm C-2 Fitting + soft tube Bitspower reserves the right to change the product design and interpretations. These are subject to change without notice. Product colors and accessories are based on the actual product. — 1 — I. AMD Motherboard system 54 AMD SOCKET 939 / 754 / 940 IN 48 AMD SOCKET AM4 AMD SOCKET AM3 / AM3+ AMD SOCKET AM2 / AM2+ AMD SOCKET FM1 / FM2+ Bitspower Fan and DRGB RF Remote Controller Hub (Not included) are now available at microcenter.com DRGB PIN on Motherboard or other equipment. 96 90 BPTA-RFCHUB The CPU water block has a DRGB cable, which AMD SOCKET AM4 AMD SOCKET AM3 AM3+ / AMD SOCKET AM2 AM2+ / AMD SOCKET FM1 / FM2+ can be connected to the DRGB extension cable of the radiator fans. Fan and DRGB RF Remote Motherboard Controller Hub (Not included) OUT DRGB LED Do not over-tighten the thumb screws Installation (SCM3FL20). -

Vorbereitung Auf Comptia A+

Markus Kammermann, Ramon Kratzer CompTIA A+ Systemtechnik und Support von A bis Z Vorbereitung auf die Prüfungen 220-901 und 220-902 Bibliografische Information der Deutschen Nationalbibliothek Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über <http://dnb.d-nb.de> abrufbar. ISBN 978-3-95845-466-8 4. Auflage 2016 www.mitp.de E-Mail: [email protected] Telefon: +49 7953 / 7189 – 079 Telefax: +49 7953 / 7189 – 082 © 2016 mitp Verlags GmbH & Co. KG Dieses Werk, einschließlich aller seiner Teile, ist urheberrechtlich geschützt. Jede Verwertung außerhalb der engen Grenzen des Urheberrechtsgesetzes ist ohne Zustimmung des Verlages unzulässig und straf- bar. Dies gilt insbesondere für Vervielfältigungen, Übersetzungen, Mikroverfilmungen und die Einspei- cherung und Verarbeitung in elektronischen Systemen. Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Werk berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften. Dieses Lehrmittel wurde für das CompTIA Authorized Curriculum durch ProCert Labs geprüft und ist CAQC-zertifiziert. Weitere Informationen zu dieser Qualifizierung erhalten Sie unter www.comptia.org/ certification/caqc/ sowie unter der Adresse www.procertlabs.com Das Bildmaterial in diesem Buch, soweit es nicht von uns selber erstellt -

Motherboards, Processors, and Memory

220-1001 COPYRIGHTED MATERIAL c01.indd 03/23/2019 Page 1 Chapter Motherboards, Processors, and Memory THE FOLLOWING COMPTIA A+ 220-1001 OBJECTIVES ARE COVERED IN THIS CHAPTER: ✓ 3.3 Given a scenario, install RAM types. ■ RAM types ■ SODIMM ■ DDR2 ■ DDR3 ■ DDR4 ■ Single channel ■ Dual channel ■ Triple channel ■ Error correcting ■ Parity vs. non-parity ✓ 3.5 Given a scenario, install and configure motherboards, CPUs, and add-on cards. ■ Motherboard form factor ■ ATX ■ mATX ■ ITX ■ mITX ■ Motherboard connectors types ■ PCI ■ PCIe ■ Riser card ■ Socket types c01.indd 03/23/2019 Page 3 ■ SATA ■ IDE ■ Front panel connector ■ Internal USB connector ■ BIOS/UEFI settings ■ Boot options ■ Firmware upgrades ■ Security settings ■ Interface configurations ■ Security ■ Passwords ■ Drive encryption ■ TPM ■ LoJack ■ Secure boot ■ CMOS battery ■ CPU features ■ Single-core ■ Multicore ■ Virtual technology ■ Hyperthreading ■ Speeds ■ Overclocking ■ Integrated GPU ■ Compatibility ■ AMD ■ Intel ■ Cooling mechanism ■ Fans ■ Heat sink ■ Liquid ■ Thermal paste c01.indd 03/23/2019 Page 4 A personal computer (PC) is a computing device made up of many distinct electronic components that all function together in order to accomplish some useful task, such as adding up the numbers in a spreadsheet or helping you to write a letter. Note that this defi nition describes a computer as having many distinct parts that work together. Most PCs today are modular. That is, they have components that can be removed and replaced with another component of the same function but with different specifi cations in order to improve performance. Each component has a specifi c function. Much of the computing industry today is focused on smaller devices, such as laptops, tablets, and smartphones. -

MSI MEG X570 GODLIKE Datasheet

MOTHERBOARD MEG X570 GODLIKE ONE BOARD TO RULE THEM ALL FEATURE Mystic Light Infinity II Personalize your PC with 16.8 million colors / 29 effects with MSI Mystic Light APP, making your system come alive with infinity. Dynamic Dashboard Built-in dynamic panel that indicates the status of GODLIKE and shows off your own personality. Lightning Gen4 solution The latest Gen4 PCI-E and M.2 solution with up to 64GB/s bandwidth for maximum transfer speed. Frozr Heatsink Design Designed with the patented fan and double ball bearings to SPECIFICATION provide best performance for enthusiast gamers and prosumers. Extended Heat-Pipe Design Enlarge the surface of heat dissipation, connecting from Model Name MEG X570 GODLIKE MOS heatsink to chipset heatsink. CPU Support Supports 2nd and 3rd Gen AMD Ryzen™ / Ryzen™ with Radeon™ Vega Graphics and 2nd Gen AMD Ryzen™ with Radeon™ Graphics Desktop Processors M.2 Shield FROZR CPU Socket Socket AM4 Strengthened built-in M.2 thermal solution. Keeps M.2 SSDs ® Chipset AMD X570 Chipset safe while preventing throttling, making them run faster. Graphics Interface 4 x PCI-E 4.0 x16 slots Supports 2-way SLI / 4-way CrossFire WIFI 6 Memory Support 4 DIMMs, Dual Channel DDR4 Storage 3 x Lightning Gen 4 M.2 slots The latest wireless solution supports MU-MIMO and BSS 6 x SATA 6Gb/s ports color technology, delivering speeds up to 2400Mbps. USB Ports 5 x USB 3.2 (Gen2, 3A+2C) + 6 x USB 3.2 (Gen1) + 4 x USB 2.0 Core Boost LAN Killer™ E3000 2.5G LAN, Killer™ E2600 Gigabit LAN Wi-Fi / BT Killer™ Wi-Fi 6 AX1650 Combining dual 8 pin power connectors and IR digital power Audio 8-Channel (7.1) HD Audio with XTREME AUDIO DAC design, the GODLIKE is ready for more cores also provide better performance. -

AMD Ryzen™ PRO & Athlon™ PRO Processors Quick Reference Guide

AMD Ryzen™ PRO & Athlon™ PRO Processors Quick Reference guide AMD Ryzen™ PRO Processors with Radeon™ Graphics for Business Laptops (Socket FP6/FP5) 1 Core/Thread Frequency Boost/Base L2+L3 Cache Graphics Node TDP Intel vPro Core/Thread Frequency Boost*/Base L2+L3 Cache Graphics Node TDP AMD PRO technologies COMPARED TO 4.9/1.1 Radeon™ 6/12 UHD AMD Ryzen™ 7 PRO 8/16 Up to 12MB Graphics 7nm 15W intel Intel Core i7 10810U GHz 13MB 4750U 4.1/1.7 GHz CORE i7 14nm 15W (7 Cores) 10th Gen Intel Core i7 10610U 4/8 4.9/1.8 9MB UHD GHz AMD Ryzen™ 7 PRO Up to Radeon™ intel 4/8 6MB 10 12nm 15W 4.8/1.9 3700U 4.0/2.3 GHz Vega CORE i7 Intel Core i7 8665U 4/8 9MB UHD 14nm 15W 8th Gen GHz Radeon™ AMD Ryzen™ 5 PRO 6/12 Up to 11MB Graphics 7nm 15W intel 4.4/1.7 4650U 4.0/2.1 GHz CORE i5 Intel Core i5 10310U 4/8 7MB UHD 14nm 15W GHz (6 Cores) 10th Gen AMD Ryzen™ 5 PRO 4/8 Up to 6MB Radeon™ 12nm 15W intel 4.1/1.6 3500U 3.7/2.1 GHz Vega8 CORE i5 Intel Core i5 8365U 4/8 7MB UHD 14nm 15W th GHz 8 Gen Radeon™ AMD Ryzen™ 3 PRO 4/8 Up to 6MB Graphics 7nm 15W intel 4.1/2.1 4450U 3.7/2.5 GHz CORE i3 Intel Core i3 10110U 2/4 5MB UHD 14nm 15W (5 Cores) 10th Gen GHz AMD Ryzen™ 3 PRO 4/4 Up to 6MB Radeon™ 12nm 15W intel 3.9/2.1 3300U 3.5/2.1 GHz Vega6 CORE i3 Intel Core i3 8145U 2/4 4.5MB UHD 14nm 15W 8th Gen GHz AMD Athlon™ PRO Processors with Radeon™ Vega Graphics for Business Laptops (Socket FP5) AMD Athlon™ PRO Up to Radeon™ intel Intel Pentium 4415U 2/4 2.3 GHz 2.5MB HD 610 14nm 15W 300U 2/4 3.3/2.4 GHz 5MB Vega3 12nm 15W 1. -

Prime B450m-A

PRIME B450M-A Motherboard E14212 First Edition May 2018 Copyright © 2018 ASUSTeK COMPUTER INC. All Rights Reserved. No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). Product warranty or service will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing. ASUS PROVIDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSINESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. SPECIFICATIONS AND INFORMATION CONTAINED IN THIS MANUAL ARE FURNISHED FOR INFORMATIONAL USE ONLY, AND ARE SUBJECT TO CHANGE AT ANY TIME WITHOUT NOTICE, AND SHOULD NOT BE CONSTRUED AS A COMMITMENT BY ASUS. ASUS ASSUMES NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR INACCURACIES THAT MAY APPEAR IN THIS MANUAL, INCLUDING THE PRODUCTS AND SOFTWARE DESCRIBED IN IT. -

Socket Am4 X570 Motherboards a Groundbreaking New Platform - Ryzentm 3000 Ready Bleeding-Edge Hardware for Gamers, Content Creators, and Prosumers

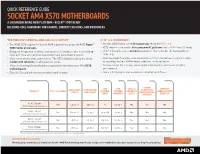

QUICK REFERENCE GUIDE SOCKET AM4 X570 MOTHERBOARDS A GROUNDBREAKING NEW PLATFORM - RYZENTM 3000 READY BLEEDING-EDGE HARDWARE FOR GAMERS, CONTENT CREATORS, AND PROSUMERS THE INDUSTRY LEADING AMD AM4 X570 CHIPSET PCIE® 4.0 LEADERSHIP 1 • The AMD X570 chipset for Socket AM4 supports the powerful AMD Ryzen™ • 3rd Gen AMD Ryzen is the first processor ready for PCIe® 4.0 . 3000 Series processors. • X570 chipset is the world's first consumer PC platform that is PCIe® Gen 4.0 Ready. • Designed for gamers, creators, and everyone in between who need cutting- • PCIe® 4.0 enables up to 32 GB/s bandwidth. That's double the bandwidth of edge performance, optimized bandwidth and breathtaking speed. PCIe® 3.0. • More connectivity, more convenience. The X570 chipset enables the most • More bandwidth enables new generations of high-performance graphics cards, modern I/O solutions for all consumer needs. networking devices, NVMe drives, ethernet cards and more. • Major motherboard manufacturers expected to introduce over fifty X570 • Achieve faster file storage, faster application loading, and faster graphics motherboards. performance. • Elite X570 models from most motherboard vendors. • Reduce bottlenecks and accelerate consumer workflows. RYZEN USB USB DUAL x8 MEMORY SATA 6GBPS SUPERSPEED+ PROCESSOR PRODUCT PCIe® 4.0 LANES HISPEED HISPEED GRAPHICS OVERCLOCKING PORTS USB 10GBPS OVERCLOCKING 5GBPS 480MBPS SLOTS ENABLED ENABLED X570 Chipset Yes Up to 14 Up to 12 0 Up to 4 Yes Yes Yes With 3rd Gen Ryzen Processor X470 Chipset No Up to 12 Up to 2 Up to 10 Up to 6 Yes Yes Yes With 3rd Gen Ryzen Processor B450 Chipset No Up to 6 Up to 2 Up to 6 Up to 6 No Yes Yes With 3rd Gen Ryzen Processor A320 Chipset Not Compatible With 3rd Gen Ryzen Processor No Up to 6 Up to 1 Up to 5 Up to 6 No No No *This chart illustrates competitive product placement and is not necessarily an indication of relative performance. -

POWERING the WORKFORCE AMD Ryzen™ PRO Processors

POWERING THE WORKFORCE AMD Ryzen™ PRO Processors AMD HAS BEEN LEADING AMD is committed to delivering technology features that enable customers to invest with confidence. TECHNOLOGICAL INNOVATION FOR 50 YEARS • 1st to break the 1 GHz barrier 1 SECURITY BUILT IN 2 COMPETITIVE PERFORMANCE • 1st to create 64-bit x86 THE WORLD’S ONLY PROCESSOR FAMILY processor standard WITH FULL MEMORY ENCRYPTION AS A STANDARD SECURITY FEATURE1 • 1st native dual core & quad core UP TO UP TO x86 processors • 1st x86 quad core SoC 2X 9% • 1st 64-bit ARM®-based SoC in HELPS DEFEND AGAINST COLD BOOT ATTACKS the industry FASTER PERFORMANCE FASTER PERFORMANCE SUPPORTS ARCHITECTED WITH A THAN A 2 YEAR OR OLDER PC2 VS INTEL3 • 1st with compute & graphics WINDOWS 10 SECURITY FOCUS ON SECURITY processing on the same chip • 1st 16-core desktop processor POWER THE WORK DAY IN MODERN DEVICES At AMD we strive to provide 3 4 organizations more choice and flexibility with their IT budget UP TO PROFESSIONALFEATURES so they can join us in pushing innovation forward. 14.75 HOURS BATTERY LIFE4 MODERN DESIGNS ON THE HP ELITEBOOK 745 G6 POWERED BY AMD RYZEN TM 7 PRO 3700U PROCESSORS. COMPETITIVE PERFORMANCE SECURITY BUILT-IN PROFESSIONAL FEATURES • PRO processors from AMD deliver the power efficiency • The ONLY processor family with full memory encryption • Open standard, DASH manageability from the DMTF, and performance needed to keep every level of business as a standard feature.1 AMD Memory Guard helps encrypt backed by leading technology companies available on all user productive no matter how demanding the workload. -

AMD Raven Ridge

DELIVERING A NEW LEVEL OF VISUAL PERFORMANCE IN AN SOC AMD “RAVEN RIDGE” APU Dan Bouvier, Jim Gibney, Alex Branover, Sonu Arora Presented by: Dan Bouvier Corporate VP, Client Products Chief Architect AMD CONFIDENTIAL RAISING THE BAR FOR THE APU VISUAL EXPERIENCE Up to MOBILE APU GENERATIONAL 200% MORE CPU PERFORMANCE PERFORMANCE GAINS Up to 128% MORE GPU PERFORMANCE Up to 58% LESS POWER FIRST “Zen”-based APU CPU Performance GPU Performance Power HIGH-PERFORMANCE AMD Ryzen™ 7 2700U 7th Gen AMD A-Series APU On-die “Vega”-based graphics Scaled GPU Managed Improved Upgraded Increased LONG BATTERY LIFE and CPU up to power delivery memory display package Premium form factors reach target and thermal bandwidth experience performance frame rate dissipation efficiency density 2 | AMD Ryzen™ Processors with Radeon™ Vega Graphics - Hot Chips 30 | * See footnotes for details. “RAVEN RIDGE” APU AMD “ZEN” x86 CPU CORES CPU 0 “ZEN” CPU CPU 1 (4 CORE | 8 THREAD) USB 3.1 NVMe PCIe FULL PCIe GPP ----------- ----------- Discrete SYSTEM 4MB USB 2.0 SATA GFX CONNECTIVITY CPU 2 CPU 3 L3 Cache X64 DDR4 HIGH BANDWIDTH SOC FABRIC System Infinity Fabric & MEMORY Management SYSTEM Unit ACCELERATED Platform Multimedia Security MULTIMEDIA Processor Engines AMD GFX+ 1MB L2 EXPERIENCE X64 DDR4 (11 COMPUTE UNITS) Cache Video Audio Sensor INTEGRATED CU CU CU CU CU CU Display Codec ACP Fusion Controller Next SENSOR Next Hub FUSION HUB CU CU CU CU CU AMD “VEGA” GPU UPGRADED DISPLAY ENGINE 3 | AMD Ryzen™ Processors with Radeon™ Vega Graphics - Hot Chips 30 | SIGNIFICANT DENSITY INCREASE “Raven Ridge” die BGA Package: 25 x 35 x 1.38mm Technology: GLOBALFOUNDRIES 14nm – 11 layer metal Transistor count: 4.94B 59% 16% Die Size: 209.78mm2 more transistors smaller die than prior generation “Bristol Ridge” APU 4 | AMD Ryzen™ Processors with Radeon™ Vega Graphics - Hot Chips 30 | * See footnotes for details. -

SMBIOS Specification

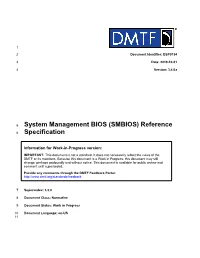

1 2 Document Identifier: DSP0134 3 Date: 2019-10-31 4 Version: 3.4.0a 5 System Management BIOS (SMBIOS) Reference 6 Specification Information for Work-in-Progress version: IMPORTANT: This document is not a standard. It does not necessarily reflect the views of the DMTF or its members. Because this document is a Work in Progress, this document may still change, perhaps profoundly and without notice. This document is available for public review and comment until superseded. Provide any comments through the DMTF Feedback Portal: http://www.dmtf.org/standards/feedback 7 Supersedes: 3.3.0 8 Document Class: Normative 9 Document Status: Work in Progress 10 Document Language: en-US 11 System Management BIOS (SMBIOS) Reference Specification DSP0134 12 Copyright Notice 13 Copyright © 2000, 2002, 2004–2019 DMTF. All rights reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

Procesory AMD

Procesory AMD Mariusz Nowak 2019 Gniazdo PGA Socket AM2 • Liczba pinów: 940 • Rok wprowadzenia: 2006 • Magistrale: FSB 200 MHz, HyperTransport 2.0 • Obsługa kontrolera pamięci DDR2 zintegrowanego z procesorem • Athlon 64, Sempron, Opteron, Phenom Gniazdo PGA Socket AM2+ • Liczba pinów: 940 • Rok wprowadzenia: 2007 • Magistrale: FSB 200 MHz, HyperTransport 3.0 (2.6 GHz) • Obsługa procesorów 1-, 2-, 3-, 4-rdzeniowych • Athlon 64, Athlon II, Opteron, Phenom, Phenom II Gniazdo PGA Socket AM3 • Liczba pinów: 941 • Rok wprowadzenia: 2009 • Magistrale: FSB 200 MHz, HyperTransport 3.0 (2.6 GHz) • Obsługa DDR3 • Athlon II, Phenom II, Sempron, Opteron Gniazdo PGA Socket AM4 • Liczba pinów: 1331 • Rok wprowadzenia: 2016 • Obsługa DDR4, PCIe 3.0 i 4.0 • Wsparcie dla architektury ZEN (procesory Ryzen, Athlon) Gniazdo LGA Socket TR4 • Liczba pinów: 4094 • Rok wprowadzenia: 2017 • Obsługa DDR4 (8 modułów, 4 kanały), PCIe 3.0 i 4.0 • Wsparcie dla architektury ZEN (super wydajne procesory Ryzen Threadripper) Oznaczenia najnowszych procesorów AMD (Zen) Zapotrzebowanie na energię Nazwa • (brak) - komputer stacjonarny Ryzen 5 3 5 50 H • U - komputer przenośny handlowa • X - wysoka częstotliwość taktowania • WX - duża ilość rdzeni • G - z układem graficznym • E - obniżone zapotrzebowanie na energię (komputer stacjonarny) • M - obniżone zapotrzebowanie na Seria Generacja Wydajność Numer energię (komputer przenośny) • H - wysokowydajny komputer • 3 (mała wydajność) • 1 • 9 (ekstremalna) modelu przenośny • 5 (średnia wydajność) • 2 • 8 (najwyższa) procesora •