Operating System Support Matrix

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

DAN189 EXAR UARTS in GPS APPLICATIONS March 2007 EXAR UARTS in GPS APPLICATIONS

DAN189 EXAR UARTS IN GPS APPLICATIONS March 2007 EXAR UARTS IN GPS APPLICATIONS 1.0 INTRODUCTION This application note describes where an Exar UART can be used in a Global Positioning System (GPS) application. GPS has traditionally been used in military applications such as marine navigation, aircraft navigation, and weapon’s guidance. However, GPS applications have recently expanded to industrial and consumer applications such as vehicle navigation systems, fleet management, and personal navigation. In these applications, the Exar UART can be used in the GPS receiver and in the GPS application. FIGURE 1. GPS APPLICATION EXAMPLES GPS Applications Marine Navigation System Aircraft Navigation System Vehicle Navigation System Fleet Management System Personal Navigation System GPS Receiver TX RX UART RX TX UART 1.1 GPS Receiver A GPS receiver typically includes the following: • RF block for receiving the GPS data and converting it to digital data • Microprocessor for processing the data • ROM to store the firmware for processing the data • RAM used by the microprocessor for data processing • UART to send data to the GPS application The figure below shows a block diagram of a GPS receiver. FIGURE 2. GPS RECEIVER BLOCK DIAGRAM ROM RAM RF Block TX Microprocessor UART RX 1 DAN189 EXAR UARTS IN GPS APPLICATIONS The figure below shows a block diagram of an automobile GPS navigation system: FIGURE 3. AUTOMOBILE GPS NAVIGATION SYSTEM EXAMPLE Keypad ROM RAM Radio CD RX GPS UART Microprocessor DVD TX LCD The UART that has been used in the GPS receiver or in the GPS application has typically been an industry standard 16550 UART or a UART that is available on the microprocessor. -

Cobia Database Articles Final Revision 2.0, 2-1-2017

Revision 2.0 (2/1/2017) University of Miami Article TITLE DESCRIPTION AUTHORS SOURCE YEAR TOPICS Number Habitat 1 Gasterosteus canadus Linné [Latin] [No Abstract Available - First known description of cobia morphology in Carolina habitat by D. Garden.] Linnaeus, C. Systema Naturæ, ed. 12, vol. 1, 491 1766 Wild (Atlantic/Pacific) Ichthyologie, vol. 10, Iconibus ex 2 Scomber niger Bloch [No Abstract Available - Description and alternative nomenclature of cobia.] Bloch, M. E. 1793 Wild (Atlantic/Pacific) illustratum. Berlin. p . 48 The Fisheries and Fishery Industries of the Under this head was to be carried on the study of the useful aquatic animals and plants of the country, as well as of seals, whales, tmtles, fishes, lobsters, crabs, oysters, clams, etc., sponges, and marine plants aml inorganic products of U.S. Commission on Fisheries, Washington, 3 United States. Section 1: Natural history of Goode, G.B. 1884 Wild (Atlantic/Pacific) the sea with reference to (A) geographical distribution, (B) size, (C) abundance, (D) migrations and movements, (E) food and rate of growth, (F) mode of reproduction, (G) economic value and uses. D.C., 895 p. useful aquatic animals Notes on the occurrence of a young crab- Proceedings of the U.S. National Museum 4 eater (Elecate canada), from the lower [No Abstract Available - A description of cobia in the lower Hudson Eiver.] Fisher, A.K. 1891 Wild (Atlantic/Pacific) 13, 195 Hudson Valley, New York The nomenclature of Rachicentron or Proceedings of the U.S. National Museum Habitat 5 Elacate, a genus of acanthopterygian The universally accepted name Elucate must unfortunately be supplanted by one entirely unknown to fame, overlooked by all naturalists, and found in no nomenclator. -

Common Errors in English by Paul Brians [email protected]

Common Errors in English by Paul Brians [email protected] http://www.wsu.edu/~brians/errors/ (Brownie points to anyone who catches inconsistencies between the main site and this version.) Note that italics are deliberately omitted on this page. What is an error in English? The concept of language errors is a fuzzy one. I'll leave to linguists the technical definitions. Here we're concerned only with deviations from the standard use of English as judged by sophisticated users such as professional writers, editors, teachers, and literate executives and personnel officers. The aim of this site is to help you avoid low grades, lost employment opportunities, lost business, and titters of amusement at the way you write or speak. But isn't one person's mistake another's standard usage? Often enough, but if your standard usage causes other people to consider you stupid or ignorant, you may want to consider changing it. You have the right to express yourself in any manner you please, but if you wish to communicate effectively you should use nonstandard English only when you intend to, rather than fall into it because you don't know any better. I'm learning English as a second language. Will this site help me improve my English? Very likely, though it's really aimed at the most common errors of native speakers. The errors others make in English differ according to the characteristics of their first languages. Speakers of other languages tend to make some specific errors that are uncommon among native speakers, so you may also want to consult sites dealing specifically with English as a second language (see http://www.cln.org/subjects/esl_cur.html and http://esl.about.com/education/adulted/esl/). -

Ds430 Opb 16550 Uart

0 OPB 16550 UART (v1.00d) DS430 December 2, 2005 0 0 Product Specification Introduction LogiCORE™ Facts This document provides the specification for the OPB Core Specifics 16550 UART (Universal Asynchronous QPro™-R Virtex™-II, QPro Receiver/Transmitter) Intellectual Property (IP). Virtex-II, Spartan™-II, Spartan-IIE, Supported Device Spartan-3, Spartan-3E, Virtex, The OPB 16550 UART described in this document has Family Virtex-II, Virtex-II Pro, Virtex-4, been designed incorporating features described in Virtex-E National Semiconductor PC16550D UART with FIFOs data Version of Core opb_uart16550 v1.00d sheet (June,1995),Discontinued (http://www.national.com/pf/PC/PC16550D.html). Resources Used The National Semiconductor PC16550D data sheet is Min Max referenced throughout this document and should be Slices 283 417 used as the authoritative specification. Differences LUTs 328 545 between the National Semiconductor implementation and the OPB 16550 UART Point Design implementation FFs 275 338 are highlighted and explained in Specification Block RAMs Exceptions. Provided with Core Features Documentation Product Specification • Hardware and software register compatible with all Design File Formats VHDL standard 16450 and 16550 UARTs Constraints File N/A • Implements all standard serial interface protocols Verification N/A - 5, 6, 7, or 8 bits per character Instantiation Template N/A - Odd, Even, or no parity detection and generation Reference Designs None - 1, 1.5, or 2 stop bit detection and generation Design Tool Requirements - Internal baud rate generator and separate receiver Xilinx Implementation ISE 6.1i or later clock input Tools - Modem control functions Verification ModelSim SE/EE 5.8e or later Simulation IPModelSim SE/EE 5.8e or later - False start bit detection and recovery - Prioritized transmit, receive, line status, and Synthesis XST modem control interrupts Support - Line break detection and generation Support provided by Xilinx, Inc. -

Serial Communication Buses

Computer Architecture 10 Serial Communication Buses Made wi th OpenOffi ce.org 1 Serial Communication SendingSending datadata oneone bitbit atat oneone time,time, sequentiallysequentially SerialSerial vsvs parallelparallel communicationcommunication cable cost (or PCB space), synchronization, distance ! speed ? ImprovedImproved serialserial communicationcommunication technologytechnology allowsallows forfor transfertransfer atat higherhigher speedsspeeds andand isis dominatingdominating thethe modernmodern digitaldigital technology:technology: RS232, RS-485, I2C, SPI, 1-Wire, USB, FireWire, Ethernet, Fibre Channel, MIDI, Serial Attached SCSI, Serial ATA, PCI Express, etc. Made wi th OpenOffi ce.org 2 RS232, EIA232 TheThe ElectronicElectronic IndustriesIndustries AllianceAlliance (EIA)(EIA) standardstandard RS-232-CRS-232-C (1969)(1969) definition of physical layer (electrical signal characteristics: voltage levels, signaling rate, timing, short-circuit behavior, cable length, etc.) 25 or (more often) 9-pin connector serial transmission (bit-by-bit) asynchronous operation (no clock signal) truly bi-directional transfer (full-duplex) only limited power can be supplied to another device numerous handshake lines (seldom used) many protocols use RS232 (e.g. Modbus) Made wi th OpenOffi ce.org 3 Voltage Levels RS-232RS-232 standardstandard convertconvert TTL/CMOS-levelTTL/CMOS-level signalssignals intointo bipolarbipolar voltagevoltage levelslevels toto improveimprove noisenoise immunityimmunity andand supportsupport longlong cablecable lengthslengths TTL/CMOS → RS232: 0V = logic zero → +3V…+12V (SPACE) +5V (+3.3V) = logic one → −3V…−12V (MARK) Some equipment ignores the negative level and accepts a zero voltage level as the "OFF" state The "dead area" between +3V and -3V may vary, many receivers are sensitive to differentials of 1V or less Made wi th OpenOffi ce.org 4 Data frame CompleteComplete one-byteone-byte frameframe consistsconsists of:of: start-bit (SPACE), data bits (7, 8), stop-bits (MARK) e.g. -

Massachusetts Institute of Technology Bulletin

d 7I THE DEAN OF SCIEN<C OCT 171972 MASSACHUSETTS INSTITUTE OF TECHNOLOGY BULLETIN REPORT OF THE PRESIDENT 1971 MASSACHUSETTS INSTITUTE OF TECHNOLOGY BULLETIN REPORT OF THE PRESIDENT FOR THE ACADEMIC YEAR 1970-1971 MASSACHUSETTS INSTITUTE OF TECHNOLOGY BULLETIN VOLUME 107, NUMBER 2, SEPTEMBER, 1972 Published by the Massachusetts Institute of Technology 77 MassachusettsAvenue, Cambridge, Massachusetts, five times yearly in October, November, March, June, and September Second class postage paid at Boston, Massachusetts. Issues of the Bulletin include REPORT OF THE TREASURER REPORT OF THE PRESIDENT SUMMER SESSION CATALOGUE PUBLICATIONS AND THESES and GENERAL CATALOGUE Send undeliverable copies and changes of address to Room 5-133 Massachusetts Institute of Technology Cambridge,Massachusetts 02139. THE CORPORATION Honorary Chairman:James R. Killian, Jr. Chairman:Howard W. Johnson President:Jerome B. Wiesner Chancellor: Paul E. Gray Vice Presidentand Treasurer:Joseph J. Snyder Secretary:John J. Wilson LIFE MEMBERS Bradley Dewey, Vannevai Bush, James M. Barker, Thomas C. Desmond, Marshall B. Dalton, Donald F. Carpenter, Thomas D. Cabot, Crawford H. Greenewalt, Lloyd D. Brace, William A. Coolidge, Robert C. Sprague, Charles A. Thomas, David A. Shepard, George J. Leness, Edward J. Hanley, Cecil H. Green, John J. Wilson, Gilbert M. Roddy, James B. Fisk, George P. Gardner, Jr., Robert C. Gunness, Russell DeYoung, William Webster, William B. Murphy, Laurance S. Rockefeller, Uncas A. Whitaker, Julius A. Stratton, Luis A. Ferr6, Semon E. Knudsen, Robert B. Semple, Ir6n6e du Pont, Jr., Eugene McDermott, James R. Killian, Jr. MEMBERS Albert H. Bowker, George P. Edmonds, Ralph F. Gow, Donald A. Holden, H. I. Romnes, William E. -

SCR1 SDK. Altera Arria-V Starter Kit Edition. Quick Start Guide

SCR1 SDK. Altera Arria-V Starter Kit Edition. Quick Start Guide © Syntacore, [email protected] Version 1.4, 2019-04-08 Table of Contents Revision History . 2 1. Setup equipment. 3 1.1. Prerequisites . 3 2. SDK HW assembly . 4 2.1. Connecting serial console . 4 2.2. Pins assignment. 4 3. Arria-V HW image update . 6 4. Booting the new FPGA image . 8 5. Resetting the board: . 9 6. UART connection settings . 9 7. Using UART terminal . 10 7.1. Load binary images to the Memory address . 10 7.2. Example: Dhrystone run from TCM memory . 12 7.3. Using OpenOCD. 13 7.3.1. Installing OpenOCD . 13 7.3.2. Starting the OpenOCD server. 13 7.3.3. Downloading and running an image using OpenOCD. 14 8. Building SDK FPGA-project for the Arria V GX SDK. 16 8.1. General structure of the SDK project. 16 8.2. Additional requirements for compilation . 16 8.3. Building SDK FPGA project. 17 8.3.1. FPGA firmware generation (sof-format) . 17 8.3.2. Converting FPGA-image to the board flash memory image (flash-format) . 17 8.3.3. SDK-specific pins assignment in FPGA-project . 19 8.4. SCR1 SDK FPGA-project functional description . 20 8.4.1. Common project structure . 20 8.4.2. Qsys SoC module structure. 20 8.4.3. Description of the blocks used in the SDK project . 21 8.4.3.1. SCR1-core. 21 8.4.3.2. AXI bridge . 21 8.4.3.3. Opencores UART 16550 IP . 21 8.4.4. -

Low-Profile PCI Cards: a New Approach to Inner Space • Lavalanche Winners! • Distributor Profile Lava I/O News

April 2002 Vol.4 No.4 Inside this issue: • Low-profile PCI cards: A New Approach to Inner Space • Lavalanche Winners! • Distributor profile Lava I/O News Low-Profile PCI Cards: A New Approach to Inner Space Most of us remember our first impression on looking inside the chassis of a desktop or tower computer: is that all there is? Apart from the motherboard, power supply, drives and cables, a few cards, and dust bunnies, things were pretty empty in there. And while we knew that air had to circulate inside the case, the empty spaces inside still seemed a bit large. Notebook computers came along and really confirmed the impression that the inside of typical computers had enough extra space for a game of baseball. sets standards for the PCI bus generally. As well as defining a maximum height for Low-profile PCI cards follow the “PCI Local cards designated as “low-profile”, the low-pro- The reason for all the empty space is historical: Bus Specification, Revision 2.2” or later, but file PCI specification also outlines two low-pro- the original PC's expansion cards were loaded in addition adopt the form factor require- file PCI card lengths —short (called “MD1”) with lots of separate and large components. ments of the new "PCI Engineering Change and long (“MD2”).An MD1 low-profile card has They were rather tall, and needed to be so. Notice —Low Profile PCI Card". Designed as a a maximum length of 4.72" (119.91 mm). An However, as integrated circuit technology collaborative effort by the PCI Special Interest MD2 card is longer than an MD1 card, but not advanced, expansion boards got smaller and Group and companies including IBM and longer than 6.6" (167.64 mm). -

Z182 Com Port Appnote

HIGH PERFORMANCE PC COMMUNICATION Zilog PORT USING THE Z182 MICROCONTROLLER HIGH PERFORMANCE PC COMMUNICATION PORT USING THE Z182 o meet the demands of high speed communications on the Information Superhighway, Zilog's Z182-based PC Communication Port "COMPORT.S™" software code provides the user with increased data buffering capabilities for faster communication between PCs T and modems. INTRODUCTION With the advent of the Information Superhighway, users will handle heavy traffic at only a sustained rate of 57.6 Kbps. be able to access information quickly and easily by means This factor, combined with limited CPU bandwidth (due to of PC/Modem communications. However, user-friendly complex operating systems), means users cannot take full operating systems, capable of processing large amounts advantage of the high throughput that today’s modems of data, become so performance intensive that data com- can accommodate. munication becomes a bottleneck. Although there have been many advances in modem and PC design, a satis- PC Week's labs (July 1992) analyzed the serial card factory solution to the PC/modem communication bottle- bottleneck issue and their tests showed that a standard neck has not been found. serial card could not reliably sustain data transfer over 19.2 Kbps. However, when using a 16550 UART loaded The PC/Modem communication bottleneck is caused by serial card, the user could expect 57.6 Kbps of reliable, the PC standard serial cards used to connect to the sustained data transfer. This is great for V.32bis, but what modems. Conventional serial cards were designed to about V.FAST and beyond? Serial Port Limitations If you look at a PC Standard Serial Card, you will find a 8250 quickly to interrupts in a multi-tasking system? The answer or 16450 UART as well as RS-232 line drivers. -

Objective Is

Lehigh Preserve Institutional Repository Design of a microprocessor-based emulsion polymerization process control facility Dimitratos, John N. 1987 Find more at https://preserve.lib.lehigh.edu/ This document is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion by an authorized administrator of Lehigh Preserve. For more information, please contact [email protected]. Design of a Microprocessor-based Emulsion Polymerization Process Control Facility A research report written in partial fulfillment of the requirements for the degree of Master of Science in Chemical F:ngim·ering, Lehigh University, Bethlehem, Pennsylvania by John N. Dimitratos June 1987 ,. Design of a Microprocessor-based Emulsion Polymerization .. ,_.,,-•• ·, ,, -i •:>:.·.:':' Process Control Facility ' A research report written in partial fulfillment of the requirements for the degree of Master of Science in Chemical Engineering, Lehigh University, Bethlehem, Pennsylvania by John N. Dimitratos June 1987 •1 to my father and my brother there art times when it is hard to decide what should be chosen at what price, and what endured in return for what reward. Perhaps it is still harder to stick to the decision Aristotle (384-322 B.C) Ethics, Book Ill. Abstract The explosion of microcomputer technology and the recent developments in software and hardware products introduce a new horizon of capabilities for the process control engineer. However, taking advantage of this new technology is not something easily done. H the process control engineer has to undertake such a project soon he will have to deal with the different languages the software engineer and the plant operator use. -

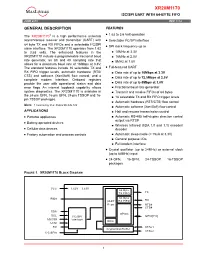

XR20M1170 Data Sheet

XR20M1170 I2C/SPI UART WITH 64-BYTE FIFO JUNE 2019 REV. 1.1.2 GENERAL DESCRIPTION FEATURES 1.62 to 3.6 Volt operation The XR20M11701 is a high performance universal asynchronous receiver and transmitter (UART) with Selectable I2C/SPI interface 64 byte TX and RX FIFOs and a selectable I2C/SPI SPI clock frequency up to slave interface. The XR20M1170 operates from 1.62 to 3.63 volts. The enhanced features in the 18MHz at 3.3V XR20M1170 include a programmable fractional baud 16MHz at 2.5V rate generator, an 8X and 4X sampling rate that 8MHz at 1.8V allows for a maximum baud rate of 16Mbps at 3.3V. The standard features include 16 selectable TX and Full-featured UART RX FIFO trigger levels, automatic hardware (RTS/ Data rate of up to 16Mbps at 3.3V CTS) and software (Xon/Xoff) flow control, and a Data rate of up to 12.5Mbps at 2.5V complete modem interface. Onboard registers provide the user with operational status and data Data rate of up to 8Mbps at 1.8V error flags. An internal loopback capability allows Fractional baud rate generator system diagnostics. The XR20M1170 is available in Transmit and receive FIFOs of 64 bytes the 24-pin QFN, 16-pin QFN, 24-pin TSSOP and 16- 16 selectable TX and RX FIFO trigger levels pin TSSOP packages. Automatic hardware (RTS/CTS) flow control NOTE: 1 Covered by U.S. Patent #5,649,122 Automatic software (Xon/Xoff) flow control APPLICATIONS Halt and resume transmission control Portable appliances Automatic RS-485 half-duplex direction control output via RTS# Battery-operated devices Wireless Infrared (IrDA 1.0 and 1.1) encoder/ Cellular data devices decoder Factory automation and process controls Automatic sleep mode (< 15uA at 3.3V) General purpose I/Os Full modem interface Crystal oscillator (up to 24MHz) or external clock (up to 64MHz) input 24-QFN, 16-QFN, 24-TSSOP, 16-TSSOP packages FIGURE 1. -

Microprocessors and Microcontrollers (EE-231) Main Objectives

Microprocessors and Microcontrollers (EE-231) Main Objectives • 16550 Communication Device • ADC and DAC interfacing 16550 Programmable Communications Interface • National Semiconductor Corp’s PC16550D is a programmable communications interface designed to connect to virtually any type of serial interface. • 16550 is a universal asynchronous receiver/transmitter (UART) fully compatible with Intel microprocessors. • 16550 operates at 0–1.5 M baud. – baud rate is bps (bits transferred per second) including start, stop, data, and parity • 16550 also includes a programmable baud rate generator and separate FIFOs for input and output data to ease the load on the microprocessor. • Each FIFO contains 16 bytes of storage. • The most common communications interface found in the PC and many modems. Asynchronous Serial Data • Asynchronous serial data are transmitted and received without a clock and in frames as shown in figure. – each frame contains a start bit, seven data bits, parity, and one stop bit • Most Internet services use 10 bits, but normally do not use parity. • instead, eight data bits are transferred, replacing parity with a data bit 16550 Functional Description • The device is available as a 40-pin DIP (dual in-line package) or as a 44-pin PLCC (plastic leadless chip carrier). • Two completely separate sections are responsible for data communications. – the receiver and the transmitter • Because each sections is independent, 16550 is able to function in simplex, half-duplex, or full-duplex modes. The pin-out of the 16550 UART. 16550 Functional Description • A major feature of the 16550 is its internal receiver and transmitter FIFO (first-in, first-out) memories. • Because each is 16 bytes deep, the UART requires attention from the processor only after receiving 16 bytes of data.