Renesas HEW for SH Migration Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bill Baggs Cape Florida State Park

Haw Creek Preserve State Park Approved Plan Unit Management Plan STATE OF FLORIDA DEPARTMENT OF ENVIRONMENTAL PROTECTION Division of Recreation and Parks December 16, 2016 TABLE OF CONTENTS INTRODUCTION ...................................................................................1 PURPOSE AND SIGNIFICANCE OF THE PARK ....................................... 1 Park Significance ................................................................................1 PURPOSE AND SCOPE OF THE PLAN..................................................... 2 MANAGEMENT PROGRAM OVERVIEW ................................................... 7 Management Authority and Responsibility .............................................. 7 Park Management Goals ...................................................................... 8 Management Coordination ................................................................... 8 Public Participation ..............................................................................9 Other Designations .............................................................................9 RESOURCE MANAGEMENT COMPONENT INTRODUCTION ................................................................................. 11 RESOURCE DESCRIPTION AND ASSESSMENT..................................... 12 Natural Resources ............................................................................. 12 Topography .................................................................................. 12 Geology ...................................................................................... -

Equipment For' River Measurements

.. UNITED STATES DEPARTMENT OF THE INTERIOR GEOLOGICAL SURVEY WATER RESOURCES BRANCH EQUIPMENT FOR' RIVER MEASUREMENTS " PLANS AND SPECIFICATIONS FOR REINFORCED CONCRETE HOUSE AND WELL FOR WATER-STAGE RECORDERS ARRANGED BY LASLEY LEE DISTRICT ENGINEER, COLUMBUS, OHIO • 1933 DlI'I\IITMDlT 0' THI INnIUOII' UNITEO STATES GEOl.OGICAL SURVEY WATER RESOURCES BRANCH EQUIPMENT FOR RIVER MEASUREMENTS CABLE TOWER AND CAR WATER-STAGE RECORDER HOUSE AND WELL CABLE TOWER AND CAR Chelan River, Chelan. Wash. Alle8heny River. Franklin, Pa. Columbia River, Rock Island. wash. MEASUREMENT BY WADING MEASUREMENT FROM CABLE MEASUREMENT FROM BRIDGE MEASUREMENT THROUGH ICE Merced River, Yosemite Valley. calif. Scioto River, Columbus, Ohio Scioto River. Dublin. Ohio Wisconsin River, Muscoda. Wis. OONTENTS Introduct1on •••••••••••••••••• ~ ••••••••••••••••••••••••• ••• 1 Construction cqllipmont •.•• " •••••••••••.•••••••••••••••••••• 4 .. Excavation •••••••••••• , .•• , •••••••••••••••••• ~.~ ••••••• ~.~ • 4 Blasting •••••••••••••• ~ •••••••••• , ••••••••••••• ~.~.~ •• 6 Concrete ••••••••••••••. .•• ~ ••••••••••••••••••• , ••• ~ •• ~.~ •• 7 Ccm811 t ................. ~ ••.•••••••• ~ •••••• ~ ••••• , •••••• 7 Fine aggregate •••••••••••••••• , ••••••••••••••••••••••• 7 Coarse aggrogate ••••••••••••••••• !' •••••••• !' •••••••••• ~ 7 ?report ions •••.• ~ • ~ .... ~ •• ~ .... .,." •. ~ •• , ••• ~. 0 •• ~. ~ ~ ~ • '•• 7 Quality of water ••••••••••••••••••• , ••••••• , •• ~, •••••• 8 Mixillg ••• ~ ••••••• '8 ••• ~ .................. , ••••••••• , •••• 8 Qua~tity of water -

Build a Plane That Cuts Smooth and Crisp Raised Panels With, Against Or Across the Grain – the Magic Is in the Spring and Skew

Fixed-width PanelBY WILLARD Raiser ANDERSON Build a plane that cuts smooth and crisp raised panels with, against or across the grain – the magic is in the spring and skew. anel-raising planes are used Mass., from 1790 to 1823 (Smith may to shape the raised panels in have apprenticed with Joseph Fuller doors, paneling and lids. The who was one of the most prolific of the profile has a fillet that defines early planemakers), and another similar Pthe field of the panel, a sloped bevel example that has no maker’s mark. to act as a frame for the field and a flat Both are single-iron planes with tongue that fits into the groove of the almost identical dimensions, profiles door or lid frame. and handles. They differ only in the I’ve studied panel-raising planes spring angles (the tilt of the plane off made circa the late 18th and early 19th vertical) and skew of the iron (which centuries, including one made by Aaron creates a slicing cut across the grain to Smith, who was active in Rehoboth, reduce tear-out). The bed angle of the Smith plane is 46º, and the iron is skewed at 32º. Combined, these improve the quality of cut without changing the tool’s cutting angle – which is what happens if you skew Gauges & guides. It’s best to make each of these gauges before you start your plane build. In the long run, they save you time and keep you on track. Shaping tools. The tools required to build this plane are few, but a couple of them – the firmer chisel and floats – are modified to fit this design. -

Fletcher Business Group Acquires Atlas Saw & Tool

FOR IMMEDIATE RELEASE Media Contact: Sarah Archambault • 917.923.9838 • [email protected] FLETCHER BUSINESS GROUP ACQUIRES ATLAS SAW & TOOL Global Solution Provider Expands Product Line and Services through Acquisition of Leading Provider of Saw Blades, Cutting Tools and Sharpening Services [East Berlin, CT – January 23, 2017] Today, Fletcher Business Group (FBG) – a leading provider of solution-driven technologies for a wide range of industries – including custom and OEM picture framing; sign and digital graphics; hardware; woodworking; and float and glass fabrication industries – is announcing the acquisition of Atlas Saw & Tool and Tem-Tech. With locations in Illinois, Florida and Arizona, Atlas provides high quality saw blades, cutting tools and sharpening services. Tem-Tech carries a high capacity saw line, along with repair/refurbish services for all saw types. Atlas Saw & Tool joins FBG’s roster of globally recognized brands as a wholly owned subsidiary and will continue the day-to-day operations of its key brands. Atlas serves a variety of markets including picture framing, cabinet making, flooring, millwork and the plastic industry. Using precise German CNC grinders and associated robotics, Atlas Saw sharpens blades and tools to OEM specifications and serves customers nationwide from its three regional tech centers. Atlas will continue to provide custom saw blade design services, fabrication and re-sharpening programs utilizing its premier selection of American and Japanese made core blades. The Tem-Tech brand offerings will remain, including the large capacity saw, CNC moulding profile template machine, saw service, repair and preventative maintenance programs. This will include service, refurbishment and parts support of Pistorius brand saws. -

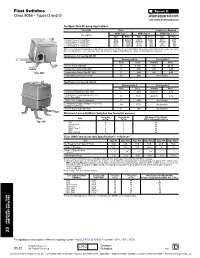

Float Switches Class 9036 – Types D and G

Float Switches Class 9036 – Types D and G For Open Tank Or Sump Applications Class 9036 2 Pole Single Lever Operated NEMA Type 1 NEMA Type 4 NEMA Type 7, 9 Description Type Price Type Price Type Price Contacts Close on Liquid Rise. DG2 $35.60 DW31 $236. DR31 $227. Contacts Open on Liquid Rise . DG2R 38.80 DW31R 239. DR31R 230. Contacts Close on Liquid Rise. GG2 68.00 GW1 397. GR1 388. Contacts Open on Liquid Rise . GG2R 68.00 GW1R 404. GR1R 397. Order universal mounting bracket and float accessory kits separately from Class 9049 section. Types GW and GR use center hole float. Devices with Form C use Centerhole float . All others use tapped at top float. See Page 18-8 for 9049 accessories. Modifications For Type DG, DW, DR Factory Installed Field Installed Form Price 9049 Kit Price Reverse Action (Type DG) R $3.30 A58 $3.30 Compensating Spring (Type DG) C 6.50 A19 6.50 Compensating Spring (Type DR, DW) C 6.50 A20 6.50 Type DG2 Comp. Spring and Reverse Action CR 9.80 Not Available Modifications For Type GG, GW, GR Factory Installed Field Installed Form Price 9049 Kit Price Compensating Spring for Type GG2 C 8.10 9049A13 8.10 Combination of Comp. Spring & Reverse Action (Type GG2) CR 17.70 9049A13 8.10 1 N.O.-1 N.C. Contact Configuration H 9.60 Not Available Combination of Comp. Spring & 1 N.O.-1 N. C. Contact for Type GG2 CH 17.70 Not Available Reverse Action (Type GR, GW) R 9.60 Not Available Maximum Forces At Which Switches Are Tested (in ounces) Type Force Up Force Down Will Support This Weight To Trip To Trip With Compensating Spring Type GG DG2 9 8 60 DG2 Form R 8 8 60 DW31 8 8 66 DW31 Form R 8 8 66 DR31 8 8 66 DR31 Form R 8 8 66 Class 9049 Float Accessory Specifications – In Ounces Item Type A6 Type A6S Type A6C Type A6CS Type A6A Type A6CA Net Buoyancya (in Water) 7" Float . -

Oil Mill Gazetteer OFFICIAL ORGAN of the NATIONAL OIL MILL SUPERINTENDENTS* ASSOCIATION and TRI-STATES COTTONSEED OIL MILL SUPERINTENDENTS* ASSOCIATION Vol

Oil Mill Gazetteer OFFICIAL ORGAN OF THE NATIONAL OIL MILL SUPERINTENDENTS* ASSOCIATION AND TRI-STATES COTTONSEED OIL MILL SUPERINTENDENTS* ASSOCIATION Vol. 48; No. 7 Wharton, Texas, January, 1944 Price 25 Cents Fo r t 'W o r t h r ; : = iiiiter ribs LATE LINTER RIBS can be furnished for linters with 106 or 141 saws. They Pare easier to install—less likely to break—spacing of saw slots is more accurate— make a more rigid gratefall—help prevent buckling of lower rib rail and can be installed more quickly. The ribs are made of 5-16" steel plate. They are formed to the proper shape on a large forming press. The slots are milled with gang cutters to insure accurate spacing and are then beveled or “relieved" on the under side, quite similar to individual ribs. Any plate section may be renewed. The finished plate is case hardened to the proper depth. r-OTHER FORT WORTH LINT ROOM EQUIPMENT * Pneumatic Lint Flue Systems Pneumatic Rock and Shale Removers * Lint Cleaning Beaters Fort Worth All-Metal Linters * Saw Filing and Gumming Machines Permanent Magnet Boards * Linter Saw s Mote and Tailings Beaters * Brushless Linter Devices Vertical Screw Elevators * Lint Condensers Parts to re-build and convert Linters to 141 Saw Machines A Complete Line of Power Transmission and Conveying Equipment SALES OFFICES—Fort Worth, P. O. Box 1038 . Memphis, P. O. Box 1499 . Atlanta, P. O. Box 1065 T orT W orIh ^MACHINERY CO. manufacturers o f h i g h -g r a d e o il m i l l e q u i p m e n t THERE'S MORE OIL, MARKET FLUCTUATIONS occur and you can not do very much about them. -

Service Letter 159, 13000 Scuff Plate Inst

WIPLINE FLOATS • SKIS • MODIFICATIONS • AIRCRAFT SALES SERVICE LETTER 159 AVIONICS • INTERIOR • MAINTENANCE • PAINT REFINISHING PAGE 1 of 6 REV: A SERVICE LETTER NUMBER 159 TITLE: 13000 Scuff Plate Inst. BY: C.Schlemmer AIRCRAFT MAKE/MODEL(S): FLOAT MODEL(S): NOTE(S): APP: J.Sortor Optional Compliance DATE: 01/16/15 De Havilland DHC-6 13000 S/L P/N 1008370 REV: A ECO-23996 FAA APPROVAL HAS BEEN OBTAINED FOR TECHNICAL DATA IN THIS PUBLICATION THAT AFFECTS STC OR TSO DESIGN COMPLIANCE EFFECTIVITY: This service letter applies to: de Havilland DHC-6 Twin Otter when equipped with Wipline model 13000 Amphibian and Seaplane Floats STC SA2CH. COMPLIANCE: Compliance with this service letter is optional. BACKGROUND: Wipaire has received a request from a customer to add a scuff plate to the outboard afterbody of the left float. COMPLIANCE METHOD: Install the parts included in this service letter in accordance with the instructions in the Technical Data section of this service letter. APPROX. SHOP HOURS: This service letter will take approximately 3 labor hours to complete. WARRANTY INFORMATION: This service letter does not include any warranty labor or parts. TECHNICAL DATA: Copies of this service letter, service kit, float manual, repair drawing, and float parts manual are available on www.wipaire.com. 1700 Henry Ave – Fleming Field (KSGS), South St. Paul, MN 55075 Ph: 651.451.1205 Fax: 651.457.7858 www.wipaire.com WIPLINE FLOATS • SKIS • MODIFICATIONS • AIRCRAFT SALES SERVICE LETTER 159 AVIONICS • INTERIOR • MAINTENANCE • PAINT REFINISHING PAGE 2 of 6 REV: A See figures below for details on installing the scuff plate See BOM below for the list of parts used when installing the scuff plate. -

Tridium's Sedona 1.2 Component Descriptions

Tridium’s Sedona 1.2 Component Descriptions Components are deployed in kits which are available from Tridium, Contemporary Controls and other members of the Sedona community. Kits without a company name are from Tridium. Kits with a company name and no product name are from a Sedona community member and these components can be used with other Sedona devices. Kits with both a company name and product name are hardware dependent thereby limiting portability. What follows are component descriptions of Tridium-release kits compliant with Sedona release 1.2.28. In prior releases by Tridium, Tridium put all the Sedona components into one kit called the Control kit. With this final release, Tridium organized these components into multiple kits with more meaningful kit names. This organizational structure has been maintained in this document with components listed by the newer kit names. It is recommended that these kits or components not be modified from their original form to ensure the portability of components and kits among members of the Sedona community. If changes or enhancements need to be made by a Sedona developer, the developer can use what currently exists, modify or enhance the component, but then save the result as a custom component using the developer’s name. The developer would then create a kit name that also includes the developer’s name making it clear it is a custom kit. When studying these components keep the following in mind. Boolean variables are assumed if there is a false/true state indication. Integers (32-bit signed integers) are shown as whole numbers while floats (32-bit floating point) are shown with a decimal point. -

Northeastern Loggers Handrook

./ NORTHEASTERN LOGGERS HANDROOK U. S. Deportment of Agricnitnre Hondbook No. 6 r L ii- ^ y ,^--i==â crk ■^ --> v-'/C'^ ¿'x'&So, Âfy % zr. j*' i-.nif.*- -^«L- V^ UNITED STATES DEPARTMENT OF AGRICULTURE AGRICULTURE HANDBOOK NO. 6 JANUARY 1951 NORTHEASTERN LOGGERS' HANDBOOK by FRED C. SIMMONS, logging specialist NORTHEASTERN FOREST EXPERIMENT STATION FOREST SERVICE UNITED STATES GOVERNMENT PRINTING OFFICE - - - WASHINGTON, D. C, 1951 For sale by the Superintendent of Documents, Washington, D. C. Price 75 cents Preface THOSE who want to be successful in any line of work or business must learn the tricks of the trade one way or another. For most occupations there is a wealth of published information that explains how the job can best be done without taking too many knocks in the hard school of experience. For logging, however, there has been no ade- quate source of information that could be understood and used by the man who actually does the work in the woods. This NORTHEASTERN LOGGERS' HANDBOOK brings to- gether what the young or inexperienced woodsman needs to know about the care and use of logging tools and about the best of the old and new devices and techniques for logging under the conditions existing in the northeastern part of the United States. Emphasis has been given to the matter of workers' safety because the accident rate in logging is much higher than it should be. Sections of the handbook have previously been circulated in a pre- liminary edition. Scores of suggestions have been made to the author by logging operators, equipment manufacturers, and professional forest- ers. -

Drill Pipe Float Valves ®

® ® Smart Solutions. Powerful Products. Drill Pipe Float Valves ® EXPERIENCE, DEDICATION and VISION Introducing Forum Energy Technologies – a global provider of manufactured technologies and applied products and services. We may be a new name to you but our equipment and employees have a long history of solving our customers’ challenges. FET brings together some of the most well-known brands in our industry with an extensive range of mission critical products and services. We are building a world class company to bring innovative solutions to our worldwide customers. With offices in the key oilfield distribution centers of the globe, Forum is well-positioned to supply our clients with the equipment and related services that improve safety and performance and lower operating costs. Forum’s products and services range from the underwater reservoir to the refinery, from the sea floor to the above ground transportation line. We pride ourselves on giving you a comprehensive offering of solutions to maximize your operations and improve your bottom line. Our customers are our partners and we work with them to solve their ever-changing challenges. ® Introduction FORUM is the original manufacturer of Baker Drill Pipe Float Valves. Committed to continuous improvement and production of quality products for optimum performance and reliability, Forum Drill Pipe Float Valves have become an industry standard with their superior engineering, quality, construction and dependability in service. FORUM manufactures a complete line of Float Valves, Repair Kits, and Puller Assemblies to accommodate a wide range of drilling situations and operating conditions, including H2S and Steam Service. These Drill Pipe Float Valves provide added blowout protection at the bottom of the drillstring, prevent flowback when joints are added, and keep cuttings out of the drillpipe to prevent bit plugging while making connections. -

Selection of Optimum Filtration Rates for Sand Filters John Leroy Cleasby Iowa State University

Iowa State University Capstones, Theses and Retrospective Theses and Dissertations Dissertations 1960 Selection of optimum filtration rates for sand filters John LeRoy Cleasby Iowa State University Follow this and additional works at: https://lib.dr.iastate.edu/rtd Part of the Civil and Environmental Engineering Commons Recommended Citation Cleasby, John LeRoy, "Selection of optimum filtration rates for sand filters " (1960). Retrospective Theses and Dissertations. 2815. https://lib.dr.iastate.edu/rtd/2815 This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact [email protected]. SELECTION OF OPTIMUM FILTRATION BATES FOB 3AKD FILTERS ty John Le Boy Classby A Dissertation Submitted to the Graduate Faculty in Partial Fulfillment of The Requirements for the Degree of DOCTOR OF PHILOSOPHY Major Subjects Sanitary Engineering Approved: Signature was redacted for privacy. In Charge of Major Work Signature was redacted for privacy. Signature was redacted for privacy. Iowa State University Of Science and Technology Ames, Iowa I960 il TABLE OF CONTENTS Page LIST OF ABBREVIATIONS vil I. INTRODUCTION 1 II. WORK OF OTHER INVESTIGATORS 4 A. Early Development of Rapid Sand Filters 4 B. Studies of High Rate Filtration 6 C. Summary of Status of High Rate Filtration 19 D. Studies of the Functioning of Sand Filters 20 III. OBJECTIVES AND SCOPE OF THIS STUDY 31 IV. PILOT PLANT APPARATUS 35 A. -

Online Trowel Fitting Guide the Wagman Online Fitting Guide Will Help You Easily See All of the Trowel Blades and Pans That Fit Your Machine

Online Trowel Fitting Guide The Wagman online fitting guide will help you easily see all of the trowel blades and pans that fit your machine. Choose the make and model of your equipment for a list of what fits your trowel. Visit www.WagmanMetal.com for the interactive fitting guide. 50 Years of Excellence Since 1963 Wagman Metal Products, Inc., has been a leading supplier of power trowel replacement blades and floating pans in the concrete industry. We want to thank our dealers and customers for their continued support, helping to make Wagman Metal Products successful. We are truly a family business that started when my grandfather George F. Wagman, Sr., and my father George F. Wagman, Jr., began production and distribution of a variety of blades to fit many brands of power trowels. Today, Wagman manufactures over 350 different blades to fit the trowels of over 40 companies. In 1980 I started working on our factory floor, performing a variety of jobs in order to learn all the aspects of the manufacturing process. My experience over the years helps ensure that all the products we manufacture meet my tough standards for quality and value. If it's got my name on it, you know you can count on it! Wagman's experience and innovation have helped pioneer the development of heavy-duty blades to cope with the stresses of the new generation of heavy riding trowels. More recently Wagman has perfected the design of the plastic trowel blade, engineered to provide burnish free finishing and unparalleled blade life. Be sure to check out our newest innovation, the Revolution Rotary System.