Pentium Processors Have Slightly Different Requirements to Enable and Disable Paging

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

Premiere/PCI II Baby-AT Board & Expandable Desktop

Premiere/PCI II Baby-AT Board & Expandable Desktop Technical Product Summary Version 2.0 December, 1994 Order Number 281626-002 ® Premiere/PCI II Technical Product Summary Table of Contents Introduction............................................................................................................................................ 3 Board Level Features ............................................................................................................................. 4 CPU Performance Upgrade Second Level Cache System Memory Expansion Slots Peripheral Component Interconnect (PCI) Chip Set SMC 37C665 Super I/O Controller Keyboard Interface Dallas DS12887 Real Time Clock, CMOS RAM And Battery System BIOS Connectors System Level Features............................................................................................................................ 10 Chassis Peripheral Bays Fan Expansion Slots Front and Back Panel Power Supply and Power Consumption Floppy Drive Speaker Chassis Color Appendix A - User-Installable Upgrades............................................................................................... 12 Appendix B - Jumpers........................................................................................................................... 13 Appendix C - Connectors ...................................................................................................................... 14 Appendix D - Memory Map ................................................................................................................. -

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS48, MCS51, 80X86 up To

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS-48, MCS-51, 80x86 up to 80386, 80860, 80960, SA-110 Intel 80486: 80486, 80486 overdrive Intel Pentium: Pentium, Pentium MMX, Pentium Overdrive, Mobile Pentium Intel Pentium II: Boxed Pentium II, Boxed Pentium Pro, Mobile Pentium II and Celeron modules Intel Pentium III: Pentium III markings, Mobile Pentium III and Celeron modules Intel modern CPUs: Pentium II, Pentium III, Pentium 4, Core Duo, Core Solo, Core 2 Duo, Core 2 Quad, Core 2 Extreme, Xeon, Pentium Dual Core, Celeron, Celeron D, Celeron Dual Core Intel 287 adapter Intel 3002 Intel 478-pin FC-PGA Thermal Sample Intel 80188 Intel 80486 Mech sample Intel 8080A Intel 80P23T-25 Intel A100 UM80536UC600512 Intel A110 UM80536UC800512 Intel A80186 Intel A80186-10 Intel A80188 Intel A80188-10 Intel A80286-10 Intel A80286-12 Intel A80286-8 Intel A80376-16 Intel A80376-20 Intel A80386-16 Intel A80386-20 Intel A80386-25 Intel A80386DX-16 Intel A80386DX-16 IV Intel A80386DX-20 Intel A80386DX-20 IV Intel A80386DX-25 Intel A80386DX-25 IV Intel A80386DX-33 IV Intel A80386DX16 Intel A80386EXI Intel A80387-16 Intel A80387-20 Intel A80387-20B Intel A80387-25 Intel A80387DX-16 (with logo) Intel A80387DX-16-33 Intel A80387DX-20 Intel A80387DX-25 Intel A80387DX-33 Intel A80486DX-33 Intel A80486DX-50 Intel A80486DX2-50 Intel A80486DX2-66 Intel A80486DX4-100 Intel A80486DX4-75 Intel A80486SX-16 Intel A80486SX-20 Intel A80486SX-25 Intel A80486SX-33 Intel A80486SX2-50 Intel A80487SX Intel A80860XP-40 Intel A80860XP-50 Intel A80860XR-25 Intel A80860XR-33 Intel -

Pentium® Processor Family Developer's Manual

D Pentium® Processor Family Developer’s Manual Volume 1: Pentium® Processors NOTE: The Pentium® Processor Family Developer’s Manual consists of three books: Pentium® Processors, Order Number 241428; the 82496/82497/82498 Cache Controller and 82491/82492/82493 Cache SRAM, Order Number 241429; and the Architecture and Programming Manual, Order Number 241430. Please refer to all three volumes when evaluating your design needs. 1995 PATENT NOTICE Through its investment in computer technology, Intel Corporation (Intel) has acquired numerous proprietary rights, including patents issued by the U.S. Patent and Trademark Office. Intel has patents covering the use or implementation of processors in combination with other products, e.g., certain computer systems. System and method patents or pending patents, of Intel and others, may apply to these systems. A separate license may be required for their use (see Intel Terms and Conditions for details). Specific Intel patents include U.S. patent 4,972,338. Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein. Intel retains the right to make changes to these specifications at any time, without notice. Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order. -

Premiere/PCI Baby-AT Board & Expandable Desktop

Premiere/PCI Baby-AT Board & Expandable Desktop Technical Product Summary Final Review Copy Version 2.0 March, 1994 Order Number 281604-002 ® Premiere/PCI Baby-AT Technical Product Summary · Page 2 Intel Corporation disclaims all warranties and liabilities for the use of this document and the information contained herein, and assumes no responsibility for any errors which may appear in this document. Intel makes no commitment to update the information contained herein, and may make changes at any time without notice. There are no express or implied licenses granted hereunder to any intellectual property rights of Intel Corporation or others to design or fabricate Intel integrated circuits or integrated circuits based on the information in this document. Contact your local sales office to obtain the latest specifications before placing your order. The following are trademarks of Intel Corporation and may only be used to identify Intel products: AboveÔ ICEä LANDeskÔ ActionMediaâ iCOMPä MCSâ DVIâ Indeoä NetPortÔ EtherExpressÔ Insight960™ NetportExpress™ ExCAÔ Intel287Ô OverDriveÔ FlashFileÔ Intel386Ô ParagonÔ i287Ô Intel387Ô PentiumÔ i386Ô Intel486Ô RapdiCADä i387Ô Intel487Ô SatisFAXtionâ i486Ô Intel Insideâ Solutions960™ i487Ô IntelDX2™ StorageExpressä i750â IntelDX4™ TokenExpressÔ i860ä iPSCâ i960â iRMX® The Indeo, OverDrive and Pentium logos are trademarks and the Intel and Intel Inside logos are registered trademarks of Intel Corporation. Intel Corporation and Intel’s FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products. MDS is an ordering code only and is not used as a product name or trademark. MDS is a trademark or registered trademark of its respective owner. Additional copies of Intel literature may be obtained from: Intel Corporation Literature Sales P.O. -

Pentium® Processor Family Developer's Manual

D Pentium® Processor Family Developer’s Manual 1997 12/19/96 9:12 AM Front.doc Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Pentium® processor may contain design defects or errors known as errata. Current characterized errata are available on request. MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. -

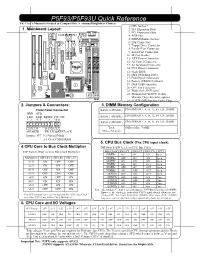

P5F93/P5F93U Quick Reference the User’S Manual Is Located at Compact Disc’S \Manual\English Or Chinese 1: CPU Socket 7 1

P5F93/P5F93U Quick Reference The User’s Manual is located at Compact Disc’s \manual\English or Chinese 1: CPU Socket 7 1. Mainboard Layout: 2: ISA Expansion Slots 3: PCI Expansion Slots 3 i 1 1 13 4 COM1 COM2 14 L 5 4: AGP Slot 1 9 19 A M 1 1 1 5: DIMM Module Sockets 1 12 1 10 6: IDE Connectors 3 IR 7 8 11 7: Floppy Drive Connector L F P P P C C C P 8: Parallel Port Connector 6 D I I I I I T D 3 2 1 2 D D 9: Serial Port Connectors E E 5 JP11 B B B 10: IR Port Header 21 1 2 A A A 11: ATX Power Connector 1 4 N N N 12: AT Power Connector 2 4 5 1 JP7 M K K K 13: AT Keyboard Connector i L A 14: PS/2 Mouse Connector 2 1 0 15: Flash BIOS S I 16: Dual Switching Power 18 M S S I I 15 I 17: Front Panel Connectors M S S o M A c A 1 k 18: Battery (CR2032 Lithium) M e 2 1 S t 2 W P 7 I 19: Dual USB Connector 6 1 D 1 5 4 3 1 20: CPU Fan Connector 2 N 1 22 JP7 JP2 O 17 S 16 D D 21: Wake On LAN Header W I I M M P I 3 22: Winbond 83781D PC Health D 2 23 2 N 20 1 O M M Monitor Chip (Assemble option) 2 1 23: 512KB/1MB Pipeline Cache Chip 2. -

Pentium® Processor Specification Update

Pentium® Processor Specification Update Release Date: January 1999 Order Number 242480-041 The Pentium® processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update. 24248041.doc INTEL CONFIDENTIAL — PRELIMINARY Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Pentium® processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel’s website at http://www.intel.com. -

PENTIUM® PROCESSOR 75 90 100 120 133 150 166 200 Max

E PENTIUM® PROCESSOR 75 90 100 120 133 150 166 200 Max. Operating Frequency MHz MHz MHz MHz MHz MHz MHz MHz iCOMP® Index 2.0 Rating 67 81 90 100 111 114 127 142 Note: Contact Intel Corporation for more information about iCOMP®Index 2.0 ratings. n Compatible with Large Software Base n Multi-Processor Support MS-DOS*, Windows*, OS/2*, UNIX* Multiprocessor Instructions Support for Second Level Cache n 32-Bit CPU with 64-Bit Data Bus n On-Chip Local APIC Controller n Superscalar Architecture MP Interrupt Management Two Pipelined Integer Units Are Capable 8259 Compatible of 2 Instructions/Clock Pipe-lined Floating Point Unit n Upgradable with a Pentium® OverDrive® Processor n Separate Code and Data Caches 8-Kbyte Code, 8-Kbyte Write Back Data n Power Management Features MESI Cache Protocol System Management Mode Clock Control n Advanced Design Features Branch Prediction n Fractional Bus Operation Virtual Mode Extensions 200-MHz Core/66-MHz Bus 166-MHz Core/66-MHz Bus n 3.3V BiCMOS Silicon Technology 150-MHz Core/60-MHz Bus n 4-Mbyte Pages for Increased TLB Hit Rate 133-MHz Core/66-MHz Bus n IEEE 1149.1 Boundary Scan 120-MHz Core/60-MHz Bus 100-MHz Core/66-MHz Bus n Dual Processing Configuration 100-MHz Core/50-MHz Bus n Functional Redundancy Checking Support 90-MHz Core/60-MHz Bus 75-MHz Core/50-MHz Bus n Internal Error Detection Features The Pentium® processor 75/90/100/120/133/150/166/200 extends the Pentium processor family, providing performance needed for mainstream desktop applications as well as for workstations and servers. -

P5 (Microarchitecture)

P5 (microarchitecture) The Intel P5 Pentium family Produced From 1993 to 1999 Common manufacturer(s) • Intel Max. CPU clock rate 60 MHz to 300 MHz FSB speeds 50 MHz to 66 MHz Min. feature size 0.8pm to 0.25pm Instruction set x86 Socket(s) • Socket 4, Socket 5, Socket 7 Core name(s) P5. P54C, P54CS, P55C, Tillamook The original Pentium microprocessor was introduced on March 22, 1993.^^ Its microarchitecture, deemed P5, was Intel's fifth-generation and first superscalar x86 microarchitecture. As a direct extension of the 80486 architecture, it included dual integer pipelines, a faster FPU, wider data bus, separate code and data caches and features for further reduced address calculation latency. In 1996, the Pentium with MMX Technology (often simply referred to as Pentium MMX) was introduced with the same basic microarchitecture complemented with an MMX instruction set, larger caches, and some other enhancements. The P5 Pentium competitors included the Motorola 68060 and the PowerPC 601 as well as the SPARC, MIPS, and Alpha microprocessor families, most of which also used a superscalar in-order dual instruction pipeline configuration at some time. Intel's Larrabee multicore architecture project uses a processor core derived from a P5 core (P54C), augmented by multithreading, 64-bit instructions, and a 16-wide vector processing unit. T31 Intel's low-powered Bonnell [4i microarchitecture employed in Atom processor cores also uses an in-order dual pipeline similar to P5. Development The P5 microarchitecture was designed by the same Santa Clara team which designed the 386 and 486.^ Design work started in 1989;^ the team decided to use a superscalar architecture, with on-chip cache, floating-point, and branch prediction. -

Intel® Processor Identification and the CPUID Instruction

AP-485 APPLICATION NOTE Intel® Processor Identification and the CPUID Instruction May 2002 Order Number: 241618-021 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Intel processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641 or call 1-800-879-4683 or visit Intel’s website at http://www.intel.com/ Copyright © Intel Corporation 1993-2002. -

Pentium® Processor with Mmx™ Technology

E PENTIUM® PROCESSOR WITH MMX™ TECHNOLOGY Maximum Operating Frequency 166 MHz 200 MHz 233 MHz iCOMP® Index 2.0 Rating 160 182 203 NOTE: Contact Intel Corporation for more information about iCOMP® Index 2.0 ratings. n Support for MMX™ Technology n Enhanced CMOS Silicon Technology n Compatible with Large Software Base n 4-Mbyte Pages for Increased TLB Hit MS-DOS*, Windows*, OS/2*, UNIX* Rate n 32-Bit Processor with 64-Bit Data Bus n IEEE 1149.1 Boundary Scan n Superscalar Architecture n Dual Processing Configuration Enhanced Pipelines n Internal Error Detection Features Two Pipelined Integer Units Capable of Two Instructions per n Multi-Processor Support Clock Multiprocessor Instructions Pipelined MMX Unit Support for Second Level Cache Pipelined Floating-Point Unit n On-Chip Local APIC Controller n Separate Code and Data Caches MP Interrupt Management 16-Kbyte Code, 16-Kbyte Write 8259 Compatible Back Data n Power Management Features MESI Cache Protocol System Management Mode n Advanced Design Features Clock Control Deeper Write Buffers n Fractional Bus Operation Enhanced Branch Prediction 233 MHz Core/66 MHz Bus Feature 200 MHz Core/66 MHz Bus Virtual Mode Extensions 166 MHz Core/66 MHz Bus The Pentium® processor with MMX™ technology extends the Pentium processor family, providing performance needed for mainstream desktop applications as well as for workstations. The Pentium processor with MMX technology is compatible with the entire installed base of applications for MS-DOS*, Windows*, OS/2* and UNIX*. The Pentium processor with MMX technology is the first microprocessor to support Intel MMX technology. Furthermore, the Pentium processor with MMX technology superscalar architecture can execute two instructions per clock cycle.