Pentium® Processor Family Developer's Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pentium Processors Have Slightly Different Requirements to Enable and Disable Paging

D Pentium® Processor Family Developer’s Manual Volume 1: Pentium® Processors NOTE: The Pentium® Processor Family Developer’s Manual consists of three books: Pentium® Processors, Order Number 241428; the 82496/82497/82498 Cache Controller and 82491/82492/82493 Cache SRAM, Order Number 241429; and the Architecture and Programming Manual, Order Number 241430. Please refer to all three volumes when evaluating your design needs. 1995 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. The Pentium® processor may contain design defects or errors known as errata. Current characterized errata are available on request. *Third-party brands and names are the property of their respective owners. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. Box 7641 Mt. -

PCSA Oct 2001

Understanding CPU Upgrades In theory, one way to t seems that every time a new software product is released the system require- ments are increased - everything from the hard drive capacity and CPU speed increase the performance of a Ito the required RAM. One of the apparently obvious ways to gain a speed PC with little effort is to increase is by upgrading the CPU. But such an upgrade isn’t always cost effective and in some cases simply increasing the available RAM can help considerably to upgrade the CPU. Surely it boost the apparent speed of the PC. Sometimes though the best (and maybe only) option is to upgrade the CPU, although this can be a more involved process than it can’t be that difficult? might at first seem due to socket/motherboard incompatibilities, differing CPU and Actually there’s lots to think RAM speed requirements, cooling problems and inevitably assorted knock-on effects causing the upgrade to be anything but cost effective. Also, it is worth about. remembering that just because the replacement CPU has, for example, double the clock rate of the old unit doesn’t necessarily mean that the new one will increase the By Phil Morris processing performance of the PC in question by anything like 100%. Technical Writer This article looks at some of the options for upgrading the CPUs in existing systems. It is extremely unlikely that recent processors like AMD’s Duron (and forthcoming Hammer) and Intel’s Pentium 4 and Itanium will require upgrading for some time, so I will omit those in the context of this article. -

VX97 User's Manual ASUS CONTACT INFORMATION Asustek COMPUTER INC

R VX97 Pentium Motherboard USER'S MANUAL USER'S NOTICE No part of this manual, including the products and softwares described in it, may be repro- duced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup pur- poses, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). ASUS PROVIDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PAR- TICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDEN- TAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSI- NESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. Products and corporate names appearing in this manual may or may not be registered trade- marks or copyrights of their respective companies, and are used only for identification or explanation and to the owners’ benefit, without intent to infringe. • Intel, LANDesk, and Pentium are registered trademarks of Intel Corporation. • IBM and OS/2 are registered trademarks of International Business Machines. • Symbios is a registered trademark of Symbios Logic Corporation. • Windows and MS-DOS are registered trademarks of Microsoft Corporation. • Sound Blaster AWE32 and SB16 are trademarks of Creative Technology Ltd. • Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. -

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

Premiere/PCI II Baby-AT Board & Expandable Desktop

Premiere/PCI II Baby-AT Board & Expandable Desktop Technical Product Summary Version 2.0 December, 1994 Order Number 281626-002 ® Premiere/PCI II Technical Product Summary Table of Contents Introduction............................................................................................................................................ 3 Board Level Features ............................................................................................................................. 4 CPU Performance Upgrade Second Level Cache System Memory Expansion Slots Peripheral Component Interconnect (PCI) Chip Set SMC 37C665 Super I/O Controller Keyboard Interface Dallas DS12887 Real Time Clock, CMOS RAM And Battery System BIOS Connectors System Level Features............................................................................................................................ 10 Chassis Peripheral Bays Fan Expansion Slots Front and Back Panel Power Supply and Power Consumption Floppy Drive Speaker Chassis Color Appendix A - User-Installable Upgrades............................................................................................... 12 Appendix B - Jumpers........................................................................................................................... 13 Appendix C - Connectors ...................................................................................................................... 14 Appendix D - Memory Map ................................................................................................................. -

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS48, MCS51, 80X86 up To

Intel: 3002, 4004, 4040, 8008, 8080, 8085, MCS-48, MCS-51, 80x86 up to 80386, 80860, 80960, SA-110 Intel 80486: 80486, 80486 overdrive Intel Pentium: Pentium, Pentium MMX, Pentium Overdrive, Mobile Pentium Intel Pentium II: Boxed Pentium II, Boxed Pentium Pro, Mobile Pentium II and Celeron modules Intel Pentium III: Pentium III markings, Mobile Pentium III and Celeron modules Intel modern CPUs: Pentium II, Pentium III, Pentium 4, Core Duo, Core Solo, Core 2 Duo, Core 2 Quad, Core 2 Extreme, Xeon, Pentium Dual Core, Celeron, Celeron D, Celeron Dual Core Intel 287 adapter Intel 3002 Intel 478-pin FC-PGA Thermal Sample Intel 80188 Intel 80486 Mech sample Intel 8080A Intel 80P23T-25 Intel A100 UM80536UC600512 Intel A110 UM80536UC800512 Intel A80186 Intel A80186-10 Intel A80188 Intel A80188-10 Intel A80286-10 Intel A80286-12 Intel A80286-8 Intel A80376-16 Intel A80376-20 Intel A80386-16 Intel A80386-20 Intel A80386-25 Intel A80386DX-16 Intel A80386DX-16 IV Intel A80386DX-20 Intel A80386DX-20 IV Intel A80386DX-25 Intel A80386DX-25 IV Intel A80386DX-33 IV Intel A80386DX16 Intel A80386EXI Intel A80387-16 Intel A80387-20 Intel A80387-20B Intel A80387-25 Intel A80387DX-16 (with logo) Intel A80387DX-16-33 Intel A80387DX-20 Intel A80387DX-25 Intel A80387DX-33 Intel A80486DX-33 Intel A80486DX-50 Intel A80486DX2-50 Intel A80486DX2-66 Intel A80486DX4-100 Intel A80486DX4-75 Intel A80486SX-16 Intel A80486SX-20 Intel A80486SX-25 Intel A80486SX-33 Intel A80486SX2-50 Intel A80487SX Intel A80860XP-40 Intel A80860XP-50 Intel A80860XR-25 Intel A80860XR-33 Intel -

AX34-U Hardware

Overview AX34-U Online Manual Installation AX34-U Hardware Drivers & Utilities BIOS Setup AWARD AWARD Glossary DOC. NO.: AX34U-OL-E0108A Troubleshooting & Technical Support Technical 1 AX34-U Online Manual What’s in this manual AX34-U .............................................................................................................................................1 What’s in this manual ......................................................................................................................................................2 You Must Notice ..............................................................................................................................................................8 Before You Start ..............................................................................................................................................................9 Overview .......................................................................................................................................................................10 Feature Highlight ...........................................................................................................................................................11 Quick Installation Procedure..........................................................................................................................................14 Motherboard Map ..........................................................................................................................................................15 -

Premiere/PCI Baby-AT Board & Expandable Desktop

Premiere/PCI Baby-AT Board & Expandable Desktop Technical Product Summary Final Review Copy Version 2.0 March, 1994 Order Number 281604-002 ® Premiere/PCI Baby-AT Technical Product Summary · Page 2 Intel Corporation disclaims all warranties and liabilities for the use of this document and the information contained herein, and assumes no responsibility for any errors which may appear in this document. Intel makes no commitment to update the information contained herein, and may make changes at any time without notice. There are no express or implied licenses granted hereunder to any intellectual property rights of Intel Corporation or others to design or fabricate Intel integrated circuits or integrated circuits based on the information in this document. Contact your local sales office to obtain the latest specifications before placing your order. The following are trademarks of Intel Corporation and may only be used to identify Intel products: AboveÔ ICEä LANDeskÔ ActionMediaâ iCOMPä MCSâ DVIâ Indeoä NetPortÔ EtherExpressÔ Insight960™ NetportExpress™ ExCAÔ Intel287Ô OverDriveÔ FlashFileÔ Intel386Ô ParagonÔ i287Ô Intel387Ô PentiumÔ i386Ô Intel486Ô RapdiCADä i387Ô Intel487Ô SatisFAXtionâ i486Ô Intel Insideâ Solutions960™ i487Ô IntelDX2™ StorageExpressä i750â IntelDX4™ TokenExpressÔ i860ä iPSCâ i960â iRMX® The Indeo, OverDrive and Pentium logos are trademarks and the Intel and Intel Inside logos are registered trademarks of Intel Corporation. Intel Corporation and Intel’s FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products. MDS is an ordering code only and is not used as a product name or trademark. MDS is a trademark or registered trademark of its respective owner. Additional copies of Intel literature may be obtained from: Intel Corporation Literature Sales P.O. -

Pentium® Processor Family Developer's Manual

D Pentium® Processor Family Developer’s Manual 1997 12/19/96 9:12 AM Front.doc Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Pentium® processor may contain design defects or errors known as errata. Current characterized errata are available on request. MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. -

Evolution of the Pentium

Chapter 7B – The Evolution of the Intel Pentium This chapter attempts to trace the evolution of the modern Intel Pentium from the earliest CPU chip, the Intel 4004. The real evolution begins with the Intel 8080, which is an 8–bit design having features that permeate the entire line. Our discussion focuses on three organizations. IA–16 The 16–bit architecture found in the Intel 8086 and Intel 80286. IA–32 The 32–bit architecture found in the Intel 80386, Intel 80486, and most variants of the Pentium design. IA–64 The 64–bit architecture found in some high–end later model Pentiums. The IA–32 has evolved from an early 4–bit design (the Intel 4004) that was first announced in November 1971. At that time, memory came in chips no larger than 64 kilobits (8 KB) and cost about $1,600 per megabyte. Before moving on with the timeline, it is worth recalling the early history of Intel. Here, we quote extensively from Tanenbaum [R002]. “In 1968, Robert Noyce, inventor of the silicon integrated circuit, Gordon Moore, of Moore’s law fame, and Arthur Rock, a San Francisco venture capitalist, formed the Intel Corporation to make memory chips. In the first year of operation, Intel sold only $3,000 worth of chips, but business has picked up since then.” “In September 1969, a Japanese company, Busicom, approached Intel with a request for it to manufacture twelve custom chips for a proposed electronic calculator. The Intel engineer assigned to this project, Ted Hoff, looked at the plan and realized that he could put a 4–bit general–purpose CPU on a single chip that would do the same thing and be simpler and cheaper as well. -

Technical Reference Guide HP Compaq Dc7800 Series Business Desktop Computers

Technical Reference Guide HP Compaq dc7800 Series Business Desktop Computers Document Part Number: 461444-001 October 2007 This document provides information on the design, architecture, function, and capabilities of the HP Compaq dc7800 Series Business Desktop Computers. This information may be used by engineers, technicians, administrators, or anyone needing detailed information on the products covered. © Copyright 2007 Hewlett-Packard Development Company, L.P. The information contained herein is subject to change without notice. Microsoft, MS-DOS, Windows, and Windows NT are trademarks of Microsoft Corporation in the U.S. and other countries. Intel, Intel Core 2 Duo, Intel Core 2 Quad, Pentium Dual-Core, Intel Inside, and Celeron are trademarks of Intel Corporation in the U.S. and other countries. Adobe, Acrobat, and Acrobat Reader are trademarks or registered trademarks of Adobe Systems Incorporated. The only warranties for HP products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. This document contains proprietary information that is protected by copyright. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company. Technical Reference Guide HP Compaq dc7800 Series Business Desktop Computers First Edition (October 2007) Document Part Number: 461444-001 Contents 1Introduction 1.1 About this Guide . 1–1 1.1.1 Online Viewing . 1–1 1.1.2 Hardcopy . 1–1 1.2 Additional Information Sources . 1–1 1.3 Model Numbering Convention . -

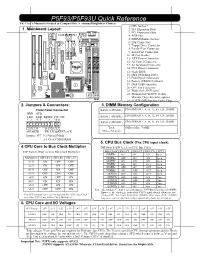

P5F93/P5F93U Quick Reference the User’S Manual Is Located at Compact Disc’S \Manual\English Or Chinese 1: CPU Socket 7 1

P5F93/P5F93U Quick Reference The User’s Manual is located at Compact Disc’s \manual\English or Chinese 1: CPU Socket 7 1. Mainboard Layout: 2: ISA Expansion Slots 3: PCI Expansion Slots 3 i 1 1 13 4 COM1 COM2 14 L 5 4: AGP Slot 1 9 19 A M 1 1 1 5: DIMM Module Sockets 1 12 1 10 6: IDE Connectors 3 IR 7 8 11 7: Floppy Drive Connector L F P P P C C C P 8: Parallel Port Connector 6 D I I I I I T D 3 2 1 2 D D 9: Serial Port Connectors E E 5 JP11 B B B 10: IR Port Header 21 1 2 A A A 11: ATX Power Connector 1 4 N N N 12: AT Power Connector 2 4 5 1 JP7 M K K K 13: AT Keyboard Connector i L A 14: PS/2 Mouse Connector 2 1 0 15: Flash BIOS S I 16: Dual Switching Power 18 M S S I I 15 I 17: Front Panel Connectors M S S o M A c A 1 k 18: Battery (CR2032 Lithium) M e 2 1 S t 2 W P 7 I 19: Dual USB Connector 6 1 D 1 5 4 3 1 20: CPU Fan Connector 2 N 1 22 JP7 JP2 O 17 S 16 D D 21: Wake On LAN Header W I I M M P I 3 22: Winbond 83781D PC Health D 2 23 2 N 20 1 O M M Monitor Chip (Assemble option) 2 1 23: 512KB/1MB Pipeline Cache Chip 2.