NEON Technology Introduction

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Interplay of Compile-Time and Run-Time Options for Performance Prediction Luc Lesoil, Mathieu Acher, Xhevahire Tërnava, Arnaud Blouin, Jean-Marc Jézéquel

The Interplay of Compile-time and Run-time Options for Performance Prediction Luc Lesoil, Mathieu Acher, Xhevahire Tërnava, Arnaud Blouin, Jean-Marc Jézéquel To cite this version: Luc Lesoil, Mathieu Acher, Xhevahire Tërnava, Arnaud Blouin, Jean-Marc Jézéquel. The Interplay of Compile-time and Run-time Options for Performance Prediction. SPLC 2021 - 25th ACM Inter- national Systems and Software Product Line Conference - Volume A, Sep 2021, Leicester, United Kingdom. pp.1-12, 10.1145/3461001.3471149. hal-03286127 HAL Id: hal-03286127 https://hal.archives-ouvertes.fr/hal-03286127 Submitted on 15 Jul 2021 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. The Interplay of Compile-time and Run-time Options for Performance Prediction Luc Lesoil, Mathieu Acher, Xhevahire Tërnava, Arnaud Blouin, Jean-Marc Jézéquel Univ Rennes, INSA Rennes, CNRS, Inria, IRISA Rennes, France [email protected] ABSTRACT Both compile-time and run-time options can be configured to reach Many software projects are configurable through compile-time op- specific functional and performance goals. tions (e.g., using ./configure) and also through run-time options (e.g., Existing studies consider either compile-time or run-time op- command-line parameters, fed to the software at execution time). -

Making Speech Recognition Work on the Web Christopher J. Varenhorst

Making Speech Recognition Work on the Web by Christopher J. Varenhorst Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Masters of Engineering in Computer Science and Engineering at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY May 2011 c Massachusetts Institute of Technology 2011. All rights reserved. Author.................................................................... Department of Electrical Engineering and Computer Science May 20, 2011 Certified by . James R. Glass Principal Research Scientist Thesis Supervisor Certified by . Scott Cyphers Research Scientist Thesis Supervisor Accepted by . Christopher J. Terman Chairman, Department Committee on Graduate Students Making Speech Recognition Work on the Web by Christopher J. Varenhorst Submitted to the Department of Electrical Engineering and Computer Science on May 20, 2011, in partial fulfillment of the requirements for the degree of Masters of Engineering in Computer Science and Engineering Abstract We present an improved Audio Controller for Web-Accessible Multimodal Interface toolkit { a system that provides a simple way for developers to add speech recognition to web pages. Our improved system offers increased usability and performance for users and greater flexibility for developers. Tests performed showed a %36 increase in recognition response time in the best possible networking conditions. Preliminary tests shows a markedly improved users experience. The new Wowza platform also provides a means of upgrading other Audio Controllers easily. Thesis Supervisor: James R. Glass Title: Principal Research Scientist Thesis Supervisor: Scott Cyphers Title: Research Scientist 2 Contents 1 Introduction and Background 7 1.1 WAMI - Web Accessible Multimodal Toolkit . 8 1.1.1 Existing Java applet . 11 1.2 SALT . -

Screen Capture Tools to Record Online Tutorials This Document Is Made to Explain How to Use Ffmpeg and Quicktime to Record Mini Tutorials on Your Own Computer

Screen capture tools to record online tutorials This document is made to explain how to use ffmpeg and QuickTime to record mini tutorials on your own computer. FFmpeg is a cross-platform tool available for Windows, Linux and Mac. Installation and use process depends on your operating system. This info is taken from (Bellard 2016). Quicktime Player is natively installed on most of Mac computers. This tutorial focuses on Linux and Mac. Table of content 1. Introduction.......................................................................................................................................1 2. Linux.................................................................................................................................................1 2.1. FFmpeg......................................................................................................................................1 2.1.1. installation for Linux..........................................................................................................1 2.1.1.1. Add necessary components........................................................................................1 2.1.2. Screen recording with FFmpeg..........................................................................................2 2.1.2.1. List devices to know which one to record..................................................................2 2.1.2.2. Record screen and audio from your computer...........................................................3 2.2. Kazam........................................................................................................................................4 -

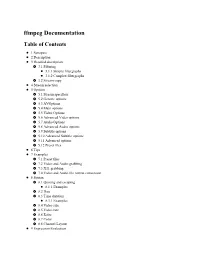

Ffmpeg Documentation Table of Contents

ffmpeg Documentation Table of Contents 1 Synopsis 2 Description 3 Detailed description 3.1 Filtering 3.1.1 Simple filtergraphs 3.1.2 Complex filtergraphs 3.2 Stream copy 4 Stream selection 5 Options 5.1 Stream specifiers 5.2 Generic options 5.3 AVOptions 5.4 Main options 5.5 Video Options 5.6 Advanced Video options 5.7 Audio Options 5.8 Advanced Audio options 5.9 Subtitle options 5.10 Advanced Subtitle options 5.11 Advanced options 5.12 Preset files 6 Tips 7 Examples 7.1 Preset files 7.2 Video and Audio grabbing 7.3 X11 grabbing 7.4 Video and Audio file format conversion 8 Syntax 8.1 Quoting and escaping 8.1.1 Examples 8.2 Date 8.3 Time duration 8.3.1 Examples 8.4 Video size 8.5 Video rate 8.6 Ratio 8.7 Color 8.8 Channel Layout 9 Expression Evaluation 10 OpenCL Options 11 Codec Options 12 Decoders 13 Video Decoders 13.1 rawvideo 13.1.1 Options 14 Audio Decoders 14.1 ac3 14.1.1 AC-3 Decoder Options 14.2 ffwavesynth 14.3 libcelt 14.4 libgsm 14.5 libilbc 14.5.1 Options 14.6 libopencore-amrnb 14.7 libopencore-amrwb 14.8 libopus 15 Subtitles Decoders 15.1 dvdsub 15.1.1 Options 15.2 libzvbi-teletext 15.2.1 Options 16 Encoders 17 Audio Encoders 17.1 aac 17.1.1 Options 17.2 ac3 and ac3_fixed 17.2.1 AC-3 Metadata 17.2.1.1 Metadata Control Options 17.2.1.2 Downmix Levels 17.2.1.3 Audio Production Information 17.2.1.4 Other Metadata Options 17.2.2 Extended Bitstream Information 17.2.2.1 Extended Bitstream Information - Part 1 17.2.2.2 Extended Bitstream Information - Part 2 17.2.3 Other AC-3 Encoding Options 17.2.4 Floating-Point-Only AC-3 Encoding -

![Arxiv:2007.15943V1 [Cs.SE] 31 Jul 2020](https://docslib.b-cdn.net/cover/3194/arxiv-2007-15943v1-cs-se-31-jul-2020-533194.webp)

Arxiv:2007.15943V1 [Cs.SE] 31 Jul 2020

MUZZ: Thread-aware Grey-box Fuzzing for Effective Bug Hunting in Multithreaded Programs Hongxu Chen§† Shengjian Guo‡ Yinxing Xue§∗ Yulei Sui¶ Cen Zhang† Yuekang Li† Haijun Wang# Yang Liu† †Nanyang Technological University ‡Baidu Security ¶University of Technology Sydney §University of Science and Technology of China #Ant Financial Services Group Abstract software performance. A typical computing paradigm of mul- tithreaded programs is to accept a set of inputs, distribute Grey-box fuzz testing has revealed thousands of vulner- computing jobs to threads, and orchestrate their progress ac- abilities in real-world software owing to its lightweight cordingly. Compared to sequential programs, however, multi- instrumentation, fast coverage feedback, and dynamic adjust- threaded programs are more prone to severe software faults. ing strategies. However, directly applying grey-box fuzzing On the one hand, the non-deterministic thread-interleavings to input-dependent multithreaded programs can be extremely give rise to concurrency-bugs like data-races, deadlocks, inefficient. In practice, multithreading-relevant bugs are usu- etc [32]. These bugs may cause the program to end up with ab- ally buried in the sophisticated program flows. Meanwhile, normal results or unexpected hangs. On the other hand, bugs existing grey-box fuzzing techniques do not stress thread- that appear under specific inputs and interleavings may lead interleavings that affect execution states in multithreaded pro- to concurrency-vulnerabilities [5, 30], resulting in memory grams. Therefore, mainstream grey-box fuzzers cannot ade- corruptions, information leakage, etc. quately test problematic segments in multithreaded software, although they might obtain high code coverage statistics. There exist a line of works on detecting bugs and vulner- To this end, we propose MUZZ, a new grey-box fuzzing abilities in multithreaded programs. -

Efficient Multi-Codec Support for OTT Services: HEVC/H.265 And/Or AV1?

Efficient Multi-Codec Support for OTT Services: HEVC/H.265 and/or AV1? Christian Timmerer†,‡, Martin Smole‡, and Christopher Mueller‡ ‡Bitmovin Inc., †Alpen-Adria-Universität San Francisco, CA, USA and Klagenfurt, Austria, EU ‡{firstname.lastname}@bitmovin.com, †{firstname.lastname}@itec.aau.at Abstract – The success of HTTP adaptive streaming is un- multiple versions (e.g., different resolutions and bitrates) and disputed and technical standards begin to converge to com- each version is divided into predefined pieces of a few sec- mon formats reducing market fragmentation. However, other onds (typically 2-10s). A client first receives a manifest de- obstacles appear in form of multiple video codecs to be sup- scribing the available content on a server, and then, the client ported in the future, which calls for an efficient multi-codec requests pieces based on its context (e.g., observed available support for over-the-top services. In this paper, we review the bandwidth, buffer status, decoding capabilities). Thus, it is state of the art of HTTP adaptive streaming formats with re- able to adapt the media presentation in a dynamic, adaptive spect to new services and video codecs from a deployment way. perspective. Our findings reveal that multi-codec support is The existing different formats use slightly different ter- inevitable for a successful deployment of today's and future minology. Adopting DASH terminology, the versions are re- services and applications. ferred to as representations and pieces are called segments, which we will use henceforth. The major differences between INTRODUCTION these formats are shown in Table 1. We note a strong differ- entiation in the manifest format and it is expected that both Today's over-the-top (OTT) services account for more than MPEG's media presentation description (MPD) and HLS's 70 percent of the internet traffic and this number is expected playlist (m3u8) will coexist at least for some time. -

University of Texas at Arlington Dissertation Template

LOW COMPLEXITY ENCODER USING MACHINE LEARNING by THEJASWINI PURUSHOTHAM Presented to the Faculty of the Graduate School of The University of Texas at Arlington in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE IN ELECTRICAL ENGINEERING THE UNIVERSITY OF TEXAS AT ARLINGTON December 2010 Copyright © by Thejaswini Purushotham 2010 All Rights Reserved ACKNOWLEDGEMENTS Multitudes of pixels come together to form a lovely portrait. Similarly, the fruition of a thesis happens because of the encouragement and guidance of numerous people. Thus, I would like to take this opportunity to thank everyone who invested their precious time on me in the last two years. In the fall of 2008, I walked into the room of Dr.K.R. Rao with the hopes of learning from the master of video coding. Though we were total strangers, he immediately put me at ease by creating a very positive working atmosphere which entails my sincere appreciation. His mentoring has undoubtedly had a profound impact on me. I am greatly indebted to him. I am deeply grateful to Dr. Dongil Han for always being available in the lab and providing me with continued financial support and technical advice. I would like to thank the other members of my advisory committee Dr. W. Alan Davis and Dr. Jonathan Bredow for reviewing this thesis document and offering insightful comments. My sincere thanks to Pragnesh and Suchethan. The love, affection and encouragement of Bhumika, Bhavana, Gunpreet, Thara, Srikanth and all my friends who kept me going through the trying times of my Masters. Finally, my sincere gratitude and love goes out to my mom Ms. -

User Manual 19HFL5014W Contents

User Manual 19HFL5014W Contents 1 TV Tour 3 13 Help and Support 119 1.1 Professional Mode 3 13.1 Troubleshooting 119 13.2 Online Help 120 2 Setting Up 4 13.3 Support and Repair 120 2.1 Read Safety 4 2.2 TV Stand and Wall Mounting 4 14 Safety and Care 122 2.3 Tips on Placement 4 14.1 Safety 122 2.4 Power Cable 4 14.2 Screen Care 123 2.5 Antenna Cable 4 14.3 Radiation Exposure Statement 123 3 Arm mounting 6 15 Terms of Use 124 3.1 Handle 6 15.1 Terms of Use - TV 124 3.2 Arm mounting 6 16 Copyrights 125 4 Keys on TV 7 16.1 HDMI 125 16.2 Dolby Audio 125 5 Switching On and Off 8 16.3 DTS-HD (italics) 125 5.1 On or Standby 8 16.4 Wi-Fi Alliance 125 16.5 Kensington 125 6 Specifications 9 16.6 Other Trademarks 125 6.1 Environmental 9 6.2 Operating System 9 17 Disclaimer regarding services and/or software offered by third parties 126 6.3 Display Type 9 6.4 Display Input Resolution 9 Index 127 6.5 Connectivity 9 6.6 Dimensions and Weights 10 6.7 Sound 10 7 Connect Devices 11 7.1 Connect Devices 11 7.2 Receiver - Set-Top Box 12 7.3 Blu-ray Disc Player 12 7.4 Headphones 12 7.5 Game Console 13 7.6 USB Flash Drive 13 7.7 Computer 13 8 Videos, Photos and Music 15 8.1 From a USB Connection 15 8.2 Play your Videos 15 8.3 View your Photos 15 8.4 Play your Music 16 9 Games 18 9.1 Play a Game 18 10 Professional Menu App 19 10.1 About the Professional Menu App 19 10.2 Open the Professional Menu App 19 10.3 TV Channels 19 10.4 Games 19 10.5 Professional Settings 20 10.6 Google Account 20 11 Android TV Home Screen 22 11.1 About the Android TV Home Screen 22 11.2 Open the Android TV Home Screen 22 11.3 Android TV Settings 22 11.4 Connect your Android TV 25 11.5 Channels 27 11.6 Channel Installation 27 11.7 Internet 29 11.8 Software 29 12 Open Source Software 31 12.1 Open Source License 31 2 1 TV Tour 1.1 Professional Mode What you can do In Professional Mode ON, you can have access to a large number of expert settings that enable advanced control of the TV’s state or to add additional functions. -

Ffmpeg Codecs Documentation Table of Contents

FFmpeg Codecs Documentation Table of Contents 1 Description 2 Codec Options 3 Decoders 4 Video Decoders 4.1 hevc 4.2 rawvideo 4.2.1 Options 5 Audio Decoders 5.1 ac3 5.1.1 AC-3 Decoder Options 5.2 flac 5.2.1 FLAC Decoder options 5.3 ffwavesynth 5.4 libcelt 5.5 libgsm 5.6 libilbc 5.6.1 Options 5.7 libopencore-amrnb 5.8 libopencore-amrwb 5.9 libopus 6 Subtitles Decoders 6.1 dvbsub 6.1.1 Options 6.2 dvdsub 6.2.1 Options 6.3 libzvbi-teletext 6.3.1 Options 7 Encoders 8 Audio Encoders 8.1 aac 8.1.1 Options 8.2 ac3 and ac3_fixed 8.2.1 AC-3 Metadata 8.2.1.1 Metadata Control Options 8.2.1.2 Downmix Levels 8.2.1.3 Audio Production Information 8.2.1.4 Other Metadata Options 8.2.2 Extended Bitstream Information 8.2.2.1 Extended Bitstream Information - Part 1 8.2.2.2 Extended Bitstream Information - Part 2 8.2.3 Other AC-3 Encoding Options 8.2.4 Floating-Point-Only AC-3 Encoding Options 8.3 flac 8.3.1 Options 8.4 opus 8.4.1 Options 8.5 libfdk_aac 8.5.1 Options 8.5.2 Examples 8.6 libmp3lame 8.6.1 Options 8.7 libopencore-amrnb 8.7.1 Options 8.8 libopus 8.8.1 Option Mapping 8.9 libshine 8.9.1 Options 8.10 libtwolame 8.10.1 Options 8.11 libvo-amrwbenc 8.11.1 Options 8.12 libvorbis 8.12.1 Options 8.13 libwavpack 8.13.1 Options 8.14 mjpeg 8.14.1 Options 8.15 wavpack 8.15.1 Options 8.15.1.1 Shared options 8.15.1.2 Private options 9 Video Encoders 9.1 Hap 9.1.1 Options 9.2 jpeg2000 9.2.1 Options 9.3 libkvazaar 9.3.1 Options 9.4 libopenh264 9.4.1 Options 9.5 libtheora 9.5.1 Options 9.5.2 Examples 9.6 libvpx 9.6.1 Options 9.7 libwebp 9.7.1 Pixel Format 9.7.2 Options 9.8 libx264, libx264rgb 9.8.1 Supported Pixel Formats 9.8.2 Options 9.9 libx265 9.9.1 Options 9.10 libxvid 9.10.1 Options 9.11 mpeg2 9.11.1 Options 9.12 png 9.12.1 Private options 9.13 ProRes 9.13.1 Private Options for prores-ks 9.13.2 Speed considerations 9.14 QSV encoders 9.15 snow 9.15.1 Options 9.16 vc2 9.16.1 Options 10 Subtitles Encoders 10.1 dvdsub 10.1.1 Options 11 See Also 12 Authors 1 Description# TOC This document describes the codecs (decoders and encoders) provided by the libavcodec library. -

Ffsake: Further Fluff with Ffmpeg

ffsake: further fluff with ffmpeg Talking Tech, Spring 2017 2/5/17 Ethan Gates What is ffmpeg? ● Leading open-source framework for processing and manipulating audiovisual material ● Aims to decode, encode, transcode, mux, demux, stream, filter and play “anything that humans and machines have created” ● A combination of tools and libraries ○ ffmpeg - media conversion ○ ffprobe - metadata analysis/extraction ○ ffplay - playback ■ libavutil - various utilities (e.g. math equations) ■ libavcodec - codec library ■ libavformat - format (wrapper/container) library ■ libavdevice - device library (drivers for common/open hardware) ■ libavfilter - filter library ■ libswscale - scaling library ■ libswresample - audio sampling library Who’s using it? ● VLC Media Player ● YouTube ● Media Player Classic ● Chromium/Google Chrome ● Handbrake ● Facebook ● Audacity ● DaVinci Resolve ● DCP-o-matic ● Axle But what can it do? ● Make derivative copies ● Re-wrap files ● Edit files ● Generate checksums ● Create test files/streams ● Extract/insert metadata ● Generate informative (or just plain cool) audio/video effects ● Livestream video/screencapture * Thanks for this slide, Andrew Weaver Installation All about that configuration! $ brew info ffmpeg $ brew install ffmpeg --with-sdl2 --with-freetype --with-openjpeg --with-x265 --with-rubberband --with-tesseract Translation: with ffplay (playback), with added text/titles support, with JPEG 2000 codec, with H.265 (HEVC) codec, with extra audio filters, with OCR support Tasks to Cover I. Making a test file/signal -

VIDEO DIGITIZATION at the AUSTRIAN MEDIATHEK Chives Obtain a Quality Assurance Instrument for the Recording of Their Media

ARTICLE 8LIIQTPS]QIRXSJWYGLERSRPMRIGIVXM½GEXMSRWIVZMGITVSZMHIWFIRI½XWJSVFSXLTEVXMIWEV- VIDEO DIGITIZATION AT THE AUSTRIAN MEDIATHEK chives obtain a quality assurance instrument for the recording of their media. In the past, sound Herman Lewetz, Austian Mediathek9 carrier owners had to implement quality control by means of a cost-intensive strategy: mul- tiple recording of a single sound medium and time-consuming comparative analysis. The avail- In September 2009 the Austrian Mediathek started a project called “Österreich am Wort“. EFMPMX]SJSFNIGXMZIQIEWYVIQIRXVIWYPXWEPPS[WJSVEHVEWXMGEPP]WMQTPM½IHUYEPMX]QSRMXSVMRK Its goal is to digitize and publish via the web about 10,000 full-length recordings within three years. The misfortune for me personally was that in the proposal for this project someone had For companies or organisations dealing with the process of mass migration of analogue media, claimed 2,000 of these to be video recordings. This meant I had to start what we so far suc- long-term evaluation is an important tool for supporting the continuous internal improve- cessfully had postponed: Video digitization. ment process. For example, slow deterioration over time can be made visible. Besides the cost savings due to precise situation assessment, there is another advantage for service providers: Requirements [LIRYWMRKTPE]FEGOHIZMGIWSJHMJJIVIRXUYEPMX]MXQE]LEZIFIIRHMJ½GYPXXSEVKYIXLILMKLIV costs for recording with high-quality machines to their clients. With the help of the automatic, %WE½VWXWXIT[ISYXPMRIHXLIVIUYMVIQIRXW[IXLSYKLXMQTSVXERXJSVEHMKMXM^EXMSRWGLIQE reference-based analysis, quality differences between average and high-class playback devices that best supported long-term preservation. Unlike audio digitization there is still no widely become easily measurable. By documenting the measurement results, the client can easily see accepted archive format for video. -

Is the Linux Desktop Less Secure Than Windows 10? Or How Super Mario Music Can Own Your System

IS THE LINUX DESKTOP LESS SECURE THAN WINDOWS 10? OR HOW SUPER MARIO MUSIC CAN OWN YOUR SYSTEM. Hanno Böck https://hboeck.de 1 This was too easy . It should not be possible to find a serious memory corruption vulnerability in the default Linux desktop attack surface with just a few minutes of looking. Although it’ s hard to say it, this is not the kind of situation that occurs with a latest Windows 10 default install. Is it possible that Linux desktop security has rotted? (Chris Evans) 2 NINTENDO SOUND FILES (1) Exploit against Gstreamer in Ubuntu 12.04 (LTS). Thumbnail parser. 3 NINTENDO SOUND FILES (2) NSF players are mini-emulators - the attacker can execute code in an emulator. Easier to bypass modern exploit mitigation techniques. 4 FIX The fix is to delete the affected NSF gstreamer plugin. No problem: Ubuntu shipped two different NSF player plugins. 5 FLIC EXPLOIT 6 AUTOMATIC DOWNLOADS Some browsers automatically download files to ~/Downloads. Any webpage can create files on your filesystem. (Chrome/Chromium, Epiphany, ... - not Linux specific) 7 TRACKER GNOME Desktop search tool automatically indexes all new files in a user's home - including ~/Downloads. 8 REACTION FROM TRACKER DEVELOPER Furthermore, the GStreamer guys were extremely fast in fixing it. You could claim that other libraries used for metadata extraction are just as insecure, but that'd really be bugs in these libraries to fix. (Carlos Garnacho) 9 TRACKER PARSERS (1) Gstreamer, ffmpeg, flac, totem-pl-parser, tiff, libvorbis, taglib, libpng, libexif, giflib, libjpeg-turbo, libosinfo, poppler, libxml2, exempi, libgxps, ghostscript, libitpcdata 10 TRACKER PARSERS (2) If you can exploit any of them you can exploit many Linux desktop users from the web without user interaction.