Bandgap Current Reference Using Widlar Current Source

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Temperature and Process Insensitive Cmos Only Reference

A TEMPERATURE AND PROCESS INSENSITIVE CMOS ONLY REFERENCE CURRENT GENERATOR A Thesis Presented to The Graduate Faculty of The University of Akron In Partial Fulfillment of the Requirements for the Degree Master of Science Shivasai Bethi December, 2014 A TEMPERATURE AND PROCESS INSENSITIVE CMOS ONLY REFERENCE CURRENT GENERATOR Shivasai Bethi Thesis Approved: Accepted: ________________________ ________________________ Advisor Department Chair Dr. Kye-shin Lee Dr. Abbas Omar ________________________ ________________________ Committee Member Dean of the College Dr. Joan E. Carletta Dr. George K. Haritos ________________________ ________________________ Committee Member Interim Dean of the Graduate School Dr. Robert Veillette Dr. Rex D. Ramsier ________________________ Date ii ABSTRACT This thesis presents the design of a temperature and process insensitive CMOS only reference current generator. The proposed reference current generator consists of a conventional CMOS Widlar current source, in which the passive resistor is replaced with a transistor resistor. The gate voltage of the transistor resistor is provided by a gate bias generator that makes the output current insensitive to temperature variation. Furthermore, to achieve a process insensitive reference current, three separate gate bias generator circuits for nominal, strong and weak corners were designed. These gate bias generators are manually selected by the control switches to minimize the current variation under different process corners. As an extension of the manual mode selector, the design of an automatic mode selector that automatically selects the optimum gate bias generators to minimize the current variation under different process corners is realized. The proposed reference current generator can be used for high temperature sensor interface applications that include amplifiers, oscillators, filters and data converters. -

Experiment 2: Discrete BJT Op-Amps (Part I)

EE 140 ANALOG INTEGRATED CIRCUITS SPRING 2011 C. Nguyen Experiment 2: Discrete BJT Op-Amps (Part I) This is a three-week laboratory. You are required to write only one lab report for all parts of this experiment. 1.0. INTRODUCTION In this lab, we will introduce and study the properties of a few circuit blocks commonly used to build operational amplifiers. Because we are limited to using discrete components, we will not be able to construct a complete op-amp. This will be done in the op-amp design project later in the semester. In this lab, however, we will ask you to analyze and design circuits commonly used to make integrated circuit operational amplifiers, and you will use these circuits to build a differential amplifier with both resistive and current mirror biasing. Although built with discrete devices, this op-amp uses a classical topology common to most commercial op- amps including the well-known 741. The operation of these circuits will depend on the use of matched transistors. The CA3083 is a matched NPN transistor array built on a single integrated substrate. To ensure that the transistors are properly isolated, you must connect pin 5 of the array to the most negative point of the circuit (-6 volts). Data sheets for the CA3083, and discrete npn and pnp transistors needed in this lab are attached. In this lab more than any other so far, neatness counts. Unless you build your circuits neatly, they will not operate. Trim your resistor leads if necessary. Make sure that you record all the measurements that you make as you proceed, and include these measurements in your lab report. -

B.Tech. Biomedical Engineering

RAMA UNIVERSITY UTTAR PRADESH Faculty of Engineering & Technology SYLLABUS & EVALUATION SCHEME [Effective from the Session 2014-15] B.Tech. Biomedical Engineering 2nd, 3rd&4th Year RAMA UNIVERSITY UTTAR PRADESH, KANPUR A meeting of the Board of Studies of the department of B.Tech Biomedical Engineering of Faculty of Engineering and Technology Rama University Uttar Pradesh, Kanpur was held on 5th July 2014 at 11 AM. The following members were present: 1. …………………………………. Convener 2. …………………………………. Member 3. …………………………………. Member 4. ……………………………… External Member 5. ……………………………… External Member The quorum of the meeting was complete. Agenda of the meeting: 1. Assessment Criteria 2. Question Paper Format 3. Syllabus The meeting resolved unanimously that attached Assessment Criteria, Question Paper Format and Syllabus are justified and approved. Convener Signature: ……………………… Name : ……………………….. Date: Internal Members Signature: 1…………………………………. 2……………………………………… Name: Date: External Members Signature: 1……………………………………… 2………………………………………… Name: Date: Rama University Uttar Pradesh, Kanpur Course Detail and Evaluation Scheme (Effective from the Session 2014-15) B. Tech. Biomedical Engineering Year-2 SEMESTER-III EVALUATION Subject Period S.N. Subject Name SCHEME Total Credit Code L T P CE MTE ETE Theory Subjects 1 BAS-301 Mathematics III 3 1 0 20 20 60 100 4 2 BEC-305 Fundamentals of Electronics Devices 3 1 0 20 20 60 100 4 3 BEC-302 Digital Electronics 3 1 0 20 20 60 100 4 4 BEC-306 Electromagnetic Field Theory 3 1 0 20 20 60 100 4 5 BEC-307 Fundamentals of Network Analysis & Synthesis 3 1 0 20 20 60 100 4 Practicals / Project 6 BEC-351 Electronics Engineering Lab I 0 0 2 30 20 50 100 1 7 BEC-352 Digital Electronics Lab-I 0 0 3 30 20 50 100 1 8 BEC-355 PCB & Electronics Workshop 0 0 2 30 20 50 100 1 9 Total 15 5 7 190 160 450 800 23 L-Lecture, T-Tutorial, P- Practical, CE- Continuous Evaluation, MTE-Mid Term Examination, ETE-End Term Examination Evaluation Scheme: Course without practical components For Continuous Evaluation (CE) is such as: 20 Marks 1. -

Current Mirrors

Current mirrors Current mirrors are important blocks in electronics. They are widely used in several applications and chips, the operational amplifier being one of them. Current mirrors consist of two branches that are parallel to each other and create two approximately equal currents. This is why these circuits are called current mirrors. These currents are used to load other stages in circuits and they are designed in such a way so that current is constant and independent of loading. Current mirrors come in different varieties: Simple current mirror (BJT and MOSFET) Base current corrected simple current mirror Widlar current source Wilson current mirror (BJT and MOSFET) Cascoded current mirror (BJT and MOSFET) For best performance, transistors should be matched, temperature should be the same for all devices and collector-base/drain-gate voltages should also be matched. This will provide equal currents on both sides of the current mirror. All of the circuits have a compliance voltage which is the minimum output voltage required to maintain correct circuit operation: the BJT should be in the active/linear region and the MOSFET should be in the active/saturation region. 1 www.ice77.net Simple current mirror Two implementations exist for the simple current mirror: BJT and MOSFET. BJT The BJT implementation of the simple current mirror is used as a block in the operational amplifier. VCC Vo 3.600V 1.472mA R1 VCC Vo IREF Io I 2k 3.600V 650.0mV V1 V2 Q1 3.6Vdc 0.65Vdc 1.425mA Q2 1.425mA 1.425mA 1.472mA 0V 23.47uA 0V I 23.47uA 655.3mV -

Analog Circuits

Electronics Engineering Analog Circuits Comprehensive Theory with Solved Examples and Practice Questions MADE EASY Publications Corporate Office: 44-A/4, Kalu Sarai (Near Hauz Khas Metro Station), New Delhi-110016 E-mail: [email protected] Contact: 011-45124612, 0-9958995830, 8860378007 Visit us at: www.madeeasypublications.org Analog Circuits © Copyright, by MADE EASY Publications. All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photo-copying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book. First Edition: 2015 Second Edition: 2016 Third Edition: 2017 Fourth Edition: 2018 Fifth Edition: 2019 Sixth Edition: 2020 © All rights reserved by MADE EASY PUBLICATIONS. No part of this book may be reproduced or utilized in any form without the written permission from the publisher. Contents Analog Circuits Chapter 1 Chapter 2 Diode Circuits ������������������������������������������������������ 4 BJT-Characteristics and Biasing ���������������81 1�1 Introduction �������������������������������������������������������������������� 4 2�1 Introduction ������������������������������������������������������������������81 1�2 Diode Circuits : DC Analysis and Models �������������� 4 2�2 Transistors Current Components ���������������������������81 1�3 Diode Logic Gates �������������������������������������������������������11 2�3 Early Effect ���������������������������������������������������������������������85 -

Syllabus Applicable in Gautam Buddh Technical University Lucknow Is

SyllabusApplicable in GautamBuddhTechnicalUniversity Lucknow isadoptedbytheExecutiveCouncilof MahamayaTechnicalUniversity Noida videresolutionno.13,dated24Feb,2011 forbatchesadmittedinsession:2010-11 B.TECH. BIO-MEDICALENGINEERING 2nd, 3rd and 4th Year MAHAMAYATECHNICAL UNIVERSITY, NOIDA SYLLABUS & EVALUATION SCHEME FOR BIOMEDICAL ENGINEERING (B.Tech. Course) Year II, Semester III Evaluation Scheme S.No. SUBJECT PERIODS SESSIONAL Course Code Subject EXAM. ESE Total L T P CT TA Total THEORY SUBJECTS 1. EHU-301/ Industrial Psychology/ 2 0 0 15 10 25 50 75 2 EHU-302 Industrial Sociology 2. EAS-301/ EOE-Mathematics III/ Science 3 1 0 30 20 50 100 150 4 031-EOE-038 based open Elective** 3. EEC-301 Fundamentals of 3 1 0 30 20 50 100 150 4 Electronics Devices 4. EEC-302 Digital Electronics 3 1 0 30 20 50 100 150 4 5. EEC-303 Electromagnetic Field 3 1 0 30 20 50 100 150 4 Theory 6. EEC-304 Fundamentals of Network 3 1 0 30 20 50 100 150 4 Analysis & Synthesis 7. EHU-111 *Human Values & 2 2 0 15 10 25 50 75 - Professional Ethics PRACTICAL/DESIGN/DRAWING 8 EEC-351 Electronics Engineering 0 0 2 -- 20 20 30 50 1 Lab I 9. EEC-352 Digital Electronics Lab-I 0 0 2 -- 20 20 30 50 1 10. EEC-353 PCB & Electronics 0 0 2 -- 10 10 15 25 1 Workshop 11. GP-301 General Proficiency - - - - - 50 - 50 1 Total 17 5 6 165 160 375 625 1000 26 * Human Values & Professional Ethics will be offered as compulsory Audit Course for which passingmarks are 40% in theory & 50% in aggregate. -

Detailed Table of Contents

Analog Circuit Design Discrete and Integrated Sergio Franco San Francisco State University McGraw-Hill Education, 2015 ISBN 978-0-07-802819-9 Detailed Table of Contents 1 DIODES AND THE PN JUNCTION 1.1 The Ideal Diode: Finding the Operating Mode of a Diode, Cut-and-Try Approach, Concluding Observations 1.2 Basic Diode Applications: Rectifiers, Logic Gates, Peak Detectors, The Clamped Capacitor or DC Restorer, Voltage Multipliers and PSpice Simulation 1.3 Operational Amplifiers and Diode Applications: Basic Op Amp Circuits, Our First Diode/Op- Amp Circuit 1.4 Semiconductors: Doping, Drift and Diffusion Currents, An Example: The Integrated-Circuit Diode 1.5 The pn Junction in Equilibrium: Equilibrium Conditions, The Built-in Potential φ0, The Electric Field E0, The SCL Width Xd0, and the SCL Charge Qj0 1.6 Effect of External Bias on the SCL Parameters: The Junction Capacitance Cj 1.7 The pn Diode Equation: Excess Minority Concentrations, The Diode Equation, Short-Base Diodes 1.8 The Reverse-Biased pn Junction: Reverse Breakdown 1.9 Forward-Biased Diode Characteristics: Properties of the Exponential Characteristic, Temperature Dependence, Deviations from Ideality 1.10 Dc Analysis of pn Diode Circuits: Load-Line Analysis, Iterative Analysis, Piecewise-Linear Approximations and Large-Signal Diode Models, Circuit Analysis Using the Piecewise-Linear Approximation, The pn Junction Diode as a Rectifier, the Superdiode 1.11 Ac Analysis of pn Diode Circuits: Small-Signal Operation, The Small-Signal Diode Model, The pn Diode as a Current-Controlled -

Anna University, Chennai University Departments B.E. Electronics and Communication Engineering Regulations – 2019 Vision

ANNA UNIVERSITY, CHENNAI UNIVERSITY DEPARTMENTS B.E. ELECTRONICS AND COMMUNICATION ENGINEERING REGULATIONS – 2019 VISION The Department of ECE shall strive continuously to create highly motivated, technologically competent engineers, be a benchmark and a trend setter in Electronics and Communication Engineering by imparting quality education with interwoven input from academic institutions, research organizations and industries, keeping in phase with rapidly changing technologies imbibing ethical values. MISSION Imparting quality technical education through flexible student centric curriculum evolved continuously for students of ECE with diverse backgrounds. Providing good academic ambience by adopting best teaching and learning practices. Providing congenial ambience in inculcating critical thinking with a quest for creativity, innovation, research and development activities. Enhancing collaborative activities with academia, research institutions and industries by nurturing ethical entrepreneurship and leadership qualities. Nurturing continuous learning in the stat-of-the-art technologies and global outreach programmes resulting in competent world class engineers. 1 ANNA UNIVERSITY, CHENNAI UNIVERSITY DEPARTMENTS B.E. ELECTRONICS AND COMMUNICATION ENGINEERING REGULATIONS – 2019 The Programme defines Programme Educational Objectives, Programme Outcomes and Programme Specific Outcomes as follows: 1. PROGRAMME EDUCATIONAL OBJECTIVES (PEOs): PEO1 Equip the students with sufficient theoretical, analytical and initiative skills in Basic Sciences and Engineering necessary, to assimilate, analyze, synthesis and innovate solutions to meet societal needs. PEO2 To provide adequate research ambience enabling the students to inculcate thirst for life long learning and sustained research interest. PEO3 To instill and practice values, leadership qualities and team spirit to promote entrepreneurship and indigenization. After the course duration of four years, B.E. graduates of Electronics and Communication Engineering will exhibit the following outcomes: 2. -

Module 1-Analog Integrated Circuits Credits-4 Course Code: Ec 204

MODULE 1-ANALOG INTEGRATED CIRCUITS CREDITS-4 COURSE CODE: EC 204 DIFFERENTIAL AMPLIFIERS USING BJT Positive input –Vce1 will be less positive.ie.inverting o/p Ie1 increases which increases the voltage drop across Re Both emitter sides will be positive,whichis eqwt to a Negative base of T2 Thus Vce2 increases and a noninverting o/p is obtained. This is based on the i/p signal at base of T1. DIFFERENTIAL MODE INPUT and OUTPUT Vid=Vi1-Vi2 i/p is applied to both inputs(same magnitude but opposite polarity) and o/p obtained as the difference between two o/ps Vod=Vo1-Vo2 DIFFERENTIAL MODE GAIN Ad=Vod/Vid COMMON MODE INPUT and OUTPUT-i/p is made common to both(same magnitude and same phase) Vi1+Vi2 Vic= ;Voc is of same phase 2 Continued….. Vod DIFFERENTIAL MODE GAIN:Ad= 푉푖푑 푉표푐 COMMON MODE GAIN:Ac= 푉푖푐 퐴푑 COMMON MODE REJECTION RATIO,CMRR= =δ 퐴푐 Usually CMRR=∞ Total o/p=Vo=Vod+Voc=AdVid+AcVic =AdVid(1+ 퐴푐푉푖푐 )= AdVid(1+ 푉푖푐 )≈AdVid for δ>>1 퐴푑푉푖푑 δ푉푖푑 PROPERTIES AND ADVANTAGES: Excellent stability ,High versatility, High immunity to noise, lower cost, easier fabrication as IC and closely matched components. According to the way the i/p signals are applied and o/p signal is taken,different configurations are as follows: Dual input balanced output (o/p measured between two collectors) Dual input unbalanced output Single input balanced output Single input unbalanced output DIFFERNTIAL MODE GAIN Input is applied between two bases.When Vi1 increases Vi2 decreases,ic1 increases and ic2 decreases. -

15Avp201 / Amrita Values Programme I / 1 0 0 1 15Avp211

SYLLABI B. Tech. - Elctronics & Commu. Engg. 2015 admissions onwards SYLLABI B. Tech. - Elctronics & Commu. Engg. 2015 admissions onwards 15AVP201 / AMRITA VALUES PROGRAMME I / 1 0 0 1 Upanishads and Indian Culture – Relevance of Upanishads for modern times – A 15AVP211 AMRITA VALUES PROGRAMME II 1 0 0 1 few Upanishad Personalities: Nachiketas, Satyakama Jabala, Aruni, Shvetaketu. Amrita University's Amrita Values Programme (AVP) is a new initiative to give Message of the Bhagavad Gita exposure to students about richness and beauty of Indian way of life. India is a Introduction to Bhagavad Gita – Brief storyline of Mahabharata - Context of country where history, culture, art, aesthetics, cuisine and nature exhibit more Kurukshetra War – The anguish of Arjuna – Counsel by Sri. Krishna – Key teachings diversity than nearly anywhere else in the world. of the Bhagavad Gita – Karma Yoga, Jnana Yoga and Bhakti Yoga - Theory of Karma and Reincarnation – Concept of Dharma – Concept of Avatar - Relevance Amrita Values Programmes emphasize on making students familiar with the rich of Mahabharata for modern times. tapestry of Indian life, culture, arts, science and heritage which has historically drawn people from all over the world. Life and Message of Swami Vivekananda Brief Sketch of Swami Vivekananda’s Life – Meeting with Guru – Disciplining of Students shall have to register for any two of the following courses, one each in Narendra - Travel across India - Inspiring Life incidents – Address at the Parliament the third and the fourth semesters, which may be offered by the respective of Religions – Travel in United States and Europe – Return and reception India – school during the concerned semester. -

Current Source Biasing

Current Source Biasing • Integrated circuits have transistors which are manufactured simultaneously with the same device parameters (parameters from chip to chip will vary) • As a result, different bias techniques are employed than in discrete designs • One common technique is current source biasing, which allows the designer to take advantage of matched devices • We will begin by looking at some simple current source circuits • A current source is not a “naturally” occurring device. It can be simulated by a network of transistors and circuit elements. The voltage across RE is approximately constant. \ IE is held at a constant value -VEE -VBE I E = RE Problem: For the previous circuits find the bias values IC and VCE for each transistor Solution Assume D1 and D2 forward biases (I1 > IB2) VB = VEE + 2VF = -10V + 2(0.7V) = - 8.6V Using KVL around loop A 2VF = VBE2 + IE2 R2 Since VBE2 @ VF VF 0.7V IE2 = = @ 3.7 mA R2 180W Since IC @ IE IC1 = IC2 = 3.9 mA Check that D1 and D2 are forward biased for a worst case minimum bF = 20 IC2 IB2 = @ 0.19 mA b F VCC -VB 10V - (-8.6V) I1 = = = 0.37 mA R1 50 kW VC1 = VCC - IC1RC = 10V - (3.9 mA)(1kW) = 6.1V VE2 = VB -VBE2 = - 8.6V - 0.7V = - 9.3V VE1 = VC2 = 0V -VBE1 = - 0.7V VCE1 = VC1 -VE1 = 6.1V - (-0.7V) = 6.8V VCE2 = VC2 -VE2 = - 0.7V - (-9.3V) = 8.6V Current Mirrors • Current mirrors also take advantage of matched transistors but require a minimal number of resistors. They are also well suited for circuits with more than one stage. -

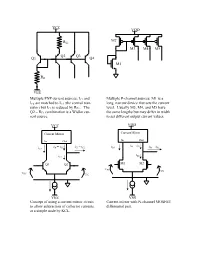

Multiple PNP Current Sources; IC3 and IC4 Are Matched To

VCC VDD R M2 E2 M3 M4 M5 Q2 Q3 Q1 Q4 M1 RB VEE Multiple PNP current sources; IC3 and Multiple P-channel sources: M1 is a IC4 are matched to IC1 (the control tran- long, narrow device that sets the current sistor) but IC2 is reduced by RE2 . The level. Usually M3, M4, and M5 have Q2 – RE2 combination is a Widlar cur- the same lengths but may differ in width rent source. to set different output current values. VCC VDD Current Mirror Current Mirror In Out In Out iM = iD1 iM = iC1 iC1 – iC2 iD1 iD1 – iD2 iC1 iD2 iC2 Q1 Q2 M1 M2 vIN1 vIN2 v IN1 vIN2 VEE VSS Concept of using a current mirror circuit Current mirror with N-channel MOSFET to allow subtraction of collector currents differential pair. at a simple node by KCL. VCC iOUT RBIAS Q1 iOUT Q2 iIN Q1 Q2 RE VEE VEE Widlar current source, for which The most basic current mirror with hi kT ⎛⎞IC1 FE IN I = ln . The collector cur- iOUT = and an output resistance C 2 ⎜⎟ h + 2 qREC⎝⎠I 2 FE rent of Q2 may be much lower than Q1 VVCE + A equal to rO2 = . with only a modest value for RE. IC VCC iIN i iIN i OUT OUT Q3 Q3 Q1 Q2 Q1 Q2 VEE VEE Current mirror using a common collector stage to balance input and output. Output Wilson current mirror –this has a much impedance is still rO2. The minimum higher output resistance from the output voltage is very low – VCESAT of cascoding effect of Q3.