Socket AM3 Processor Functional Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Titan X Amd 1.2 V4 Ig 20210319

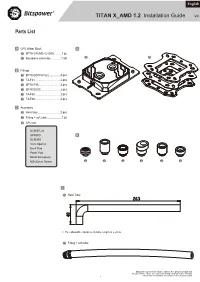

English TITAN X_AMD 1.2 Installation Guide V4 Parts List A CPU Water Block A A-1 BPTA-CPUMS-V2-SKA ..........1 pc A-1 A-2 A-2 Backplane assembly ..............1 set B Fittings B-1 BPTA-DOTFH1622 ...............4 pcs B-2 TA-F61 ...................................2 pcs B-3 BPTA-F95 ..............................2 pcs B-4 BP-RIGOS5 ...........................2 pcs B-5 TA-F60 ..................................2 pcs B-6 TA-F40 ..................................2 pcs C Accessory C-1 Hard tube ..............................2 pcs C-2 Fitting + soft tube ....................1 pc C-3 CPU set SCM3FL20 SPRING B SCM3F6 1mm Spacer Back Pad Paste Pad Metal Backplane M3x32mm Screw B-1 B-2 B-3 B-4 B-5 B-6 C C-1 Hard Tube ※ The allowable variance in tube length is ± 2mm C-2 Fitting + soft tube Bitspower reserves the right to change the product design and interpretations. These are subject to change without notice. Product colors and accessories are based on the actual product. — 1 — I. AMD Motherboard system 54 AMD SOCKET 939 / 754 / 940 IN 48 AMD SOCKET AM4 AMD SOCKET AM3 / AM3+ AMD SOCKET AM2 / AM2+ AMD SOCKET FM1 / FM2+ Bitspower Fan and DRGB RF Remote Controller Hub (Not included) are now available at microcenter.com DRGB PIN on Motherboard or other equipment. 96 90 BPTA-RFCHUB The CPU water block has a DRGB cable, which AMD SOCKET AM4 AMD SOCKET AM3 AM3+ / AMD SOCKET AM2 AM2+ / AMD SOCKET FM1 / FM2+ can be connected to the DRGB extension cable of the radiator fans. Fan and DRGB RF Remote Motherboard Controller Hub (Not included) OUT DRGB LED Do not over-tighten the thumb screws Installation (SCM3FL20). -

FCC Information and Copyright

N68S3B Setup Manual FCC Information and Copyright This equipment has been tested and found to comply with the limits of a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. The vendor makes no representations or warranties with respect to the contents here and specially disclaims any implied warranties of merchantability or fitness for any purpose. Further the vendor reserves the right to revise this publication and to make changes to the contents here without obligation to notify any party beforehand. Duplication of this publication, in part or in whole, is not allowed without first obtaining the vendor’s approval in writing. The content of this user’s manual is subject to be changed without notice and we will not be responsible for any mistakes found in this user’s manual. All the brand and product names are trademarks of their respective companies. Dichiarazione di conformità Short Declaration of conformity sintetica We declare this product is complying Ai sensi dell’art. 2 comma 3 del D.M. with the laws in force and meeting all 275 del 30/10/2002 the essential requirements as specified by the directives Si dichiara che questo prodotto è conforme alle normative vigenti e 2004/108/CE, 2006/95/CE and soddisfa i requisiti essenziali richiesti 1999/05/CE dalle direttive whenever these laws may be applied 2004/108/CE, 2006/95/CE e 1999/05/CE quando ad esso applicabili Table of Contents Chapter 1: Introduction ....................................... -

PURE Crossfirex 790GX

PC-AM3RS790G - PURE CrossFireX 790GX The Sapphire PURE CrossFireX 790GX AM3 is designed for AMD Phenom II™ AM3 true quad-core processors and next generation graphics with high speed DDR3 DRAM module. Performance, scalability, and personalization are coupled with an innovative and efficient design incorporating new ATI CrossFireX and Hybrid CrossFire technologies. The Sapphire PURE CrossFireX 790GX AM3 is designed for PC enthusiasts, high-performance gamers and professional overclockers**. Cut to the chase and open up the system BIOS to mad tweaking for the hardcore overclocker, via real-time control and then using the AMD OverDrive utility. Get the power of multi GPU graphics behind you to experience the ultimate in high definition gaming . Loaded with next generation technologies like PCI Express® 2.0 and HyperTransport™ 3.0 technology, get the ammo you need in gaming, HD editing, and high resolution video to lead the pack, not follow it. Build your dream PC. Start with a Sapphire PURE CrossFireX 790GX AM3 motherboard. Overview Features Features and Benefits AMD Phenom&tarade; Quad-Core Processors with True Quad-Core Technology Realize new possibilities for connecting with friends, family, and digital entertainment with the phenomenal performance of the AMD Phenom™ II AM3 series quad-core processor. Built from the ground up for true quad-core performance, AMD Phenom™ processors speed through advanced multitasking, critical business productivity, advanced visual design and modeling, serious gaming, and visually stunning digital media -

2018 Annual Report on Form 10-K

2018 ANNUAL REPORT ON FORM 10-K MARCH 2019 DEAR SHAREHOLDERS: From the industry’s first 1GHz CPU to the world’s first GPU delivering a teraflop of computing power, AMD has always stood for pushing the boundaries of what is possible. A few years ago, we made several big bets to accelerate our pace of innovation, strengthen our execution, and enable AMD to deliver a leadership portfolio of computing and graphics processors capable of increasing our share of the $75 billion high-performance computing market. In 2018, we saw those bets begin to pay off as we delivered our second straight year of greater than 20% annual revenue growth and significantly improved our gross margin and profitability from the previous year. REVENUE GROSS MARGIN % R&D INVESTMENT EXPENSE/REVENUE % $ Billions $ Billions $6.5B 38% $1.43B 34% $5.3B 34% 33% $4.3B $1.20B 23% $1.01B 31% 2016 2017 2018 2016 2017 2018 2016 2017 2018 2016 2017 2018 Added $2.2B in revenue Significantly improved gross Increased R&D by more than Significant improvement over the last 2 years margin over last 2 years based 40% over the last 2 years in OPEX leverage on new product portfolio Our newest Ryzen™, EPYC™ and datacenter GPU products contributed more than $1.2 billion of revenue in 2018 and helped us gain share across our priority markets. In 2018, we added 3.9% points of desktop processor unit share, 5.3% points of notebook processor unit share and met our goal of exiting the year with mid-single digit server processor market share. -

AMD Socket 939/AM2/AM2+/AM3

10318 Bluegrass Parkway Ph: 502-499-0117 Louisville, KY 40299 Fax: 502-499-0981 www.computeroutlet.net Open M-F: 9:30 to 6:00 [email protected] Rev. 08/03/2012 Processors Motherboards Memory AMD Socket 939/AM2/AM2+/AM3/AM3+/FM1 AMD Socket 754 FP/EDO AMD 3200+ 939 $59 Jetway S755Twin $59 16 M/32M/64M FP/EDO 72 Pin Simm $11/21/49 Socket AM3: Athlon II 250 X2/ 960T X4 $80 / 129 AMD Socket FM1 SDRAM Socket AM3+: FX4100/FX6100/FX8120 $125/165/189 Gigabyte A75M-D2H $99 64/128 MB SDRAM 66 MHz $19/39 Socket FM1: AMD X4-631/A3300/A3650 APU $129/119/129 AM2+(DDR2) 64M/128M/256M/512M SDRAM PC100/133 $10/15/25/45 Intel Socket 775/1055/1056/2011/LGA771 ASRock mAtx A/V/Lan $69 512 MB SDRAM PC100 /133 Ecc/Reg $69 Socket 775:Celeron 430 1.8G $49 AM3(DDR3) DDR1 E6400/E6420/E7500/E8500 $135/139/145/169 Gigabyte M68MT-D3 $69 128/256M/512M/1 G DDR266/333/400 $15/19/29/39 Quad Q8300 $175 Gigabyte GA-880GM-UD2H $105 256M/512M/ 1G (ECC/REG )DDR266/333/400 $35/49/89 Socket 1156 G6950:i3-540/i5-760/i7-950 $119/142/239/315 Biostar A880G+ $69 256M /512M/1G DDR266/333/400 Notebook $20/25/45 Socket 1155: i3-2100/i5-2400/i5-3450/i7-2600/i7-2600k $146/222/219/359/369 Biostar N68S3+ $69 DDR2 Socket 2011: i7- 3820/3930K $344/677 Foxconn A7DA-S 3.0 $119 256M/512M/ 1G/ 2G/4G 400/533/667/800 $10/20/29/39/89 Foxconn M61PMP-K $69 512M/ 1GB /2GB 400/533/667 ECC only $29/39/55 Xeon ASRock N68-VS3 UCC $69 1G/2G/4G ECC/REG or ECC Full Buffered $45/89/159 3065/3110/3430 $199/235/279 MSI 760GM-E51 $99 256M/512M Notebook $10/20 Xeon Dual Core MSI 790X-G45 $129 1G/2G/4G Notebook -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

Six-Core AMD Opteron™ Processor with AMD

AMD最新テクノロジーアップデート -HPCへの取り組み- 日本AMD株式会社 マーケティング&ビジネス開発本部 エンタープライズプロダクトマーケティング部 部長 山野 洋幸 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 2 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 3 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 Planned Server Platform Roadmap 2006 2007 2008 2009 2010 2011 “Maranello” Socket G34 with AMD SR56x0 and SP5100 Magny-Cours New Architecture Six-Core AMD Opteron™ Processor with AMD way Chipset - Socket F(1207) with AMD SR56x0 and SP5100 Shanghai/Istanbul Platform 2/4 Enterprise Enterprise “Socket F (1207)” Socket F(1207) -

M3A760GMH AMD RS780L (760G) + SB710 Chipsets Detail Specification Platform - Micro ATX Form Factor: 9.6-In X 9.0-In, 24.4 Cm X 22.9 Cm

M3A760GMH AMD RS780L (760G) + SB710 Chipsets www.asrock.com Detail Specification Platform - Micro ATX Form Factor: 9.6-in x 9.0-in, 24.4 cm x 22.9 cm CPU - Support for Socket AM3 processors: AMD PhenomTM II X6 / X4 / X3 / X2 (except 920 / 940) / Athlon II X4 / X3 / X2 / Sempron processors - Six-Core CPU Ready - Supports AMD OverDrive™ with ACC feature (Advanced Clock Calibration) - Supports AMD's Cool 'n' Quiet Technology - FSB 2600 MHz (5.2 GT/s) - Supports Untied Overclocking Technology - Supports Hyper-Transport 3.0 (HT 3.0) Technology Chipset - Northbridge: AMD RS780L (760G) - Southbridge: AMD SB710 - Dual Channel DDR3 memory technology Memory - 4 x DDR3 DIMM slots - Supports DDR3 1800(OC)/1600(OC)/1333/1066/800 non-ECC, un-buffered memory - Max. capacity of system memory: 16GB - 1 x PCI Express 2.0 x16 slot (blue @ x16 mode) Expansion Slot - 1 x PCI Express 2.0 x1 slot - 2 x PCI slots - Supports ATITM Hybrid CrossFireXTM - Integrated AMD Radeon 3000 graphics Audio - DX10 class iGPU, Pixel Shader 4.0 - Max. shared memory 512MB - Three VGA Output options: D-Sub, DVI-D and HDMI - Supports HDMI Technology with max. resolution up to 1920x1200 (1080P) - Supports Dual-link DVI with max. resolution up to 2560x1600 @ 75Hz - Supports D-Sub with max. resolution up to 2048x1536 @ 60Hz - Supports HDCP function with DVI and HDMI ports - Supports Full HD 1080p Blu-ray (BD) / HD-DVD playback with DVI and HDMI ports - 7.1 CH HD Audio with Content Protection (Realtek ALC892 Audio Codec) Audio - Premium Blu-ray audio support - PCIE x1 Gigabit LAN 10/100/1000 -

TA790XE Motherboard

TA790XE Motherboard • Supported Socket AM3 processors AMD Phenom II processor • Support latest AMD Phenom X4 , X3 / Athlon /Sempron processors • AMD 125W processor support • AMD 790X / SB750 chipset • 4 DIMM supported DDR2-1200/1066 • HyperTransport 3.0 and PCI Express 2.0 • BIOSTAR G.P.U (Green Power Utility ) Technology • Performance discrete ATX platform • AMD OverDrive™ with ACC feature (Advanced Clock Calibration) supported TA790XE Specifcation CPU SUPPORT AMD Phenom™ II X6 Processor AMD Phenom™ II X4 Processor AMD Phenom™ II X3 Processor AMD Phenom™ II X2 Processor AMD Phenom™ X4 Processor AMD Phenom™ X3 Processor AMD Athlon™ II X2 Processor AMD Athlon™ X2 Dual-Core Processor AMD Athlon™ 64 X2 Dual-Core Processor AMD Athlon™ 64 FX Processor AMD Athlon™ 64 Processor BIOSTARAMD Sempron™ Processor Maximum CPU TDP (Thermal Design Power) : 125Watt HT Support HT 5.2G MEMORY Support Dual Channel DDR2 533/667/800/1066(1066 by AM2+/AM3 CPU) MHz 4 x DDR2 DIMM Memory Slot Max. Supports up to 16GB Memory STORAGE 6 x SATA II Connector 1 x IDE Connector Support SATA RAID: 0,1,5,10 LAN Realtek RTL8111DL - 10/100/1000 Controller AUDIO CODEC Realtek ALC662 6-Channel HD Audio USB 6 x USB 2.0 Port 3 x USB 2.0 Header EXPANSION SLOT 1 x PCI-E 2.0 x16 Slot 2 x PCI-E 2.0 x1 Slot 3 x PCI Slot REAR I/O 1 x PS/2 Mouse 1 x PS/2 Keyboard 6 x USB 2.0 Port 1 x LAN Port 3 x Audio Jacks INTERNAL I/O 3 x USB 2.0 Header 6 x SATA II Connector (3Gb/s ) 1 x IDE Connector 1 x Floppy Connector 1 x Front Audio Header 1 x Front Panel Header 1 x CD-IN Header 1 x S/PDIF-Out -

SKU: 880GMAT-A-E Features Specifications Processor Support Memory Support Dimensions Inside the Box Expansion Stor

WWW.ZOTAC.COM SKU: 880GMAT-A-E Combine the power of AMD Radeon™ HD 4250 graphics processing and multi- core AMD socket AM3 processors with the high-performance micro-ATX form factor ZOTAC 880G platform. The ZOTAC 880G platform supports multi-core AMD Phenom™, AMD Athlon™ and single-core AMD Sempron™ for broad flexibility that lets users choose processing power that suits their computing needs. AMD Radeon™ HD 4250 graphics deliver stunning visuals with Microsoft® DirectX® 10.1 compatibility while AMD Avivo™ HD technology delivers full hardware decode for Blu-ray movies and other high-definition content. Expansion is plentiful with the ZOTAC 880G platform with room for 4 DIMM slots that support up to 16GB of DDR3- 1333 memory, one PCI Express x16, 1 PCI Express x1 and 2 PCI slots, 6 SATA 6.0 Gb/s ports and up to 12 USB 2.0 ports. Specifications Features • AMD 880G + SB850 chipset • AMD Radeon™ HD 4250 • Socket AM3 • AMD Avivo™ Technology • AMD HyperTransport™ 3.0 technology • Microsoft® DirectX® 10.1 • Microsoft® Windows 7/Vista® ready • OpenGL® 3.3 Processor support • AMD Phenom II • AMD Athlon II • AMD Sempron • Up to 95-watt TDP Storage support • 6 SATA 6.0Gb/s Memory support • DDR3-1333 • 4 x 240 pin DDR3 DIMM slots • Up to 16GB ram Connectors • 12 USB ports (4 on back panel, 8 via header) • 1 HD Audio Port (7.1-channel) Expansion • 1 Front panel audio header • 2 Fan headers • 1 x PCI Express x16 • 1 x PCI Express x1 • 2 x PCI Dimensions Display outputs • Micro-ATX form factor • DVI-D (HDCP) • Height: 9.6in - 244mm • HDMI • Width: 8.27in – 210mm • VGA Rear port layout Size comparison Mini-ITX MicroATX ATX Inside the box • 2 SATA cables • 1 I/O back plate © 2011 ZOTAC International (MCO) Limited ZOTAC International (MCO) Limited does not warrant the accuracy, completeness or reliability of information, materials and other items contained on this website or server. -

TA760G M2+ Motherboard

TA760G M2+ Motherboard • Supported Socket AM3 processors AMD Phenom II X4 / Phenom II X3 / Phenom II X2 processor • Support latest AMD Phenom X4 , X3 / Athlon /Sempron processors • AMD 760G chipset • Dual-Channel DDR2 -1066/800/667/533 • Integrated HD3000-based graphics (DX10) • Solid Capacitors designed in CPU VRM area • Support AMD Hybrid CrossFire X Technology • Optional DVI to HDMI adapter TA760G M2+ Specifcation CPU SUPPORT AMD Phenom™ II X4 Processor AMD Phenom™ II X3 Processor AMD Phenom™ II X2 Processor AMD Phenom™ X4 Processor AMD Phenom™ X3 Processor AMD Athlon™ II X2 Processor AMD Athlon™ X2 Dual-Core Processor AMD Athlon™ 64 X2 Dual-Core Processor AMD Athlon™ 64 FX Processor AMD Athlon™ 64 Processor AMD Sempron™ Processor HT Support HT 5.2G MEMORY BIOSTARSupport Dual Channel DDR2 533/667/800/1066 MHz 4 x DDR2 DIMM Memory Slot Max. Supports up to 16GB Memory ※It is recommended to use those Validated DDR2- 1066 modules suggested by AMD INTEGRATED VIDEO ATI Radeon™ HD3000 Graphics, On Board Graphic Max. Memory Share Up to 512 MB STORAGE 6 x SATA II Connector 1 x IDE Connector Support SATA RAID: 0,1,10 LAN Realtek RTL8111C - 10/100/1000 Controller AUDIO CODEC Realtek ALC662 6-Channel HD Audio USB 4 x USB 2.0 Port 3 x USB 2.0 Header EXPANSION SLOT 1 x PCI-E 2.0 x16 Slot 1 x PCI-E 2.0 x1 Slot 2 x PCI Slot REAR I/O 1 x PS/2 Mouse 1 x PS/2 Keyboard 4 x USB 2.0 Port 1 x DVI-D Connector 1 x VGA Port 1 x LAN Port 3 x Audio Jacks INTERNAL I/O 3 x USB 2.0 Header 6 x SATA II Connector (3Gb/s ) 1 x IDE Connector 1 x Floppy Connector 1 x -

AMD Opteron\231 Processor Pricing

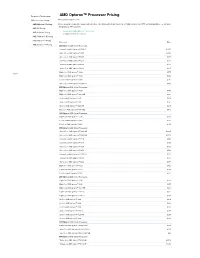

Products & Technologies AMD Opteron™ Processor Pricing AMD Processor Pricing Effective December 4, 2012 AMD Opteron™ Pricing Prices below are subject to change without notice. This listing reflects pricing for direct AMD customers in 1000-unit tray quantities, except when designated as PIB quantities. AMD FX Pricing Shop for all AMD Opteron™ Processors AMD A-Series Pricing Compare Server Processors AMD Phenom™ II Pricing AMD Athlon™ II Pricing Processor Price AMD Sempron™ Pricing AMD Opteron 6300 Series Processors Sixteen-Core AMD Opteron™ 6386 SE $1,392 Sixteen-Core AMD Opteron™ 6380 $1,088 Sixteen-Core AMD Opteron™ 6378 $867 Sixteen-Core AMD Opteron™ 6376 $703 Twelve-Core AMD Opteron™ 6348 $575 Twelve-Core AMD Opteron™ 6344 $415 Eight-Core AMD Opteron™ 6328 $575 Share Eight-Core AMD Opteron™ 6320 $293 Four-Core AMD Opteron™ 6308 $501 Sixteen-Core AMD Opteron™ 6366 HE $575 AMD Opteron 4300 Series Processors Eight-Core AMD Opteron™ 4386 $348 Eight-Core AMD Opteron™ 4376 HE $501 Six-Core AMD Opteron™ 4340 $348 Six-Core AMD Opteron™ 4334 $191 Six-Core AMD Opteron™ 4332 HE $415 Four-Core AMD Opteron™ 4310 EE $415 AMD Opteron 3300 Series Processors Eight-Core AMD Opteron™ 3380 $229 Four-Core AMD Opteron™ 3350 $125 Four-Core AMD Opteron™ 3320 $174 AMD Opteron 6200 Series Processors Sixteen-Core AMD Opteron™ 6284 SE $1265 Sixteen-Core AMD Opteron™ 6282 SE $1,019 Sixteen-Core AMD Opteron™ 6278 $989 Sixteen-Core AMD Opteron™ 6276 $788 Sixteen-Core AMD Opteron™ 6274 $639 Sixteen-Core AMD Opteron™ 6272 $523 Sixteen-Core AMD Opteron™ 6262 HE $523