AN-839 RMS Phase Jitter

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Laser Linewidth, Frequency Noise and Measurement

Laser Linewidth, Frequency Noise and Measurement WHITEPAPER | MARCH 2021 OPTICAL SENSING Yihong Chen, Hank Blauvelt EMCORE Corporation, Alhambra, CA, USA LASER LINEWIDTH AND FREQUENCY NOISE Frequency Noise Power Spectrum Density SPECTRUM DENSITY Frequency noise power spectrum density reveals detailed information about phase noise of a laser, which is the root Single Frequency Laser and Frequency (phase) cause of laser spectral broadening. In principle, laser line Noise shape can be constructed from frequency noise power Ideally, a single frequency laser operates at single spectrum density although in most cases it can only be frequency with zero linewidth. In a real world, however, a done numerically. Laser linewidth can be extracted. laser has a finite linewidth because of phase fluctuation, Correlation between laser line shape and which causes instantaneous frequency shifted away from frequency noise power spectrum density (ref the central frequency: δν(t) = (1/2π) dφ/dt. [1]) Linewidth Laser linewidth is an important parameter for characterizing the purity of wavelength (frequency) and coherence of a Graphic (Heading 4-Subhead Black) light source. Typically, laser linewidth is defined as Full Width at Half-Maximum (FWHM), or 3 dB bandwidth (SEE FIGURE 1) Direct optical spectrum measurements using a grating Equation (1) is difficult to calculate, but a based optical spectrum analyzer can only measure the simpler expression gives a good approximation laser line shape with resolution down to ~pm range, which (ref [2]) corresponds to GHz level. Indirect linewidth measurement An effective integrated linewidth ∆_ can be found by can be done through self-heterodyne/homodyne technique solving the equation: or measuring frequency noise using frequency discriminator. -

Autoencoding Neural Networks As Musical Audio Synthesizers

Proceedings of the 21st International Conference on Digital Audio Effects (DAFx-18), Aveiro, Portugal, September 4–8, 2018 AUTOENCODING NEURAL NETWORKS AS MUSICAL AUDIO SYNTHESIZERS Joseph Colonel Christopher Curro Sam Keene The Cooper Union for the Advancement of The Cooper Union for the Advancement of The Cooper Union for the Advancement of Science and Art Science and Art Science and Art NYC, New York, USA NYC, New York, USA NYC, New York, USA [email protected] [email protected] [email protected] ABSTRACT This training corpus consists of five-octave C Major scales on var- ious synthesizer patches. Once training is complete, we bypass A method for musical audio synthesis using autoencoding neural the encoder and directly activate the smallest hidden layer of the networks is proposed. The autoencoder is trained to compress and autoencoder. This activation produces a magnitude STFT frame reconstruct magnitude short-time Fourier transform frames. The at the output. Once several frames are produced, phase gradient autoencoder produces a spectrogram by activating its smallest hid- integration is used to construct a phase response for the magnitude den layer, and a phase response is calculated using real-time phase STFT. Finally, an inverse STFT is performed to synthesize audio. gradient heap integration. Taking an inverse short-time Fourier This model is easy to train when compared to other state-of-the-art transform produces the audio signal. Our algorithm is light-weight methods, allowing for musicians to have full control over the tool. when compared to current state-of-the-art audio-producing ma- This paper presents improvements over the methods outlined chine learning algorithms. -

Modeling the Impact of Phase Noise on the Performance of Crystal-Free Radios Osama Khan, Brad Wheeler, Filip Maksimovic, David Burnett, Ali M

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 64, NO. 7, JULY 2017 777 Modeling the Impact of Phase Noise on the Performance of Crystal-Free Radios Osama Khan, Brad Wheeler, Filip Maksimovic, David Burnett, Ali M. Niknejad, and Kris Pister Abstract—We propose a crystal-free radio receiver exploiting a free-running oscillator as a local oscillator (LO) while simulta- neously satisfying the 1% packet error rate (PER) specification of the IEEE 802.15.4 standard. This results in significant power savings for wireless communication in millimeter-scale microsys- tems targeting Internet of Things applications. A discrete time simulation method is presented that accurately captures the phase noise (PN) of a free-running oscillator used as an LO in a crystal- free radio receiver. This model is then used to quantify the impact of LO PN on the communication system performance of the IEEE 802.15.4 standard compliant receiver. It is found that the equiv- alent signal-to-noise ratio is limited to ∼8 dB for a 75-µW ring oscillator PN profile and to ∼10 dB for a 240-µW LC oscillator PN profile in an AWGN channel satisfying the standard’s 1% PER specification. Index Terms—Crystal-free radio, discrete time phase noise Fig. 1. Typical PN plot of an RF oscillator locked to a stable crystal frequency modeling, free-running oscillators, IEEE 802.15.4, incoherent reference. matched filter, Internet of Things (IoT), low-power radio, min- imum shift keying (MSK) modulation, O-QPSK modulation, power law noise, quartz crystal (XTAL), wireless communication. -

Application Note Template

correction. of TOI measurements with noise performance the improved show examples Measurement presented. is correction a noise of means by improvements range Dynamic explained. are analyzer spectrum of a factors the limiting correction. The basic requirements and noise with measurements spectral about This application note provides information | | | Products: Note Application Correction Noise with Range Dynamic Improved R&S R&S R&S FSQ FSU FSG Application Note Kay-Uwe Sander Nov. 2010-1EF76_0E Table of Contents Table of Contents 1 Overview ................................................................................. 3 2 Dynamic Range Limitations .................................................. 3 3 Signal Processing - Noise Correction .................................. 4 3.1 Evaluation of the noise level.......................................................................4 3.2 Details of the noise correction....................................................................5 4 Measurement Examples ........................................................ 7 4.1 Extended dynamic range with noise correction .......................................7 4.2 Low level measurements on noise-like signals ........................................8 4.3 Measurements at the theoretical limits....................................................10 5 Literature............................................................................... 11 6 Ordering Information ........................................................... 11 1EF76_0E Rohde & Schwarz -

AN279: Estimating Period Jitter from Phase Noise

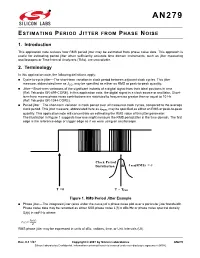

AN279 ESTIMATING PERIOD JITTER FROM PHASE NOISE 1. Introduction This application note reviews how RMS period jitter may be estimated from phase noise data. This approach is useful for estimating period jitter when sufficiently accurate time domain instruments, such as jitter measuring oscilloscopes or Time Interval Analyzers (TIAs), are unavailable. 2. Terminology In this application note, the following definitions apply: Cycle-to-cycle jitter—The short-term variation in clock period between adjacent clock cycles. This jitter measure, abbreviated here as JCC, may be specified as either an RMS or peak-to-peak quantity. Jitter—Short-term variations of the significant instants of a digital signal from their ideal positions in time (Ref: Telcordia GR-499-CORE). In this application note, the digital signal is a clock source or oscillator. Short- term here means phase noise contributions are restricted to frequencies greater than or equal to 10 Hz (Ref: Telcordia GR-1244-CORE). Period jitter—The short-term variation in clock period over all measured clock cycles, compared to the average clock period. This jitter measure, abbreviated here as JPER, may be specified as either an RMS or peak-to-peak quantity. This application note will concentrate on estimating the RMS value of this jitter parameter. The illustration in Figure 1 suggests how one might measure the RMS period jitter in the time domain. The first edge is the reference edge or trigger edge as if we were using an oscilloscope. Clock Period Distribution J PER(RMS) = T = 0 T = TPER Figure 1. RMS Period Jitter Example Phase jitter—The integrated jitter (area under the curve) of a phase noise plot over a particular jitter bandwidth. -

End-To-End Deep Learning for Phase Noise-Robust Multi-Dimensional Geometric Shaping

MITSUBISHI ELECTRIC RESEARCH LABORATORIES https://www.merl.com End-to-End Deep Learning for Phase Noise-Robust Multi-Dimensional Geometric Shaping Talreja, Veeru; Koike-Akino, Toshiaki; Wang, Ye; Millar, David S.; Kojima, Keisuke; Parsons, Kieran TR2020-155 December 11, 2020 Abstract We propose an end-to-end deep learning model for phase noise-robust optical communications. A convolutional embedding layer is integrated with a deep autoencoder for multi-dimensional constellation design to achieve shaping gain. The proposed model offers a significant gain up to 2 dB. European Conference on Optical Communication (ECOC) c 2020 MERL. This work may not be copied or reproduced in whole or in part for any commercial purpose. Permission to copy in whole or in part without payment of fee is granted for nonprofit educational and research purposes provided that all such whole or partial copies include the following: a notice that such copying is by permission of Mitsubishi Electric Research Laboratories, Inc.; an acknowledgment of the authors and individual contributions to the work; and all applicable portions of the copyright notice. Copying, reproduction, or republishing for any other purpose shall require a license with payment of fee to Mitsubishi Electric Research Laboratories, Inc. All rights reserved. Mitsubishi Electric Research Laboratories, Inc. 201 Broadway, Cambridge, Massachusetts 02139 End-to-End Deep Learning for Phase Noise-Robust Multi-Dimensional Geometric Shaping Veeru Talreja, Toshiaki Koike-Akino, Ye Wang, David S. Millar, Keisuke Kojima, Kieran Parsons Mitsubishi Electric Research Labs., 201 Broadway, Cambridge, MA 02139, USA., [email protected] Abstract We propose an end-to-end deep learning model for phase noise-robust optical communi- cations. -

Receiver Sensitivity and Equivalent Noise Bandwidth Receiver Sensitivity and Equivalent Noise Bandwidth

11/08/2016 Receiver Sensitivity and Equivalent Noise Bandwidth Receiver Sensitivity and Equivalent Noise Bandwidth Parent Category: 2014 HFE By Dennis Layne Introduction Receivers often contain narrow bandpass hardware filters as well as narrow lowpass filters implemented in digital signal processing (DSP). The equivalent noise bandwidth (ENBW) is a way to understand the noise floor that is present in these filters. To predict the sensitivity of a receiver design it is critical to understand noise including ENBW. This paper will cover each of the building block characteristics used to calculate receiver sensitivity and then put them together to make the calculation. Receiver Sensitivity Receiver sensitivity is a measure of the ability of a receiver to demodulate and get information from a weak signal. We quantify sensitivity as the lowest signal power level from which we can get useful information. In an Analog FM system the standard figure of merit for usable information is SINAD, a ratio of demodulated audio signal to noise. In digital systems receive signal quality is measured by calculating the ratio of bits received that are wrong to the total number of bits received. This is called Bit Error Rate (BER). Most Land Mobile radio systems use one of these figures of merit to quantify sensitivity. To measure sensitivity, we apply a desired signal and reduce the signal power until the quality threshold is met. SINAD SINAD is a term used for the Signal to Noise and Distortion ratio and is a type of audio signal to noise ratio. In an analog FM system, demodulated audio signal to noise ratio is an indication of RF signal quality. -

Signal-To-Noise Ratio and Dynamic Range Definitions

Signal-to-noise ratio and dynamic range definitions The Signal-to-Noise Ratio (SNR) and Dynamic Range (DR) are two common parameters used to specify the electrical performance of a spectrometer. This technical note will describe how they are defined and how to measure and calculate them. Figure 1: Definitions of SNR and SR. The signal out of the spectrometer is a digital signal between 0 and 2N-1, where N is the number of bits in the Analogue-to-Digital (A/D) converter on the electronics. Typical numbers for N range from 10 to 16 leading to maximum signal level between 1,023 and 65,535 counts. The Noise is the stochastic variation of the signal around a mean value. In Figure 1 we have shown a spectrum with a single peak in wavelength and time. As indicated on the figure the peak signal level will fluctuate a small amount around the mean value due to the noise of the electronics. Noise is measured by the Root-Mean-Squared (RMS) value of the fluctuations over time. The SNR is defined as the average over time of the peak signal divided by the RMS noise of the peak signal over the same time. In order to get an accurate result for the SNR it is generally required to measure over 25 -50 time samples of the spectrum. It is very important that your input to the spectrometer is constant during SNR measurements. Otherwise, you will be measuring other things like drift of you lamp power or time dependent signal levels from your sample. -

Image Denoising by Autoencoder: Learning Core Representations

Image Denoising by AutoEncoder: Learning Core Representations Zhenyu Zhao College of Engineering and Computer Science, The Australian National University, Australia, [email protected] Abstract. In this paper, we implement an image denoising method which can be generally used in all kinds of noisy images. We achieve denoising process by adding Gaussian noise to raw images and then feed them into AutoEncoder to learn its core representations(raw images itself or high-level representations).We use pre- trained classifier to test the quality of the representations with the classification accuracy. Our result shows that in task-specific classification neuron networks, the performance of the network with noisy input images is far below the preprocessing images that using denoising AutoEncoder. In the meanwhile, our experiments also show that the preprocessed images can achieve compatible result with the noiseless input images. Keywords: Image Denoising, Image Representations, Neuron Networks, Deep Learning, AutoEncoder. 1 Introduction 1.1 Image Denoising Image is the object that stores and reflects visual perception. Images are also important information carriers today. Acquisition channel and artificial editing are the two main ways that corrupt observed images. The goal of image restoration techniques [1] is to restore the original image from a noisy observation of it. Image denoising is common image restoration problems that are useful by to many industrial and scientific applications. Image denoising prob- lems arise when an image is corrupted by additive white Gaussian noise which is common result of many acquisition channels. The white Gaussian noise can be harmful to many image applications. Hence, it is of great importance to remove Gaussian noise from images. -

AN10062 Phase Noise Measurement Guide for Oscillators

Phase Noise Measurement Guide for Oscillators Contents 1 Introduction ............................................................................................................................................. 1 2 What is phase noise ................................................................................................................................. 2 3 Methods of phase noise measurement ................................................................................................... 3 4 Connecting the signal to a phase noise analyzer ..................................................................................... 4 4.1 Signal level and thermal noise ......................................................................................................... 4 4.2 Active amplifiers and probes ........................................................................................................... 4 4.3 Oscillator output signal types .......................................................................................................... 5 4.3.1 Single ended LVCMOS ........................................................................................................... 5 4.3.2 Single ended Clipped Sine ..................................................................................................... 5 4.3.3 Differential outputs ............................................................................................................... 6 5 Setting up a phase noise analyzer ........................................................................................................... -

Active Noise Control Over Space: a Subspace Method for Performance Analysis

applied sciences Article Active Noise Control over Space: A Subspace Method for Performance Analysis Jihui Zhang 1,* , Thushara D. Abhayapala 1 , Wen Zhang 1,2 and Prasanga N. Samarasinghe 1 1 Audio & Acoustic Signal Processing Group, College of Engineering and Computer Science, Australian National University, Canberra 2601, Australia; [email protected] (T.D.A.); [email protected] (W.Z.); [email protected] (P.N.S.) 2 Center of Intelligent Acoustics and Immersive Communications, School of Marine Science and Technology, Northwestern Polytechnical University, Xi0an 710072, China * Correspondence: [email protected] Received: 28 February 2019; Accepted: 20 March 2019; Published: 25 March 2019 Abstract: In this paper, we investigate the maximum active noise control performance over a three-dimensional (3-D) spatial space, for a given set of secondary sources in a particular environment. We first formulate the spatial active noise control (ANC) problem in a 3-D room. Then we discuss a wave-domain least squares method by matching the secondary noise field to the primary noise field in the wave domain. Furthermore, we extract the subspace from wave-domain coefficients of the secondary paths and propose a subspace method by matching the secondary noise field to the projection of primary noise field in the subspace. Simulation results demonstrate the effectiveness of the proposed algorithms by comparison between the wave-domain least squares method and the subspace method, more specifically the energy of the loudspeaker driving signals, noise reduction inside the region, and residual noise field outside the region. We also investigate the ANC performance under different loudspeaker configurations and noise source positions. -

MDOT Noise Analysis and Public Meeting Flow Chart

Return to Handbook Main Menu Return to Traffic Noise Home Page SPECIAL NOTES – Special Situations or Definitions INTRODUCTION 1. Applicable Early Preliminary Engineering and Design Steps 2. Mandatory Use of the FHWA Traffic Noise Model (TMN) 1.0 STEP 1 – INITIAL PROJECT LEVEL SCOPING AND DETERMINING THE APPROPRIATE LEVEL OF NOISE ANALYSIS 3. Substantial Horizontal or Vertical Alteration 4. Noise Analysis and Abatement Process Summary Tables 5. Controversy related to non-noise issues--- 2.0 STEP 2 – NOISE ANALYSIS INITIAL PROCEDURES 6. Developed and Developing Lands: Permitted Developments 7. Calibration of Noise Meters 8. Multi-family Dwelling Units 9. Exterior Areas of Frequent Human Use 10. MDOT’s Definition of a Noise Impact 3.0 STEP 3 – DETERMINING HIGHWAY TRAFFIC NOISE IMPACTS AND ESTABLISHING ABATEMENT REQUIREMENTS 11. Receptor Unit Soundproofing or Property Acquisition 12. Three-Phased Approach of Noise Abatement Determination 13. Non-Barrier Abatement Measures 14. Not Having a Highway Traffic Noise Impact 15. Category C and D Analyses 16. Greater than 5 dB(A) Highway Traffic Noise Reduction 17. Allowable Cost Per Benefited Receptor Unit (CPBU) 18. Benefiting Receptor Unit Eligibility 19. Analyzing Apartment, Condominium, and Single/Multi-Family Units 20. Abatement for Non-First/Ground Floors 21. Construction and Technology Barrier Construction Tracking 22. Public Parks 23. Land Use Category D 24. Documentation in the Noise Abatement Details Form Return to Handbook Main Menu Return to Traffic Noise Home Page Return to Handbook Main Menu Return to Traffic Noise Home Page 3.0 STEP 3 – DETERMINING HIGHWAY TRAFFIC NOISE IMPACTS AND ESTABLISHING ABATEMENT REQUIREMENTS (Continued) 25. Barrier Optimization 26.