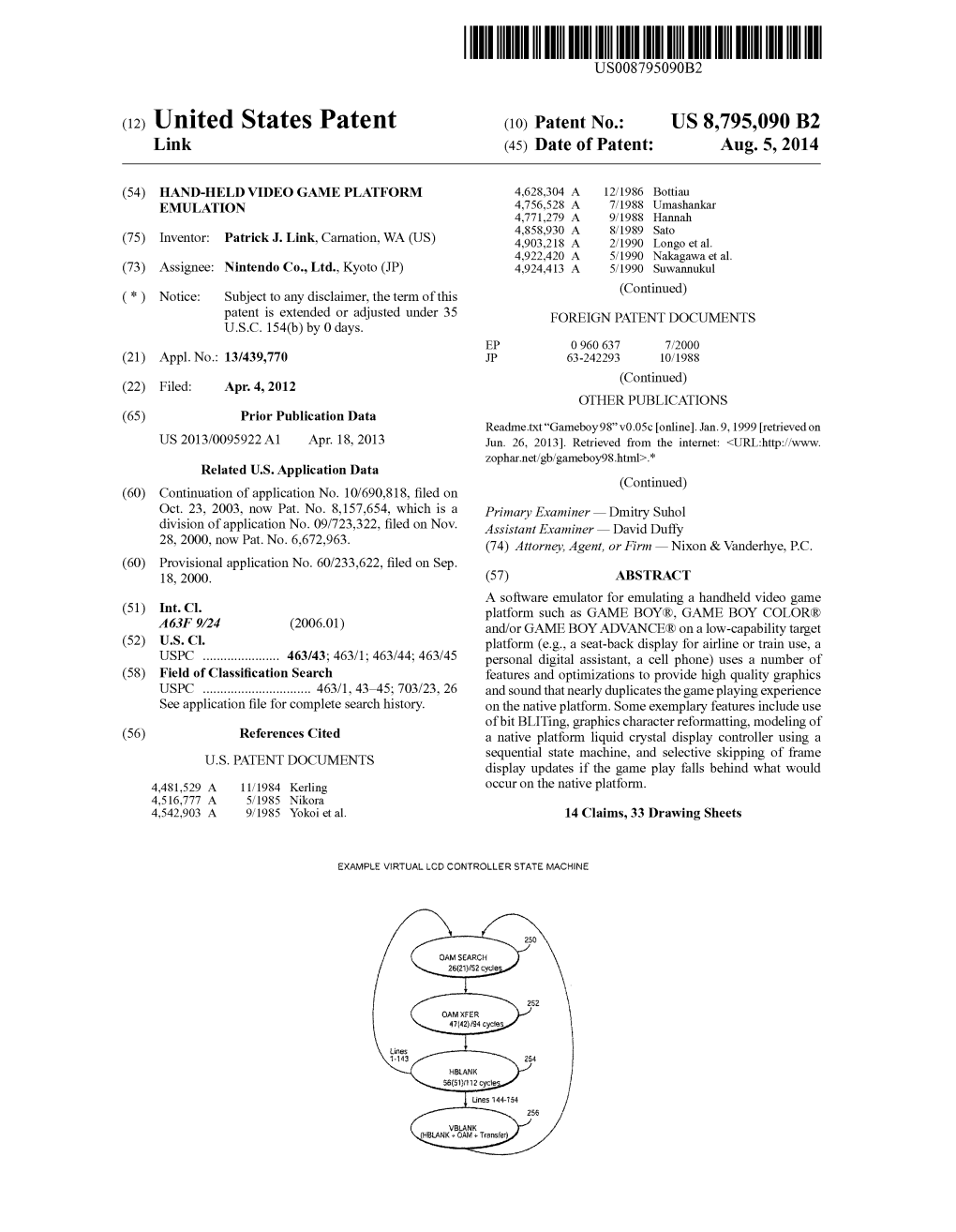

S.Apply N. C.3.32. Filed on Nov. Assistant Examiner David Duty

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Metadefender Core V4.13.1

MetaDefender Core v4.13.1 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Zurück in Die 80Er

TITEL Spiele-Emulatoren Alte Games auf neuer Hardware Zurück in die 80er Tim Schürmann, Schwelgen Sie mit uns in Erinnerungen: Mit den vorgestellten Software-Emulatoren spielen Hans-Georg Eßer Sie alte Klassiker unter modernen Linux-Distributionen. Wir stellen ein paar Programme vor, die Computer aus den 1980ern nachahmen. or vielen, vielen Jahren scheuch- ner kleinen Zeitreise steht somit nichts mit der PlayStation aus: Bereits die erste ten Anwender einen Klempner mehr im Weg. Ausgabe von 1994 enthielt ein CD-Lauf- V namens Mario durch eine pixe- werk, und passende Spiele erhalten Sie lige, grüne Landschaft, schossen sich in Anschluss gesucht günstig auf Flohmärkten oder bei Ebay. 2-D-Welten durch Horden von Monstern Zunächst müssen Sie die alten Pro- Videospielkonsolen und Handhelds wie und versuchten, alle gelben Punkte zu gramme, Spiele und Dokumente irgendwie der Game Boy von Nintendo nutzen indi- fressen, bevor das Gespenst um die Ecke auf Ihren aktuellen Computer bringen. Für viduelle Steckmodule, und die Inhalte kam. Die alte Software aus dem vorheri- die bis Mitte der 1990er-Jahre eingesetzten wandern nur mit speziellen, selbst gebas- gen Jahrhundert läuft nicht mehr unter Disketten finden Sie vereinzelt im Handel telten Lesegeräten auf den PC. modernen Linux-Distributionen, und die oder auf Flohmärkten passende Lauf- Wenn Sie einen Computer emulieren einstigen Computer und Videospielkonso- werke. Moderne Rechner bieten allerdings möchten, benötigen Sie außerdem das len sind zudem meist defekt, verkauft keine Anschlüsse mehr dafür. Zudem ver- passende Betriebssystem. In den meisten oder gar entsorgt. wenden die alten Systeme eigene Speich- Heimcomputern aus den 1980er- Glücklicherweise gibt es Emulatoren, erformate. -

Vintage Game Consoles: an INSIDE LOOK at APPLE, ATARI

Vintage Game Consoles Bound to Create You are a creator. Whatever your form of expression — photography, filmmaking, animation, games, audio, media communication, web design, or theatre — you simply want to create without limitation. Bound by nothing except your own creativity and determination. Focal Press can help. For over 75 years Focal has published books that support your creative goals. Our founder, Andor Kraszna-Krausz, established Focal in 1938 so you could have access to leading-edge expert knowledge, techniques, and tools that allow you to create without constraint. We strive to create exceptional, engaging, and practical content that helps you master your passion. Focal Press and you. Bound to create. We’d love to hear how we’ve helped you create. Share your experience: www.focalpress.com/boundtocreate Vintage Game Consoles AN INSIDE LOOK AT APPLE, ATARI, COMMODORE, NINTENDO, AND THE GREATEST GAMING PLATFORMS OF ALL TIME Bill Loguidice and Matt Barton First published 2014 by Focal Press 70 Blanchard Road, Suite 402, Burlington, MA 01803 and by Focal Press 2 Park Square, Milton Park, Abingdon, Oxon OX14 4RN Focal Press is an imprint of the Taylor & Francis Group, an informa business © 2014 Taylor & Francis The right of Bill Loguidice and Matt Barton to be identified as the authors of this work has been asserted by them in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988. All rights reserved. No part of this book may be reprinted or reproduced or utilised in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage or retrieval system, without permission in writing from the publishers. -

Pipenightdreams Osgcal-Doc Mumudvb Mpg123-Alsa Tbb

pipenightdreams osgcal-doc mumudvb mpg123-alsa tbb-examples libgammu4-dbg gcc-4.1-doc snort-rules-default davical cutmp3 libevolution5.0-cil aspell-am python-gobject-doc openoffice.org-l10n-mn libc6-xen xserver-xorg trophy-data t38modem pioneers-console libnb-platform10-java libgtkglext1-ruby libboost-wave1.39-dev drgenius bfbtester libchromexvmcpro1 isdnutils-xtools ubuntuone-client openoffice.org2-math openoffice.org-l10n-lt lsb-cxx-ia32 kdeartwork-emoticons-kde4 wmpuzzle trafshow python-plplot lx-gdb link-monitor-applet libscm-dev liblog-agent-logger-perl libccrtp-doc libclass-throwable-perl kde-i18n-csb jack-jconv hamradio-menus coinor-libvol-doc msx-emulator bitbake nabi language-pack-gnome-zh libpaperg popularity-contest xracer-tools xfont-nexus opendrim-lmp-baseserver libvorbisfile-ruby liblinebreak-doc libgfcui-2.0-0c2a-dbg libblacs-mpi-dev dict-freedict-spa-eng blender-ogrexml aspell-da x11-apps openoffice.org-l10n-lv openoffice.org-l10n-nl pnmtopng libodbcinstq1 libhsqldb-java-doc libmono-addins-gui0.2-cil sg3-utils linux-backports-modules-alsa-2.6.31-19-generic yorick-yeti-gsl python-pymssql plasma-widget-cpuload mcpp gpsim-lcd cl-csv libhtml-clean-perl asterisk-dbg apt-dater-dbg libgnome-mag1-dev language-pack-gnome-yo python-crypto svn-autoreleasedeb sugar-terminal-activity mii-diag maria-doc libplexus-component-api-java-doc libhugs-hgl-bundled libchipcard-libgwenhywfar47-plugins libghc6-random-dev freefem3d ezmlm cakephp-scripts aspell-ar ara-byte not+sparc openoffice.org-l10n-nn linux-backports-modules-karmic-generic-pae -

Session 3 15

Proceedings of CGAMES’2006 8th International Conference on Computer Games: Artificial Intelligence and Mobile Systems 24-27 July 2006 Hosted by Galt House Hotel Louisville, Kentucky, USA Organised by University of Wolverhampton in association with University of Louisville and IEEE Computer Society Society for Modelling and Simulation (SCS-Europe) Institution of Electrical Engineers (IEE) British Computer Society (BCS) Digital Games Research Association (DiGRA) International Journal of Intelligent Games and Simulation (IJIGS) Edited by: Quasim Mehdi Guest Editor: Adel Elmaghraby Published by The University of Wolverhampton School of Computing and Information Technology Printed in Wolverhampton, UK ©2006 The University of Wolverhampton Responsibility for the accuracy of all material appearing in the papers is the responsibility of the authors alone. Statements are not necessarily endorsed by the University of Wolverhampton, members of the Programme Committee or associated organisations. Permission is granted to photocopy the abstracts and other portions of this publication for personal use and for the use of students providing that credit is given to the conference and publication. Permission does not extend to other types of reproduction nor to copying for use in any profit-making purposes. Other publications are encouraged to include 300-500 word abstracts or excerpts from any paper, provided credits are given to the author, conference and publication. For permission to publish a complete paper contact Quasim Mehdi, SCIT, University of Wolverhampton, Wulfruna Street, Wolverhampton, WV1 1SB, UK, [email protected]. All author contact information in these Proceedings is covered by the European Privacy Law and may not be used in any form, written or electronic without the explicit written permission of the author and/or the publisher. -

Arcade Machine Reloaded Build Documentation

Arcade Machine Build Documentation v5.0 Revision Date: 2011-02-03 Author: Jeremy Riley (AKA Zorro) http://www.flashingblade.net Table of Contents Arcade Machine Reloaded Build Documentation....................................................................5 Introduction.................................................................................................................................5 Windows & MAMEWah Build..............................................................................................................5 MAMEWah Quickstart................................................................................................... 6 Hardware Notes:....................................................................................................... 11 Arcade Monitor Settings.................................................................................................................11 Arcade Keys...............................................................................................................................12 Tuning MAMEWah...................................................................................................... 13 MAME Resolutions.........................................................................................................................13 Using Custom Layouts....................................................................................................................13 Artwork.......................................................................................................................................................................................................................13 -

Video Game Emulation and ROM Hacking Introduction

Chang Li Writing 340 – Harlynn Ramsey About the author – Chang is a junior previously majoring in computer science, now having turned to the dark side, also known as electrical engineering. In her spare time, she enjoys reading user-written documentation on reverse engineering and hacking. Spending time in gray area communities has led to many one-on-one encounters with a number of influential developers in the CS and EE world who also enjoy activities of questionable copyright legality. Keywords – electrical engineering, computer science, entertainment Suggested multimedia - http://www.youtube.com/watch?v=_lnogpRPvY4 – Speedrun of NES Rockman http://www.youtube.com/watch?v=3UnB1fomvAw – hacking Pokemon Yellow for arbitrary code execution http://www.youtube.com/watch?v=7_HMLvLB7b0 – CS student proposes by hacking SNES Chrono Trigger Abstract – Retro video games and game consoles are harder to find and use today, both because they are out of production and the units that still work slowly stop working with age. However, the experiences of the past live on through today's emulation capabilities on the computer. With new technologies come new possibilities, and video game emulation is no different. Against the danger of copyright violation, emulation has thrived, because of both its access to old gaming experiences and new gaming possibilities. F1 to Load State: Video Game Emulation and ROM Hacking Introduction Today, many games for consoles and handhelds such as the PlayStation or Gameboy can be played on the computer. This is accomplished through emulators, which read data from copies of original games and process it for play on the current operating system, usually the computer. -

SDL Game Development

SDL Game Development Discover how to leverage the power of SDL 2.0 to create awesome games in C++ Shaun Ross Mitchell BIRMINGHAM - MUMBAI SDL Game Development Copyright © 2013 Packt Publishing All rights reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, without the prior written permission of the publisher, except in the case of brief quotations embedded in critical articles or reviews. Every effort has been made in the preparation of this book to ensure the accuracy of the information presented. However, the information contained in this book is sold without warranty, either express or implied. Neither the author, nor Packt Publishing, and its dealers and distributors will be held liable for any damages caused or alleged to be caused directly or indirectly by this book. Packt Publishing has endeavored to provide trademark information about all of the companies and products mentioned in this book by the appropriate use of capitals. However, Packt Publishing cannot guarantee the accuracy of this information. First published: June 2013 Production Reference: 1170613 Published by Packt Publishing Ltd. Livery Place 35 Livery Street Birmingham B3 2PB, UK. ISBN 978-1-84969-682-1 www.packtpub.com Cover Image by Shaun Mitchell ([email protected]) Credits Author Project Coordinator Shaun Ross Mitchell Hardik Patel Reviewers Proofreader Luka Horvat Bernadette Watkins Mårten Möller Indexer Acquisition Editor Rekha Nair Edward Gordon Graphics Lead Technical Editor Ronak Dhruv Savio Jose Chalini Snega Victor Production Coordinator Prachali Bhiwandkar Technical Editors Jeeten Handu Cover Work Prachali Bhiwandkar Kaustubh S. -

Ai-Tem: Testing Ai in Commercial Game with Emulator

AI-TEM: TESTING AI IN COMMERCIAL GAME WITH EMULATOR Worapoj Thunputtarakul and Vishnu Kotrajaras Department of Computer Engineering Chulalongkorn University, Bangkok, Thailand E-mail: [email protected], [email protected] KEYWORDS emulator of Game Boy Advance (GBA), developed to test Testbed , Artificial Intelligence, Commercial Game. many AI methods. In this paper, an emulator means a game console/handheld ABSTRACT emulator that simulates the working of game console/handheld hardware such as GBA, PlayStation, and Many artificial intelligence (AI) game researchers find that it arcade machine on any personal computer. There are many is difficult to find a game environment that they can emulators of console/handheld game hardware. appropriately test their AI on. They usually have to develop VisualboyAdvance (VBA) (VisualboyAdvance 2005) and parts of an existing game, using tools that come with the VisualboyAdvance Link (VBA Link) (VisualboyAdvance game. Some even have to re-write their testing game from Link 2005) are GBA emulators. ePSXe is a PlayStation scratch. Finding a perfect game environment that one can emulator. Even arcade machines have MAME as their use to test his AI is not easy, especially if a commercial- emulators. quality game is required. Huge amount of time and effort are ROM (Read Only Memory) is the game data dumped lost in finding such ideal testbed. This paper presents AI- from the original game cartridge or disc. Using a game ROM TEM environment, a testing environment for testing AI by with its emulator, a game can be simulated and played on using console game emulator and its ROM data to simulate PC. -

A MOD Player for GBA

Thesis report, June 2010 A MOD Player for GBA Bachelor’s Thesis in Computer Engineering Lin Ge & Danqing Ni School of Information Science, Computer and Electrical Engineering, Halmstad University 1 A MOD Player for GBA School of Information Science, Computer and Electrical Engineering Halmstad University Box 823, S-301 18 Halmstad, Sweden June 2010 2 Acknowledgement There is no royal road to learning… --Anthony Trollope We would like to thank LYPSON, a company from Halmstad, for giving us the opportunity to work with this project. Its trust and guidance since the beginning of the project give us a lot of help and confidence; and our supervisor, Edison Pignaton de Freitas, from Halmstad University, for his wonderful supervision and feedback during our thesis, especially about academic issues and our weekly report. Furthermore, we would also like to thank to Kenneth Nilsson. When we choose and write our thesis topic, he gave us a lot of helpful advice. At last, we would like to thank them all other classmates and teachers for their valuable ideas and discussions regarding the project, and reviewing our thesis. i Details Authors: Lin Ge & Danqing Ni University: Halmstad University, Sweden Degree Program: Computer Science and Engineering Title of Thesis: A MOD Player for GBA Supervisor: Edison Pignaton de Freitas ii Abstract Abstract This bachelor thesis describes the development of a MOD music player to run on GBA (Game Boy Advance) for Lypson Game Engine. GBA is a basic platform for embedded development, and the stereo system makes it possible to use the platform as a music player. -

Welcome to Visualboyadvance Version 1.7.2. Compiling the Sources ------See the INSTALL File for Compiling Instructions

Welcome to VisualBoyAdvance version 1.7.2. Compiling the sources --------------------- See the INSTALL file for compiling instructions. Please note the following requisites to compile: - GCC must be 3.x or greater in order to compile GBA.cpp with -O2. Earlier versions have a problem during optimization that requires an absurd ammount of memory and usually ends up crashing the compiler/computer - On Windows, Microsoft Visual C++ 6 or later is needed. Please note that some of the source code will not compile with the shipped header files. You will need to install the most recent Platform SDK from Microsoft. Support ------- Please support VisualBoyAdvance by making a donation. You can donate money using PayPal (www.paypal.com). Use the contact form to find how you can send donations. Also, it is recommended that you use the VisualBoyAdvance forum on www.ngemu.com message board. Default keys (can be edited in the Options menu) ------------------------------------------------ Arrow keys - direction Z - Button A X - Button B A - Button L S - Button R Enter - Start Backspace - Select Speedup - Space Capture - F12 You can change the configuration above to use a joystick. Go to Options->Joypad->Configure... menu. The 1 thorugh 4 joypads allow you to have different settings which can be easily switched. System requirements ------------------- Fast computer (Pentium III 500 Mhz recommended) and Microsoft DirectX 7 or greater. Translations ------------ Translations can be done as long as you have Microsoft Visual VC++ on your computer. If you just want to use a translation, place the translation .DLL on the same directory as the emulator. From the Options->Language menu, select Other.. -

Raspberry Pi: Mach's Einfach

CHRISTIAN IMMLER RASPBERRY PI MACH’S EINFACH DIE KOMPAKTESTE GEBRAUCHSANWEISUNG MIT 222 ANLEITUNGEN KOMPLETT ÜBERARBEITETE AUSGABE geeignet für Raspberry Pi 3 Modell B / B+ 60351-5_19x24_Titelei 2018.qxp_X 10.04.18 09:30 Seite 1 Christian Immler Raspberry Pi Mach´s einfach 60351-5_19x24_Titelei 2018.qxp_X 10.04.18 09:30 Seite 3 CHRISTIAN IMMLER RASPBERRY PI MACH’S EINFACH DIE KOMPAKTESTE GEBRAUCHSANWEISUNG MIT 222 ANLEITUNGEN 60351-5_19x24_Titelei 2018.qxp_X 10.04.18 09:30 Seite 4 Bibliografische Information der Deutschen Bibliothek Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Daten sind im Internet über http://dnb.ddb.de abrufbar. Hinweis: Alle Angaben in diesem Buch wurden vom Autor mit größter Sorgfalt erarbeitet bzw. zusammengestellt und unter Einschaltung wirksamer Kontrollmaß- nahmen reproduziert. Trotzdem sind Fehler nicht ganz auszuschließen. Der Verlag und der Autor sehen sich deshalb gezwungen, darauf hinzuweisen, dass sie weder eine Garantie noch die juristische Verantwortung oder irgendeine Haftung für Folgen, die auf fehlerhafte Angaben zurückgehen, übernehmen können. Für die Mitteilung etwaiger Fehler sind Verlag und Autor jederzeit dankbar. Internetadressen oder Versionsnummern stellen den bei Redaktionsschluss verfügbaren Informationsstand dar. Verlag und Autor übernehmen keinerlei Verantwortung oder Haftung für Veränderungen, die sich aus nicht von ihnen zu vertretenden Umständen ergeben. Evtl. beigefügte oder zum Download angebotene Dateien und Informationen