Processor Memory (RAM)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Different Types of RAM RAM RAM Stands for Random Access Memory. It Is Place Where Computer Stores Its Operating System. Applicat

Different types of RAM RAM RAM stands for Random Access Memory. It is place where computer stores its Operating System. Application Program and current data. when you refer to computer memory they mostly it mean RAM. The two main forms of modern RAM are Static RAM (SRAM) and Dynamic RAM (DRAM). DRAM memories (Dynamic Random Access Module), which are inexpensive . They are used essentially for the computer's main memory SRAM memories(Static Random Access Module), which are fast and costly. SRAM memories are used in particular for the processer's cache memory. Early memories existed in the form of chips called DIP (Dual Inline Package). Nowaday's memories generally exist in the form of modules, which are cards that can be plugged into connectors for this purpose. They are generally three types of RAM module they are 1. DIP 2. SIMM 3. DIMM 4. SDRAM 1. DIP(Dual In Line Package) Older computer systems used DIP memory directely, either soldering it to the motherboard or placing it in sockets that had been soldered to the motherboard. Most memory chips are packaged into small plastic or ceramic packages called dual inline packages or DIPs . A DIP is a rectangular package with rows of pins running along its two longer edges. These are the small black boxes you see on SIMMs, DIMMs or other larger packaging styles. However , this arrangment caused many problems. Chips inserted into sockets suffered reliability problems as the chips would (over time) tend to work their way out of the sockets. 2. SIMM A SIMM, or single in-line memory module, is a type of memory module containing random access memory used in computers from the early 1980s to the late 1990s . -

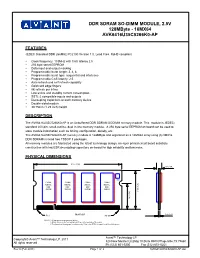

DDR SDRAM SO-DIMM MODULE, 2.5V 128Mbyte - 16MX64 AVK6416U35C5266K0-AP

DDR SDRAM SO-DIMM MODULE, 2.5V 128MByte - 16MX64 AVK6416U35C5266K0-AP FEATURES JEDEC Standard DDR 266MHz PC2100 Version 1.0, Lead Free, RoHS compliant Clock frequency: 133MHz with CAS latency 2.5 256 byte serial EEPROM Data input and output masking Programmable burst length: 2, 4, 8 Programmable burst type: sequential and interleave Programmable CAS latency: 2.5 Auto refresh and self refresh capability Gold card edge fingers 8K refresh per 64ms Low active and standby current consumption SSTL-2 compatible inputs and outputs Decoupling capacitors at each memory device Double-sided module 30.75mm (1.25 inch) height DESCRIPTION The AVK6416U35C5266K0-AP is an Unbuffered DDR SDRAM SODIMM memory module. This module is JEDEC- standard 200-pin, small-outline, dual in-line memory module. A 256 byte serial EEPROM on board can be used to store module information such as timing, configuration, density, etc. The AVK6416U35C5266K0-AP memory module is 128MByte and organized as a 16MX64 array using (8) 8MX16 DDR SDRAMs in lead free TSSOP II packages. All memory modules are fabricated using the latest technology design, six-layer printed circuit board substrate construction with low ESR decoupling capacitors on-board for high reliability and low noise. PHYSICAL DIMENSIONS 67.60 (2.66) 3.50 (0.14) SPD 128Mbit 128Mbit 128Mbit 128Mbit ) 5 8MbX16 8MbX16 8MbX16 8MbX16 2 . 1 ( DDR DDR DDR DDR 5 7 SDRAM SDRAM SDRAM SDRAM . 1 ) 3 7 8 7 . 0 ( 0 2 FRONT SIDE 1.00 (0.04) Pin 1 Pin 199 NOTES: 1- All dimensions are in milimeters (inches) 2- All blue ICs are on the front, and all red ICs are on the back side of the module. -

Dynamic Random Access Memory Topics

Dynamic Random Access Memory Topics Simple DRAM Fast Page Mode (FPM) DRAM Extended Data Out (EDO) DRAM Burst EDO (BEDO) DRAM Synchronous DRAM (SDRAM) Rambus DRAM (RDRAM) Double Data Rate (DDR) SDRAM One capacitor and transistor of power, the discharge y Leaks a smallcapacitor amount slowly Simplicit refresh Requires top sk de in ed Us le ti la o v General DRAM Formats • DRAM is produced as integrated circuits (ICs) bonded and mounted into plastic packages with metal pins for connection to control signals and buses • In early use individual DRAM ICs were usually either installed directly to the motherboard or on ISA expansion cards • later they were assembled into multi-chip plug-in modules (DIMMs, SIMMs, etc.) General DRAM formats • Some Standard Module Type: • DRAM chips (Integrated Circuit or IC) • Dual in-line Package (DIP) • DRAM (memory) modules • Single in-line in Package(SIPP) • Single In-line Memory Module (SIMM) • Dual In-line Memory Module (DIMM) • Rambus In-line Memory Module (RIMM) • Small outline DIMM (SO-DIMM) Dual in-line Package (DIP) • is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins • 14 pins Single in-line in Package (SIPP) • It consisted of a small printed circuit board upon which were mounted a number of memory chips. • It had 30 pins along one edge which mated with matching holes in the motherboard of the computer. Single In-line Memory Module (SIMM) SIMM can be a 30 pin memory module or a 72 pin Dual In-line Memory Module (DIMM) Two types of DIMMs: a 168-pin SDRAM module and a 184-pin DDR SDRAM module. -

SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer

Primer SDRAM Memory Systems: Architecture Overview and Design Verification SDRAM Memory Systems: Architecture Overview and Design Verification Primer Table of Contents Introduction . 3 - 4 DRAM Trends . .3 DRAM . 4 - 6 SDRAM . 6 - 9 DDR SDRAM . .6 DDR2 SDRAM . .7 DDR3 SDRAM . .8 DDR4 SDRAM . .9 GDDR and LPDDR . .9 DIMMs . 9 - 13 DIMM Physical Size . 9 DIMM Data Width . 9 DIMM Rank . .10 DIMM Memory Size & Speed . .10 DIMM Architecture . .10 Serial Presence Detect . .12 Memory System Design . .13 - 15 Design Simulation . .13 Design Verification . .13 Verification Strategy . .13 SDRAM Verification . .14 Glossary . .16 - 19 2 www.tektronix.com/memory SDRAM Memory Systems: Architecture Overview and Design Verification Primer Introduction Memory needs to be compatible with a wide variety of memory controller hubs used by the computer DRAM (Dynamic Random Access Memory) is attractive to manufacturers. designers because it provides a broad range of performance Memory needs to work when a mixture of different and is used in a wide variety of memory system designs for manufacturer’s memories is used in the same memory computers and embedded systems. This DRAM memory system of the computer. primer provides an overview of DRAM concepts, presents potential future DRAM developments and offers an overview Open memory standards are useful in helping to ensure for memory design improvement through verification. memory compatibility. DRAM Trends On the other hand, embedded systems typically use a fixed There is a continual demand for computer memories to be memory configuration, meaning the user does not modify larger, faster, lower powered and physically smaller. These the memory system after purchasing the product. -

Datakommunikasjon Og Maskinvare

Institutt for økonomi og IT Datakommunikasjon og maskinvare Kompendium til emnet 6105N Windows Server og datanett Jon Kvisli Universitetet i Sørøst-Norge, Januar 2020 © Jon Kvisli, 2020 Windows® og Windows Server® er varemerker registrert av Microsoft Corporation. Det må ikke kopieres fra dette heftet ut over det som er tillatt etter bestemmelser i «Lov om opphavsrett til åndsverk», og avtaler om kopiering inngått med Kopinor. Forsidebilde: Colourbox Sats: Jon Kvisli 2 Innhold 1. GRUNNPRINSIPPER I DATAKOMMUNIKASJON .......................................................................... 4 1.1. Punkt-til-punkt kommunikasjon ................................................................................................................ 4 1.2. Kommunikasjonsbusser ............................................................................................................................. 8 1.3. Signalering ................................................................................................................................................ 10 1.4. Dempning, støy og forvrengning.............................................................................................................. 14 1.5. Digitale og analoge signaler ..................................................................................................................... 16 1.6. Noen kommunikasjonsstandarder ........................................................................................................... 17 1.7. Sammendrag ........................................................................................................................................... -

Advances in Computer Random Access Memory Himadri Barman

Advances in Computer Random Access Memory Himadri Barman Introduction Random‐access memory (RAM) is a form of computer data storage and is typically associated with the main memory of a computer. RAM in popular context is volatile but as would be seen later on in the discussion, they need not be. Because of increasing complexity of the computer, emergence of portable devices, etc., RAM technology is undergoing tremendous advances. This report looks at some recent advances in RAM technology, including that of the conventional Dynamic Random Access Memory in the form of DDR 3 (Double Data Rate Type 3). We also look at the emerging area of Non‐volatile random‐access memory (NVRAM). NVRAM is random‐access memory that retains its information when power is turned off, which is described technically as being non‐volatile. This is in contrast to the most common forms of random access memory today, dynamic random‐access memory (DRAM) and static random‐access memory (SRAM), which both require continual power in order to maintain their data. NVRAM is a subgroup of the more general class of non‐volatile memory types, the difference being that NVRAM devices offer random access, unlike hard disks. Double Data Rate 3 Synchronous Dynamic Random Access Memory DDR 3, the third‐generation of DDR SDRAM technology, is a modern kind of DRAM with a high bandwidth interface. It is one of several variants of DRAM and associated interface techniques used since the early 1970s. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of RAM due to different signaling voltages, timings, and other factors. -

High Bandwidth Memory Interface Design Based on DDR3 SDRAM and FPGA

High bandwidth memory interface design based on DDR3 SDRAM and FPGA Baopo Wang1,2, Jinsong Du1,3, Xin Bi1,3*and Xing Tian1,3 1Shenyang Institute of Automation, Chinese Academy of Sciences, China 2University of Chinese Academy of Sciences, China 3Key Laboratory of Liaoning Province on Radar System and Application, China E-mail: [email protected] *Corresponding author: Xin Bi; E-mail: [email protected] Abstract—This work presented the high bandwidth memory addressing. The address bus consists of A[14:0] and BA[2:0], interface design based on DDR3 SDRAM using external memory while the data bus including DQ[31:0] and the source IP core provided by FPGA devices. The structure and synchronous clock DQS[3:0]. configuration of IP core was introduced and the simulation on soft and hard IP was carried out with the access controller designed. The maximum transmission bandwidth of the memory interface based on the soft and hard IP respectively reached 19.2Gbps and 25.6Gbps. Finally, the reliability of the interface controller was verified by downloading the program to the DAQ board and observing the internal signals. Keywords-Memory interface; DDR3; FPGA; IP; High Figure 1. The schematic diagram of the DAQ board and the storage module bandwidth III. MEMORY INTERFACE DESIGN AND SIMULATION I. INTRODUCTION Memory performance has become a key factor in A. Introduction and configuration of the IP core. improving the overall performance of the real time system[1], The devices of Cyclone V series provide available hard or requirements on the data processing, the stability and the power soft IP for external memory interface including DDR3. -

Low-Power, High-Bandwidth, and Ultra-Small Memory Module Design

LOW-POWER, HIGH-BANDWIDTH AND ULTRA- SMALL MEMORY MODULE DESIGN by Qawi IbnZayd Harvard A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Boise State University May 2011 BOISE STATE UNIVERSITY GRADUATE COLLEGE DEFENSE COMMITTEE APPROVAL of the dissertation submitted by Qawi IbnZayd Harvard We have read and discussed the dissertation submitted by student Qawi IbnZayd Harvard, and we have also evaluated his presentation and response to questions during the final oral examination. We find that the student has passed the final oral examination, and that the dissertation is satisfactory for a doctoral degree and ready for any final modifications that we may explicitly require. ______________________ __________________________________________ Date R. Jacob Baker, Ph.D. Chair, Supervisory Committee ______________________ __________________________________________ Date John Chiasson, Ph.D. Member, Supervisory Committee ______________________ __________________________________________ Date Robert Hay, Ph.D. Member, Supervisory Committee ______________________ __________________________________________ Date Sin Ming Loo, Ph.D. Member, Supervisory Committee ______________________ __________________________________________ Date Pinaki Muzumder, Ph.D. External Examiner BOISE STATE UNIVERSITY GRADUATE COLLEGE FINAL READING APPROVAL of the dissertation submitted by Qawi IbnZayd Harvard To the Graduate College of Boise State University: I have read the dissertation of Qawi IbnZayd Harvard in its final form and have found that (1) the modifications required by the defense committee are complete; (2) the format, citations, and bibliographic style are consistent and acceptable; (3) the illustrative materials including figures, tables, and charts are in place; and (4) the final manuscript is ready for submission to the Graduate College. ______________________ __________________________________________ Date R. Jacob Baker, Ph.D. -

Considerations for Designing an Embedded IA System with DDR3 ECC SO-DIMMS

White Paper David Hibler Jr Considerations for Platform Solutions Engineer Intel Corporation designing an Embedded IA System with DDR3 ECC SO-DIMMs September 2012 326491 Considerations for Designing an Embedded IA System with DDR3 ECC SO-DIMMS Executive Summary What are ECC SO-DIMMs? How do I design with them in my platform? If these are some of the questions you have when the term “ECC SO-DIMM” comes up, then this paper may be for you. Since the ECC SO-DIMM form factor is an alternative solution that is often considered in the Embedded market this paper will look at all the aspects of preparing for and designing an Embedded system with ECC SO-DIMMs instead of using the traditional DDR3 UDIMM or SO-DIMM memory. Each level of a system design will be addressed in this paper. The ECC SO-DIMM form factor is an alternative solution often considered in the embedded market… The levels of a system design that will be covered include: Product Planning Board Design Software Considerations The goal of this paper is to provide an a starting place for the creation of an Intel Architecture system with ECC SO-DIMM and to help alleviate early questions that system designers may have. The Intel® Embedded Design Center provides qualified developers with web-based access to technical resources. Access Intel Confidential design materials, step-by step guidance, application reference solutions, training, Intel’s tool 2 Considerations for Designing an Embedded IA System with DDR3 ECC SO-DIMMS loaner program, and connect with an e-help desk and the embedded community. -

DDR2 SDRAM SO-DIMM MODULE, 1.8V 1Gbyte - 128MX64 AVK6428U61E5667F1

DDR2 SDRAM SO-DIMM MODULE, 1.8V 1GByte - 128MX64 AVK6428U61E5667F1 FEATURES JEDEC Standard DDR2 PC2-5300 667MHz - Clock frequency: 333MHz with CAS latency 5 - 256 byte serial EEPROM - Data input and output masking - Programmable burst length: 2, 4, 8 - Programmable burst type: sequential and interleave - Programmable CAS latency: 5 - Auto refresh and self refresh capability - Gold card edge fingers - 8K refresh per 64ms - Low active and standby current consumption - SSTL-2 compatible inputs and outputs - Decoupling capacitors at each memory device - Double-sided module - 1.18 inch height DESCRIPTION The AVK6428U61E5667F1 family consists of Unbuffered DDR2 SDRAM SODIMM memory module. This module is JEDEC-standard 200-pin, small-outline, dual in-line memory module. A 256 byte serial EEPROM on board can be used to store module information such as timing, configuration, density, etc. The AVK6428U61E5667F1 memory module is 1GByte and organized as a 128MX64 array using (8) 128MX8 (4 internal banks) DDR2 SDRAMs in BGA packages. All memory modules are fabricated using the latest technology design, six-layer printed circuit board substrate construction with low ESR decoupling capacitors on-board for high reliability and low noise. PHYSICAL DIMENSIONS 2.661 0.040 512MBit 512MBit 512MBit 512MBit 1.18 64MX8 DDR2 64MX8 DDR2 64MX8 DDR2 64MX8 DDR2 BGA SDRAM BGA SDRAM BGA SDRAM BGA SDRAM 1024MBit (16MX8X8) 1024MBit (16MX8X8) 1024MBit (16MX8X8) 1024MBit (16MX8X8) S 128MX8 DDR2 BGA SDRAM 128MX8 DDR2 BGA SDRAM P 128MX8 DDR2 BGA SDRAM 128MX8 DDR2 BGA SDRAM 0.787 D 1 199 0.140 All gray ICs are on the front side of the module, and all white ICs are on the back side of the module. -

Simms & OTHER MEMORY MODULES

Jaycar Electronics Reference Data Sheet: SIMMS.PDF (1) SIMMs & OTHER MEMORY MODULES In early generations of personal computer, the talking about bytes rather than individual bits. computers RAM (random access, or read-write memory) was in the form of groups or banks of SRAM, DRAM and ROM standard DIL (dual-in-line) IC chips that were either Strictly speaking all memory used in modern computers soldered directly to the mother board or plugged into is random-access memory or RAM, meaning that the sockets on it. However as later computers began to data in any particular memory location or cell is just as need more and more memory, plug-in modules were accessible as any other data, merely by specifying its developed as convenient replacements for this chip unique memory address. However by convention the level memory. term RAM is only used to signify read-write random Most modern PCs are designed to have their memory in access memory, where data can be either written to or the form of these plug-in memory modules. The same read from any address at random. modules are also used to expand the memory inside This is mainly to distinguish read-write memory from laser printers, etc. However its easy to get confused, read-only memory or ROM, where the data can only because there are now both a number of different types be written to (i.e., stored in) each location once, and of module, and also many different kinds of memory from then on only read out when its needed. ROMs are chip used in them. -

8GB (X72, ECC DR) 260-Pin DDR4 SODIMM Features DDR4 SDRAM SODIMM MTA18ASF1G72HZ – 8GB

8GB (x72, ECC DR) 260-Pin DDR4 SODIMM Features DDR4 SDRAM SODIMM MTA18ASF1G72HZ ± 8GB Features Figure 1: 260-Pin SODIMM (MO-310 R/C F) • DDR4 functionality and operations supported as Module height: 30mm (1.181in) defined in the component data sheet • 260-pin, small-outline dual in-line memory module (SODIMM) • Fast data transfer rates: PC4-2666, PC4-2400, or PC4-2133 • 8GB (1 Gig x 72) •VDD = 1.20V (NOM) •VPP = 2.5V (NOM) •V = 2.5V (NOM) DDSPD Figure 2: 260-Pin SODIMM (MO-310 R/C H) • Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals Module height: 30mm (1.181in) • Low-power auto self refresh (LPASR) • Data bus inversion (DBI) for data bus • On-die VREFDQ generation and calibration • Dual-rank • Onboard I2C temperature sensor with integrated serial presence-detect (SPD) EEPROM • 16 internal banks; 4 groups of 4 banks each • Fixed burst chop (BC) of 4 and burst length (BL) of 8 via the mode register set (MRS) Options Marking • Selectable BC4 or BL8 on-the-fly (OTF) • Operating temperature • Gold edge contacts – Commercial None • Halogen-free (0°C ≤ TOPER ≤ 95°C) • Fly-by topology • Package – 260-pin DIMM (halogen-free) Z • Terminated control, command, and address bus • Frequency/CAS latency – 0.75ns @ CL = 19 (DDR4-2666) -2G6 – 0.83ns @ CL = 17 (DDR4-2400) -2G3 – 0.93ns @ CL = 15 (DDR4-2133) -2G1 CCMTD-1725822587-9688 Micron Technology, Inc. reserves the right to change products or specifications without notice. asf18c1gx72hz.pdf – Rev. H 4/18 EN 1 © 2014 Micron Technology, Inc.