Fully Differential Operational Amplifier Design Using Indirect and Negative Miller Compensation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1.5A, 24V, 17Mhz Power Operational Amplifier Datasheet (Rev. E)

OPA564 www.ti.com SBOS372E –OCTOBER 2008–REVISED JANUARY 2011 1.5A, 24V, 17MHz POWER OPERATIONAL AMPLIFIER Check for Samples: OPA564 1FEATURES 23• HIGH OUTPUT CURRENT: 1.5A DESCRIPTION • WIDE POWER-SUPPLY RANGE: The OPA564 is a low-cost, high-current operational – Single Supply: +7V to +24V amplifier that is ideal for driving up to 1.5A into reactive loads. The high slew rate provides 1.3MHz – Dual Supply: ±3.5V to ±12V full-power bandwidth and excellent linearity. These • LARGE OUTPUT SWING: 20VPP at 1.5A monolithic integrated circuits provide high reliability in • FULLY PROTECTED: demanding powerline communications and motor control applications. – THERMAL SHUTDOWN – ADJUSTABLE CURRENT LIMIT The OPA564 operates from a single supply of 7V to 24V, or dual power supplies of ±3.5V to ±12V. In • DIAGNOSTIC FLAGS: single-supply operation, the input common-mode – OVER-CURRENT range extends to the negative supply. At maximum – THERMAL SHUTDOWN output current, a wide output swing provides a 20VPP (I = 1.5A) capability with a nominal 24V supply. • OUTPUT ENABLE/SHUTDOWN CONTROL OUT • HIGH SPEED: The OPA564 is internally protected against over-temperature conditions and current overloads. It – GAIN-BANDWIDTH PRODUCT: 17MHz is designed to provide an accurate, user-selected – FULL-POWER BANDWIDTH AT 10VPP: current limit. Two flag outputs are provided; one 1.3MHz indicates current limit and the second shows a – SLEW RATE: 40V/ms thermal over-temperature condition. It also has an Enable/Shutdown pin that can be forced low to shut • DIODE FOR JUNCTION TEMPERATURE down the output, effectively disconnecting the load. MONITORING The OPA564 is housed in a thermally-enhanced, • HSOP-20 PowerPAD™ PACKAGE surface-mount PowerPAD™ package (HSOP-20) with (Bottom- and Top-Side Thermal Pad Versions) the choice of the thermal pad on either the top side or the bottom side of the package. -

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

Indirect Compensation Techniques for Three- Stage Fully-Differential Op-Amps

1 Indirect Compensation Techniques for Three- Stage Fully-Differential Op-amps Vishal Saxena, Student Member, IEEE and R. Jacob Baker, Senior Member, IEEE op-amps. A novel cascaded fully-differential, three-stage op- Abstract— As CMOS technology continues to evolve, the amp topology is presented with simulation results, which is supply voltages are decreasing while at the same time the tolerant to device mismatches and exhibits superior transistor threshold voltages are remaining relatively constant. performance. Making matters worse, the inherent gain available from the nano-CMOS transistors is dropping. Traditional techniques for achieving high-gain by cascoding become less useful in nano-scale II. INDIRECT FEEDBACK COMPENSATION CMOS processes. Horizontal cascading (multi-stage) must be Indirect Feedback Compensation is a lucrative method to used in order to realize high-gain op-amps in low supply voltage compensate op-amps for higher speed operation [1]. In this processes. This paper discusses indirect compensation techniques for op-amps using split-length devices. A reversed-nested indirect method, the compensation capacitor is connected to an internal compensated (RNIC) topology, employing double pole-zero low impedance node in the first gain stage, which allows cancellation, is illustrated for the design of three-stage op-amps. indirect feedback of the compensation current from the output The RNIC topology is then extended to the design of three-stage node to the internal high-impedance node. Further, in nano- fully-differential op-amps. Novel three-stage fully-differential CMOS processes low-voltage, high-speed op-amps can be gain-stage cascade structures are presented with efficient designed by employing a split-length composite transistor for common mode feedback (CMFB) stabilization. -

Switch-Mode Power Converter Compensation Made Easy

Switch-mode power converter compensation made easy Robert Sheehan Systems Manager, Power Design Services Member Group Technical Staff Louis Diana Field Application, America Sales and Marketing Senior Member Technical Staff Texas Instruments Using this paper as a quick look-up reference can help designers compensate the most popular switch-mode power converter topologies. Engineers have been designing switch-mode power converters for some time now. If you’re new to the design field or you don’t compensate converters all the time, compensation requires some research to do correctly. This paper will break the procedure down into a step-by-step process that you can follow to compensate a power converter. We will explain the theory of compensation and why it is necessary, examine various power stages, and show how to determine where to place the poles and zeros of the compensation network to compensate a power converter. We will examine typical error amplifiers as well as transconductance amplifiers to see how each affects the control loop and work through a number of topologies/examples so that power engineers have a quick reference when they need to compensate a power converter. Introduction Many SMPS designers would appreciate a how- A switch-mode power supply (SMPS) regulates to reference paper that they can use to look up the output voltage against any changes in compensation solutions to various topologies with output loading or input line voltage. An SMPS various feedback modes. We are striving to provide accomplishes this regulation with a feedback loop, this in a single paper. which requires compensation if it has an error Control-loop and compensation amplifier with linear feedback. -

Designing Linear Amplifiers Using the IL300 Optocoupler Application Note

Application Note 50 Vishay Semiconductors Designing Linear Amplifiers Using the IL300 Optocoupler INTRODUCTION linearizes the LED’s output flux and eliminates the LED’s This application note presents isolation amplifier circuit time and temperature. The galvanic isolation between the designs useful in industrial, instrumentation, medical, and input and the output is provided by a second PIN photodiode communication systems. It covers the IL300’s coupling (pins 5, 6) located on the output side of the coupler. The specifications, and circuit topologies for photovoltaic and output current, IP2, from this photodiode accurately tracks the photoconductive amplifier design. Specific designs include photocurrent generated by the servo photodiode. unipolar and bipolar responding amplifiers. Both single Figure 1 shows the package footprint and electrical ended and differential amplifier configurations are discussed. schematic of the IL300. The following sections discuss the Also included is a brief tutorial on the operation of key operating characteristics of the IL300. The IL300 photodetectors and their characteristics. performance characteristics are specified with the Galvanic isolation is desirable and often essential in many photodiodes operating in the photoconductive mode. measurement systems. Applications requiring galvanic isolation include industrial sensors, medical transducers, and IL300 mains powered switchmode power supplies. Operator safety 1 8 and signal quality are insured with isolated interconnections. These isolated interconnections commonly use isolation 2 K2 7 amplifiers. K1 Industrial sensors include thermocouples, strain gauges, and pressure transducers. They provide monitoring signals to a 3 6 process control system. Their low level DC and AC signal must be accurately measured in the presence of high 4 5 common-mode noise. -

NTE7144 Integrated Circuit BIMOS Operational Amplifier W/MOSFET Input, Bipolar Output

NTE7144 Integrated Circuit BIMOS Operational Amplifier w/MOSFET Input, Bipolar Output Description: The NTE7144 is an integrated circuit operational amplifier in an 8–Lead Mini–DIP type package that combines the advantages of high–voltage PMOS transistors with high–voltage bipolar transistors on a single monolithic chip. This device features gate–protected MOSFET (PMOS) transistors in the in- put circuit to provide very–high–input impedance, very–low–input current, and high–speed perfor- mance. The NTE7144 operates at supply voltages from 4V to 36V (either single or dual supply) and is internally phase–compensated to achieve stable operation in unity–gain follower operation. The use of PMOS field–effect transistors in the input stage results in common–mode input–voltage capability down to 0.5V below the negative–supply terminal, an important attribute for single–supply applications. The output stage uses bipolar transistors and includes built–in protection against dam- age from load–terminal short–circuiting to either supply–rail or to GND. Features: D MOSFET Input Stage: Very High Input Impedance Very Low Input Current Wide Common–Mode Input Voltage Range Output Swing Complements Input Common–Mode Range D Directly Replaces Industry Type 741 in Most Applications Applications: D Ground–Referenced Single–Supply Amplifiers in Automobile and Portable Instrumentation D Sample and Hold Amplifiers D Long–Duration Timers/Multivibrators (Microseconds – Minutes – Hours) D Photocurrent Instrumentation D Peak Detectors D Active Filters D Comparators D Interface in 5V TTL Systems and other Low–Supply Voltage Systems D All Standard Operational Amplifier Applications D Function Generators D Tone Controls D Power Supplies D Portable Instruments D Intrusion Alarm Systems Absolute Maximum Ratings: DC Supply Voltage (Between V+ and V– Terminals). -

Example of a MOSFET Operational Amplifier

Example of a MOSFET Operational Amplifier: This circuit is one I “designed” as an example for Engineering 1620. It is certainly not fully optimized and I am not sure it is free of errors. It is based on a 1.5 micron, P-well process and therefore uses an N-channel differential pair for its input. This is somewhat unusual because P-channel devices have lower intrinsic noise and are the device-type of choice for the input stage. I did this simply to avoid doing your SPICE assignment for you. The overall properties of the circuit are given in the table below. Amplifier Property Value A0 – DC Gain 86 DB (X20,000) fp – dominant pole position 400 Hz fGBW 8.0 MHz fU – unity gain frequency 5.6 MHz Output stage resistance at low frequency 277 K Zero position 10.7 MHz Slew Rate 710 6 V/sec Output stage quiescent current 65 a Opamp quiescent current 103 a Bias circuit quiescent current 104 a Total system quiescent current 210 a VDD 5.0 volts Total system power 1.1 mW MOSFET Operational Amplifier Gain and Phase 10 0 18 0 80 12 0 60 Gain 60 Phase 40 0 Gain (DB) 20 -60 Phase (deg.) 0 -120 -20 -180 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Frequency (Hz) Phase margin = 60 deg. Parameter Table for MOSFET Opamp Example element model vds vgs vth vov id gm ro m1 nssb 0.748 0.851 0.547 0.304 3.77E-05 2.90E-04 5.54E+05 m10 nssb 3.368 0.851 0.547 0.304 4.12E-05 3.11E-04 8.09E+05 m12 nssb 0.711 0.711 0.546 0.165 3.51E-05 5.01E-04 5.05E+05 m13 nssb 0.838 0.851 0.547 0.304 3.79E-05 2.91E-04 5.92E+05 m14 nssb 3.078 1.079 0.840 0.239 3.51E-05 -

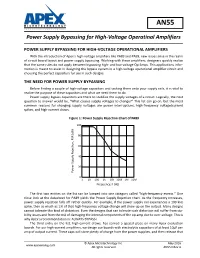

AN55 Power Supply Bypassing for High-Voltage Operational Amplifiers

AN55 Power Supply Bypassing for High-Voltage Operatinal Amplifiers POWER SUPPLY BYPASSING FOR HIGH-VOLTAGE OPERATIONAL AMPLIFIERS With the introduction of Apex’s high-voltage amplifiers like PA89 and PA99, new issues arise in the realm of circuit board layout and power supply bypassing. Working with these amplifiers, designers quickly realize that the same rules do not apply between bypassing high- and low-voltage Op-Amps. This applications infor- mation is meant to assist in designing the bypass system in a high-voltage operational amplifier circuit and choosing the perfect capacitors for use in such designs. THE NEED FOR POWER SUPPLY BYPASSING Before finding a couple of high-voltage capacitors and tacking them onto your supply rails, it is vital to realize the purpose of these capacitors and what we need them to do. Power supply bypass capacitors are there to stabilize the supply voltages of a circuit. Logically, the next question to answer would be, “What causes supply voltages to change?” This list can go on, but the most common reasons for changing supply voltages are power interruptions, high-frequency voltage/current spikes, and high-current draws. Figure 1: Power Supply Rejection Chart of PA89 100 80 60 40 20 WŽǁĞƌ^ƵƉƉůLJZĞũĞĐƟŽŶ͕W^Z;ĚͿ 0 1 10100 1k 10k 100k1M 10M Frequency, F (Hz) The first two entries on the list can be lumped into one category called “high-frequency events.” One close look at the datasheet for PA89 yields the Power Supply Rejection chart. As the frequency increases, power supply rejection falls off rather quickly. For example, if the power supply rail experiences a 100 kHz spike, then as much as 1% of that high-frequency voltage change will show up on the output. -

A Differential Operational Amplifier Circuit Collection

Application Report SLOA064A – April 2003 A Differential Op-Amp Circuit Collection Bruce Carter High Performance Linear Products ABSTRACT All op-amps are differential input devices. Designers are accustomed to working with these inputs and connecting each to the proper potential. What happens when there are two outputs? How does a designer connect the second output? How are gain stages and filters developed? This application note answers these questions and gives a jumpstart to apprehensive designers. 1 INTRODUCTION The idea of fully-differential op-amps is not new. The first commercial op-amp, the K2-W, utilized two dual section tubes (4 active circuit elements) to implement an op-amp with differential inputs and outputs. It required a ±300 Vdc power supply, dissipating 4.5 W of power, had a corner frequency of 1 Hz, and a gain bandwidth product of 1 MHz(1). In an era of discrete tube or transistor op-amp modules, any potential advantage to be gained from fully-differential circuitry was masked by primitive op-amp module performance. Fully- differential output op-amps were abandoned in favor of single ended op-amps. Fully-differential op-amps were all but forgotten, even when IC technology was developed. The main reason appears to be the simplicity of using single ended op-amps. The number of passive components required to support a fully-differential circuit is approximately double that of a single-ended circuit. The thinking may have been “Why double the number of passive components when there is nothing to be gained?” Almost 50 years later, IC processing has matured to the point that fully-differential op-amps are possible that offer significant advantage over their single-ended cousins. -

High-Frequency Amplifier Response

Section H5: High-Frequency Amplifier Response Now that we’ve got a high frequency models for the BJT, we can analyze the high frequency response of our basic amplifier configurations. Note: in the circuits that follow, the actual signal source (vS) and its associated source resistance (RS) have been included. As discussed in the low frequency response section of our studies, we always knew that this source and resistance was there but we just started our investigations with the input to the transistor (vin). Remember - the analysis process is the same and the relationship between vS and vin is a voltage divider! Again, in some instances in the following discussion, I will be using slightly different notation and taking a different approach than your author. As usual, if this results in confusion, or you are more comfortable with his technique, let me know and we’ll work it out. High Frequency Response of the CE and ER Amplifier The generic common-emitter amplifier circuit of Section D2 is reproduced to the left below and the small signal circuit using the high frequency BJT model is given below right (based on Figures 10.17a and 10.17b of your text). Note that all external capacitors are assumed to be short circuits at high frequencies and are not present in the high frequency equivalent circuit (since the external capacitors are large when compared to the internal capacitances – recall that Zc=1/jωC gets small as the frequency or capacitance gets large). We can simplify the small signal circuit by making the following observations and approximations: ¾ Cce is very small and may be neglected. -

Differential AC Boosting Compensation for Power-Efficient

Copyright © 2019 American Scientific Publishers Journal of All rights reserved Low Power Electronics Printed in the United States of America Vol. 15, 379–387, 2019 Differential AC Boosting Compensation for Power-Efficient Multistage Amplifiers Tayebeh Asiyabi1 and Jafar Torfifard2 ∗ 1Department of Electrical Engineering, Mahshahr Branch, Islamic Azad University, Mahshahr, Iran 2Department of Electrical Engineering, Izeh Branch, Islamic Azad University, Izeh, Iran (Received: 26 February 2019; Accepted: 22 July 2019) In this paper, a new architecture of four-stage CMOS operational transconductance amplifier (OTA) based on an alternative differential AC boosting compensation called DACBC is proposed. The pre- sented structure removes feedforward and boosts feedback paths of compensation network simul- taneously. Moreover, the presented circuit uses a fairly small compensation capacitor in the order of 1 pF, which makes the circuit very compact regarding enhanced several small-signal and large- signal characteristics. The proposed circuit along with several state-of-the-art schemes from the literature have been extensively analysed and compared together. The simulation results show with the same capacitive load and power dissipation the unity-gain frequency (UGF) can be improved over 60 times than conventional nested Miller compensation. The results of the presented OTA with 15 pF capacitive load demonstrated 65 phase margin, 18.88 MHz as UGF and DC gain of 115 dB with power dissipation of 462 Wfrom1.8V. Keywords: Differential AC Boosting, Frequency Compensation, CMOS Operational IP: 192.168.39.210 On: Sun, 03 Oct 2021 15:57:22 TransconductanceCopyright: Amplifier American (OTA), Scientific Low Power, Publishers Low Voltage. Delivered by Ingenta 1. INTRODUCTION is compulsory for high-precision purposes. -

Design and Implementation of a Signal Conditioning Operational Amplifier for a Reflective Object Sensor

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Masters Theses Graduate School 12-2010 Design and Implementation of a Signal Conditioning Operational Amplifier for a Reflective Object Sensor Ankit Master University of Tennessee - Knoxville, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_gradthes Part of the Electrical and Electronics Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons Recommended Citation Master, Ankit, "Design and Implementation of a Signal Conditioning Operational Amplifier for a Reflective Object Sensor. " Master's Thesis, University of Tennessee, 2010. https://trace.tennessee.edu/utk_gradthes/820 This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a thesis written by Ankit Master entitled "Design and Implementation of a Signal Conditioning Operational Amplifier for a Reflective Object Sensor." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Master of Science, with a major in Electrical Engineering. Benjamin J. Blalock, Major Professor We have read this thesis and recommend its acceptance: