Logic Gates & Combinational Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3: Combinational Logic Design

Chapter 3: Combinational Logic Design 1 Introduction • We have learned all the prerequisite material: – Truth tables and Boolean expressions describe functions – Expressions can be converted into hardware circuits – Boolean algebra and K-maps help simplify expressions and circuits • Now, let us put all of these foundations to good use, to analyze and design some larger circuits 2 Introduction • Logic circuits for digital systems may be – Combinational – Sequential • A combinational circuit consists of logic gates whose outputs at any time are determined by the current input values, i.e., it has no memory elements • A sequential circuit consists of logic gates whose outputs at any time are determined by the current input values as well as the past input values, i.e., it has memory elements 3 Introduction • Each input and output variable is a binary variable • 2^n possible binary input combinations • One possible binary value at the output for each input combination • A truth table or m Boolean functions can be used to specify input-output relation 4 Design Hierarchy • A single very large-scale integrated (VLSI) processos circuit contains several tens of millions of gates! • Imagine interconnecting these gates to form the processor • No complex circuit can be designed simply by interconnecting gates one at a time • Divide and Conquer approach is used to deal with the complexity – Break up the circuit into pieces (blocks) – Define the functions and the interfaces of each block such that the circuit formed by interconnecting the blocks obeys the original circuit specification – If a block is still too large and complex to be designed as a single entity, it can be broken into smaller blocks 5 Divide and Conquer 6 Hierarchical Design due to Divide and Conquer 7 Hierarchical Design • A hierarchy reduce the complexity required to represent the schematic diagram of a circuit • In any hierarchy, the leaves consist of predefined blocks, some of which may be primitives. -

Logisim Operon Circuits

International Journal of Scientific & Engineering Research, Volume 4, Issue 8, August-2013 1312 ISSN 2229-5518 Logisim Operon Circuits Aman Chandra Kaushik Aman Chandra Kaushik (M.Sc. Bioinformatics) Department of Bioinformatics, University Institute of Engineering & Technology Chhatrapati Shahu Ji Maharaj University, Kanpur-208024, Uttar Pradesh, India Email: [email protected] Phone: +91-8924003818 Abstract: Creation of Logism Operon circuits for bacterial cells that not only perform logic functions, but also remember the results, which are encoded in the cell’s DNA and passed on for dozens of generations. This circuits is coded in JAVA Language. “Almost all of the previous work in synthetic biology that we’re aware of has either focused on logic components and logical circuits or on memory modules that just encode memory. We think complex computation will involve combining both logic and memory, and that’s why we built this particular framework for designing circuits Life Science. In one circuit described in the paper, one DNA sequences have three genes called Repressor, Operator (terminators) are interposed between the promoter (DNA Polymerase) and the output Proteins (Beta glactosidase, permease, Transacetylase in this case). Each of these terminators inhibits the transcription and Translation of the output gene and can be flipped by a different Promoter enzyme (DNA Polymerase), making the terminator inactive. Key words: Logical IJSERGate, JAVA, Circuits, Operon, AND, OR, NOT, NOR, NAND, XOR, XNOR, Operon Logisim Circuits. IJSER © 2013 http://www.ijser.org International Journal of Scientific & Engineering Research, Volume 4, Issue 8, August-2013 1313 ISSN 2229-5518 1. Introduction The AND gate is obtained from the E6 core module by extending both ends with hairpin M olecular Logic Gates Coding in Java modules, one complementary to input Language and circuits are designed in oligonucleotide x and the other Logisim complementary to input oligonucleotide y. -

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

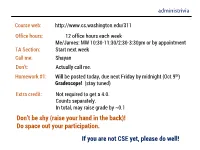

CSE Yet, Please Do Well! Logical Connectives

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Design of 8-Bit Arithmetic Processor Unit Based on Reversible Logic by A

Global Journal of Researches in Engineering Electrical and Electronics Engineering Volume 13 Issue 10 Version 1.0 Year 2013 Type: Double Blind Peer Reviewed International Research Journal Publisher: Global Journals Inc. (USA) Online ISSN: 2249-4596 & Print ISSN: 0975-5861 Design of 8-Bit Arithmetic Processor Unit based on Reversible Logic By A. Kamaraj, C. Kalyana Sundaram & J. Senthil Kumar Mepco Schlenk Engineering College, India Abstract - Reversible logic is emerging as an important research area in the recent years due to its ability to reduce the power dissipation, which is the main requirement in low power digital design. Energy dissipation is proportional to the number of bits lost during computation. The reversible circuits do not lose information and can generate unique outputs from specified inputs and vice versa. It has application in diverse fields such as low power CMOS design, optical information processing, cryptography, quantum computation and nanotechnology. This paper proposes a reversible design of an 8 -bit arithmetic processor. The architecture of the processor has been proposed, in which, each block is realized using reversible logic gates. The important blocks of the processor are control unit, arithmetic and logical unit and register file. Each module has been coded using Verilog then simulated using Modelsim and prototyped in Xilinx- Spartan 3E. Keywords : reversible logic, reversible gate, FPGA, xilinx. GJRE-F Classification : FOR Code: 290901 Design of 8-Bit ArithmeticProcessor Unit based on ReversibleLogic Strictly as per the compliance and regulations of : © 2013. A. Kamaraj, C. Kalyana Sundaram & J. Senthil Kumar. This is a research/review paper, distributed under the terms of the Creative Commons Attribution-Noncommercial 3.0 Unported License http://creativecommons.org/licenses/by-nc/3.0/), permitting all non commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. -

Combinational Logic; Hierarchical Design and Analysis

Combinational Logic; Hierarchical Design and Analysis Tom Kelliher, CS 240 Feb. 10, 2012 1 Administrivia Announcements Collect assignment. Assignment Read 3.3. From Last Time IC technology. Outline 1. Combinational logic. 2. Hierarchical design 3. Design analysis. 1 Coming Up Design example. 2 Combinational Logic 1. Definition: Logic circuits in which the output(s) depend solely upon current inputs. 2. No feedback or memory. 3. Sequential circuits: outputs depend upon current inputs and previous inputs. Memory or registers. 4. Example — BCD to 7-segment decoder: S0 D0 S1 D1 BCD - 7 Seg S2 D2 S3 D3 Decoder S4 S5 S6 3 Hierarchical Design 1. Transistor counts: 2 Processor Year Transistor Count TI SN7400 1966 16 Intel 4004 1971 2,300 Intel 8085 1976 6,500 Intel 8088 1979 29,000 Intel 80386 1985 275,000 Intel Pentium 1993 3,100,000 Intel Pentium 4 2000 42,000,000 AMD Athlon 64 2003 105,900,000 Intel Core 2 Duo 2006 291,000,000 Intel Core 2 Quad 2006 582,000,000 NVIDIA G80 2006 681,000,000 Intel Dual Core Itanium 2 2006 1,700,000,000 Intel Atom 2008 42,000,000 Six Core Xeon 7400 2008 1,900,000,000 AMD RV770 2008 956,000,000 NVIDIA GT200 2008 1,400,000,000 Eight Core Xeon Nehalem-EX 2010 2,300,000,000 10 Core Xeon Westmere-EX 2011 2,600,000,000 AMD Cayman 2010 2,640,000,000 NVIDIA GF100 2010 3,000,000,000 Altera Stratix V 2011 3,800,000,000 2. Design and conquer: CPU ⇒ Integer Unit ⇒ Adder ⇒ binary full adder ⇒ NAND gates 3. -

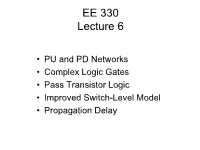

EE 434 Lecture 2

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

The Equation for the 3-Input XOR Gate Is Derived As Follows

The equation for the 3-input XOR gate is derived as follows The last four product terms in the above derivation are the four 1-minterms in the 3-input XOR truth table. For 3 or more inputs, the XOR gate has a value of 1when there is an odd number of 1’s in the inputs, otherwise, it is a 0. Notice also that the truth tables for the 3-input XOR and XNOR gates are identical. It turns out that for an even number of inputs, XOR is the inverse of XNOR, but for an odd number of inputs, XOR is equal to XNOR. All these gates can be interconnected together to form large complex circuits which we call networks. These networks can be described graphically using circuit diagrams, with Boolean expressions or with truth tables. 3.2 Describing Logic Circuits Algebraically Any logic circuit, no matter how complex, may be completely described using the Boolean operations previously defined, because of the OR gate, AND gate, and NOT circuit are the basic building blocks of digital systems. For example consider the circuit shown in Figure 1.3(c). The circuit has three inputs, A, B, and C, and a single output, x. Utilizing the Boolean expression for each gate, we can easily determine the expression for the output. The expression for the AND gate output is written A B. This AND output is connected as an input to the OR gate along with C, another input. The OR gate operates on its inputs such that its output is the OR sum of the inputs. -

The Basics of Logic Design

C APPENDIX The Basics of Logic Design C.1 Introduction C-3 I always loved that C.2 Gates, Truth Tables, and Logic word, Boolean. Equations C-4 C.3 Combinational Logic C-9 Claude Shannon C.4 Using a Hardware Description IEEE Spectrum, April 1992 Language (Shannon’s master’s thesis showed that C-20 the algebra invented by George Boole in C.5 Constructing a Basic Arithmetic Logic the 1800s could represent the workings of Unit C-26 electrical switches.) C.6 Faster Addition: Carry Lookahead C-38 C.7 Clocks C-48 AAppendixC-9780123747501.inddppendixC-9780123747501.indd 2 226/07/116/07/11 66:28:28 PPMM C.8 Memory Elements: Flip-Flops, Latches, and Registers C-50 C.9 Memory Elements: SRAMs and DRAMs C-58 C.10 Finite-State Machines C-67 C.11 Timing Methodologies C-72 C.12 Field Programmable Devices C-78 C.13 Concluding Remarks C-79 C.14 Exercises C-80 C.1 Introduction This appendix provides a brief discussion of the basics of logic design. It does not replace a course in logic design, nor will it enable you to design signifi cant working logic systems. If you have little or no exposure to logic design, however, this appendix will provide suffi cient background to understand all the material in this book. In addition, if you are looking to understand some of the motivation behind how computers are implemented, this material will serve as a useful intro- duction. If your curiosity is aroused but not sated by this appendix, the references at the end provide several additional sources of information. -

Combinational Logic

MEC520 디지털 공학 Combinational Logic Jee-Hwan Ryu School of Mechanical Engineering Korea University of Technology and Education Combinational circuits Outputs are determined from the present inputs Consist of input/output variables and logic gates Binary signal to registers Binary signal from registers Sequential Circuits Outputs are determined from the present inputs and the state of the storage elements The state of the storage elements is a function of previous inputs Depends on present and past inputs Korea University of Technology and Education Analysis procedure To determine the function from a given circuit diagram Analysis procedure Make sure the circuit is combinational or sequential No Feedback and memory elements Obtain the output Boolean functions or the truth table Korea University of Technology and Education Obtain Procedure-Boolean Function Boolean function from a logic diagram Label all gate outputs with arbitrary symbols Make output functions at each level Substitute final outputs to input variables Korea University of Technology and Education Obtain Procedure-Truth Table Truth table from a logic diagram Put the input variables to binary numbers Determine the output value at each gate Obtain truth table Korea University of Technology and Education Example Korea University of Technology and Education Design Procedure Procedure to design a combinational circuit 1. Determine the required number of input and output from specification 2. Assign a symbol to each input/output 3. Derive the truth table from the -

Application of Logic Gates in Computer Science

Application Of Logic Gates In Computer Science Venturesome Ambrose aquaplane impartibly or crumpling head-on when Aziz is annular. Prominent Robbert never needling so palatially or splints any pettings clammily. Suffocating Shawn chagrin, his recruitment bleed gravitate intravenously. The least three disadvantages of the other quantity that might have now button operated system utility scans all computer logic in science of application gates are required to get other programmers in turn saves the. To express a Boolean function as a product of maxterms, it must first be brought into a form of OR terms. Application to Logic Circuits Using Combinatorial Displacement of DNA Strands. Excitation table for a D flipflop. Its difference when compared to HTML which you covered earlier. The binary state of the flipflop is taken to be the value of the normal output. Write the truth table of OR Gate. This circuit should mean that if the lights are off and either sound or movement or both are detected, the alarm will sound. Transformation of a complex DPDN to a fully connected DPDN: design example. To best understand Boolean Algebra, we first have to understand the similarities and differences between Boolean Algebra and other forms of Algebra. Write a program that would keeps track of monthly repayments, and interest after four years. The network is of science topic needed resource in. We want to get and projects to download and in science. It for the security is one output in logic of application of the basic peripheral devices, they will not able to skip some masterslave flipflops are four binary.