DDL Backgrounder

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LINEAR ALGEBRA METHODS in COMBINATORICS László Babai

LINEAR ALGEBRA METHODS IN COMBINATORICS L´aszl´oBabai and P´eterFrankl Version 2.1∗ March 2020 ||||| ∗ Slight update of Version 2, 1992. ||||||||||||||||||||||| 1 c L´aszl´oBabai and P´eterFrankl. 1988, 1992, 2020. Preface Due perhaps to a recognition of the wide applicability of their elementary concepts and techniques, both combinatorics and linear algebra have gained increased representation in college mathematics curricula in recent decades. The combinatorial nature of the determinant expansion (and the related difficulty in teaching it) may hint at the plausibility of some link between the two areas. A more profound connection, the use of determinants in combinatorial enumeration goes back at least to the work of Kirchhoff in the middle of the 19th century on counting spanning trees in an electrical network. It is much less known, however, that quite apart from the theory of determinants, the elements of the theory of linear spaces has found striking applications to the theory of families of finite sets. With a mere knowledge of the concept of linear independence, unexpected connections can be made between algebra and combinatorics, thus greatly enhancing the impact of each subject on the student's perception of beauty and sense of coherence in mathematics. If these adjectives seem inflated, the reader is kindly invited to open the first chapter of the book, read the first page to the point where the first result is stated (\No more than 32 clubs can be formed in Oddtown"), and try to prove it before reading on. (The effect would, of course, be magnified if the title of this volume did not give away where to look for clues.) What we have said so far may suggest that the best place to present this material is a mathematics enhancement program for motivated high school students. -

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

UNIT-I Mathematical Logic Statements and Notations

UNIT-I Mathematical Logic Statements and notations: A proposition or statement is a declarative sentence that is either true or false (but not both). For instance, the following are propositions: “Paris is in France” (true), “London is in Denmark” (false), “2 < 4” (true), “4 = 7 (false)”. However the following are not propositions: “what is your name?” (this is a question), “do your homework” (this is a command), “this sentence is false” (neither true nor false), “x is an even number” (it depends on what x represents), “Socrates” (it is not even a sentence). The truth or falsehood of a proposition is called its truth value. Connectives: Connectives are used for making compound propositions. The main ones are the following (p and q represent given propositions): Name Represented Meaning Negation ¬p “not p” Conjunction p q “p and q” Disjunction p q “p or q (or both)” Exclusive Or p q “either p or q, but not both” Implication p ⊕ q “if p then q” Biconditional p q “p if and only if q” Truth Tables: Logical identity Logical identity is an operation on one logical value, typically the value of a proposition that produces a value of true if its operand is true and a value of false if its operand is false. The truth table for the logical identity operator is as follows: Logical Identity p p T T F F Logical negation Logical negation is an operation on one logical value, typically the value of a proposition that produces a value of true if its operand is false and a value of false if its operand is true. -

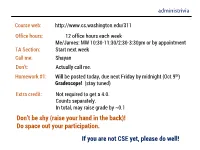

CSE Yet, Please Do Well! Logical Connectives

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

New Approaches for Memristive Logic Computations

Portland State University PDXScholar Dissertations and Theses Dissertations and Theses 6-6-2018 New Approaches for Memristive Logic Computations Muayad Jaafar Aljafar Portland State University Let us know how access to this document benefits ouy . Follow this and additional works at: https://pdxscholar.library.pdx.edu/open_access_etds Part of the Electrical and Computer Engineering Commons Recommended Citation Aljafar, Muayad Jaafar, "New Approaches for Memristive Logic Computations" (2018). Dissertations and Theses. Paper 4372. 10.15760/etd.6256 This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact [email protected]. New Approaches for Memristive Logic Computations by Muayad Jaafar Aljafar A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Dissertation Committee: Marek A. Perkowski, Chair John M. Acken Xiaoyu Song Steven Bleiler Portland State University 2018 © 2018 Muayad Jaafar Aljafar Abstract Over the past five decades, exponential advances in device integration in microelectronics for memory and computation applications have been observed. These advances are closely related to miniaturization in integrated circuit technologies. However, this miniaturization is reaching the physical limit (i.e., the end of Moore’s Law). This miniaturization is also causing a dramatic problem of heat dissipation in integrated circuits. Additionally, approaching the physical limit of semiconductor devices in fabrication process increases the delay of moving data between computing and memory units hence decreasing the performance. The market requirements for faster computers with lower power consumption can be addressed by new emerging technologies such as memristors. -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

The Equation for the 3-Input XOR Gate Is Derived As Follows

The equation for the 3-input XOR gate is derived as follows The last four product terms in the above derivation are the four 1-minterms in the 3-input XOR truth table. For 3 or more inputs, the XOR gate has a value of 1when there is an odd number of 1’s in the inputs, otherwise, it is a 0. Notice also that the truth tables for the 3-input XOR and XNOR gates are identical. It turns out that for an even number of inputs, XOR is the inverse of XNOR, but for an odd number of inputs, XOR is equal to XNOR. All these gates can be interconnected together to form large complex circuits which we call networks. These networks can be described graphically using circuit diagrams, with Boolean expressions or with truth tables. 3.2 Describing Logic Circuits Algebraically Any logic circuit, no matter how complex, may be completely described using the Boolean operations previously defined, because of the OR gate, AND gate, and NOT circuit are the basic building blocks of digital systems. For example consider the circuit shown in Figure 1.3(c). The circuit has three inputs, A, B, and C, and a single output, x. Utilizing the Boolean expression for each gate, we can easily determine the expression for the output. The expression for the AND gate output is written A B. This AND output is connected as an input to the OR gate along with C, another input. The OR gate operates on its inputs such that its output is the OR sum of the inputs. -

The Limits of Logic: Going Beyond Reason in Theology, Faith, and Art”

1 Mark Boone Friday Symposium February 27, 2004 Dallas Baptist University “THE LIMITS OF LOGIC: GOING BEYOND REASON IN THEOLOGY, FAITH, AND ART” INTRODUCTION There is a problem with the way we think. A certain idea has infiltrated our minds, affecting our outlook on the universe. This idea is one of the most destructive of all ideas, for it has affected our conception of many things, including beauty, God, and his relationship with humankind. For the several centuries since the advent of the Modern era, Western civilization has had a problem with logic and human reason. The problem extends from philosophy to theology, art, and science; it affects the daily lives of us all, for the problem is with the way we think; we think that thinking is everything. The problem is that Western civilization has for a long time considered his own human reason to be the ultimate guide to finding truth. The results have been disastrous: at different times and in different places and among people of various different opinions and creeds, the Christian faith has been subsumed under reason, beauty has been thought to be something that a human being can fully understand, and God himself has been held subservient to the human mind. When some people began to realize that reason could not fully grasp all the mysteries of the universe, they did not successfully surrender the false doctrine that had elevated reason so high, and they began to say that it is acceptable for something contrary to the rules of logic to be good. 2 Yet it has not always been this way, and indeed it should not be this way. -

Hardware Abstract the Logic Gates References Results Transistors Through the Years Acknowledgements

The Practical Applications of Logic Gates in Computer Science Courses Presenters: Arash Mahmoudian, Ashley Moser Sponsored by Prof. Heda Samimi ABSTRACT THE LOGIC GATES Logic gates are binary operators used to simulate electronic gates for design of circuits virtually before building them with-real components. These gates are used as an instrumental foundation for digital computers; They help the user control a computer or similar device by controlling the decision making for the hardware. A gate takes in OR GATE AND GATE NOT GATE an input, then it produces an algorithm as to how The OR gate is a logic gate with at least two An AND gate is a consists of at least two A NOT gate, also known as an inverter, has to handle the output. This process prevents the inputs and only one output that performs what inputs and one output that performs what is just a single input with rather simple behavior. user from having to include a microprocessor for is known as logical disjunction, meaning that known as logical conjunction, meaning that A NOT gate performs what is known as logical negation, which means that if its input is true, decision this making. Six of the logic gates used the output of this gate is true when any of its the output of this gate is false if one or more of inputs are true. If all the inputs are false, the an AND gate's inputs are false. Otherwise, if then the output will be false. Likewise, are: the OR gate, AND gate, NOT gate, XOR gate, output of the gate will also be false. -

What Is Neologicism?∗

What is Neologicism? 2 by Zermelo-Fraenkel set theory (ZF). Mathematics, on this view, is just applied set theory. Recently, ‘neologicism’ has emerged, claiming to be a successor to the ∗ What is Neologicism? original project. It was shown to be (relatively) consistent this time and is claimed to be based on logic, or at least logic with analytic truths added. Bernard Linsky Edward N. Zalta However, we argue that there are a variety of positions that might prop- erly be called ‘neologicism’, all of which are in the vicinity of logicism. University of Alberta Stanford University Our project in this paper is to chart this terrain and judge which forms of neologicism succeed and which come closest to the original logicist goals. As we look back at logicism, we shall see that its failure is no longer such a clear-cut matter, nor is it clear-cut that the view which replaced it (that 1. Introduction mathematics is applied set theory) is the proper way to conceive of math- ematics. We shall be arguing for a new version of neologicism, which is Logicism is a thesis about the foundations of mathematics, roughly, that embodied by what we call third-order non-modal object theory. We hope mathematics is derivable from logic alone. It is now widely accepted that to show that this theory offers a version of neologicism that most closely the thesis is false and that the logicist program of the early 20th cen- approximates the main goals of the original logicist program. tury was unsuccessful. Frege’s (1893/1903) system was inconsistent and In the positive view we put forward in what follows, we adopt the dis- the Whitehead and Russell (1910–13) system was not thought to be logic, tinctions drawn in Shapiro 2004, between metaphysical foundations for given its axioms of infinity, reducibility, and choice. -

How to Draw the Right Conclusions Logical Pluralism Without Logical Normativism

How to Draw the Right Conclusions Logical Pluralism without Logical Normativism Christopher Blake-Turner A thesis submitted to the faculty at the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree Master of Arts in the Department of Philosophy in the College of Arts and Sciences. Chapel Hill 2017 Approved by: Gillian Russell Matthew Kotzen John T. Roberts © 2017 Christopher Blake-Turner ALL RIGHTS RESERVED ii ABSTRACT Christopher Blake-Turner: How to Draw the Right Conclusions: Logical Pluralism without Logical Normativism. (Under the direction of Gillian Russell) Logical pluralism is the view that there is more than one relation of logical consequence. Roughly, there are many distinct logics and they’re equally good. Logical normativism is the view that logic is inherently normative. Roughly, consequence relations impose normative constraints on reasoners whether or not they are aiming at truth-preservation. It has widely been assumed that logical pluralism and logical normativism go together. This thesis questions that assumption. I defend an account of logical pluralism without logical normativism. I do so by replacing Beall and Restall’s normative constraint on consequence relations with a constraint concerning epistemic goals. As well as illuminating an important, unnoticed area of dialectical space, I show that distinguishing logical pluralism from logical normativism has two further benefits. First, it helps clarify what’s at stake in debates about pluralism. Second, it provides an elegant response to the most pressing challenge to logical pluralism: the normativity objection. iii ACKNOWLEDGEMENTS I am very grateful to Gillian Russell, Matt Kotzen, and John Roberts for encouraging discussion and thoughtful comments at many stages of this project. -

Solving Logic Problems with a Twist

Transformations Volume 6 Issue 1 Winter 2020 Article 6 11-30-2020 Solving Logic Problems with a Twist Angie Su Nova Southeastern University, [email protected] Bhagi Phuel Chloe Johnson Dylan Mandolini Shawlyn Fleming Follow this and additional works at: https://nsuworks.nova.edu/transformations Part of the Science and Mathematics Education Commons, and the Teacher Education and Professional Development Commons Recommended Citation Su, Angie; Bhagi Phuel; Chloe Johnson; Dylan Mandolini; and Shawlyn Fleming (2020) "Solving Logic Problems with a Twist," Transformations: Vol. 6 : Iss. 1 , Article 6. Available at: https://nsuworks.nova.edu/transformations/vol6/iss1/6 This Article is brought to you for free and open access by the Abraham S. Fischler College of Education at NSUWorks. It has been accepted for inclusion in Transformations by an authorized editor of NSUWorks. For more information, please contact [email protected]. Solving Logic Problems with a Twist Cover Page Footnote This article was originally published in the Dimensions Journal, A publication of the Florida Council of Teachers of Mathematics Journal. This article is available in Transformations: https://nsuworks.nova.edu/transformations/vol6/iss1/6 Su, Hui Fang Huang, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Solving Logic Problems with a Twist Solving Logic Problems with a Twist Hui Fang Huang Su, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Review of Symbolic Logic Aristotle, Greek philosopher and scientist, was a pupil of Plato and asserted that any logical argument is reducible to two premises and a conclusion (Gullberg, 1997). According to classical (Aristotelian) logic, arguments are governed by three fundamental laws: the principle of identity, the principle of the excluded middle, and the principle of contradiction.