MASTER PRODUCT SELECTION GUIDE NOTES Introduction Digital Television and Set–Top Box 1

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

January 1977 I

CALIFORNIA STATE UN:::VERSITY, NORTHRIDGE HICROPROCESSORS / A graduate p~ojc~t report s~~oitted in partial satisfaction of the requirements for the degree of Master of Science in Engineering .. I by Thor,las Carson Hecht ~- .January 1977 i The graduate project report of Thomas Carson Hecht is approved: California State University, Northridge Oitober 1976 ii TABLE OF CONTENTS TITLE PAGE i. 1-.PPROVAL PAGE i.i LIST OF FIGURES i.v ABSTRP.C'I' vii INTRODUCTION 1 INTRODUCTION 1'0 MICROPROCESSORS 3 THE 6800 HINIHAL SYSTEM 7 THE HICROCOMPUTER ... , .. ,~ .. c•<~c•••••••••••••,.tt•••••••.••,•·•••••-~~·•'~••oo 18 }!ICROELECTRONIC P.ESISTOiZS AND RESISTOR TRH'lMING 31 AJ!FL ICATT.O!'·! OF THE HICROCOI'-1PUTER TO LASER TRIH~llNG R),DJIR ERRORS AND THEIR CORRECTION 65 THE ERROR COF,RECI'TON SYSTEM •••••••c••••.,••••••••••••••• .. •-ta•••••·• 69 THE HICROPROCESSOR SYSTEN 34 LIHJ.TATWNS AND ACCURACY 97 SUNNARY 100 APPENDIX A 6800 IN.~)J'RUC.TIO.N S.&T •••••••••••••••••••• 102 APPEND IX E HOTOIWLA 6800 .CI.ROJ LTS -t.~ ...... ~ ... , ............. ~ ............... 105 lJ:'FENDIX C C.ALCJJL.A.TOR .CHIP DATA SH.EET •• , , .•••• , .•••.•••••••••••• llO 'I + .. .;:,. .. t •· II " • • • 115 BIBLlOGR.t,PHY ••••••••• otto'W ...... ll9 Li.i LIST OF FIGURES FIGURE 1: THE 6800 Mli'Hr·L'\L SYSTEH FIGURE 2: OPERATION OF THE ACIA FIGURE 3: OPERATION OF THE PIA FIGURE Lf: BLOCK DIAGRP..H OF THE PIA/CALCULATOR CHIP INTERFACE FIGURE 5: SCHEHATIC AND TRUTH TABLE OF THE PRIOP.ITY ENCODER FIGURE 6: SCHElv!ATIC OF THE QUAD AND FIGURE 7: SCHEHATIC OF 'I'JIE TNTERRUPT PRIORITY CIRCUIT FIGURE 8: LOCATIONS ADDRESSED BY THE MPU FOR DIFFERENT PRIORITY Ii'fTERlWPTS FIGURE 9: .tv1EHORY H1\P OF THE MICROCOl1PUTER FIGURE 10: CALCULATION OF RESISTANCE USING SQUARES AND SHEET RESISTANCE FIGURE 11: DIFFERENT TYPES OF TRIHS FIGURE 12: RESISTANCE AS A FUNCTION OF TRHllviiNG FIGURE 13: PLOT OF % OF INCREASE IN RESISTANCE VS. -

Computer Architectures

Computer Architectures Motorola 68000, 683xx a ColdFire – CISC CPU Principles Demonstrated Czech Technical University in Prague, Faculty of Electrical Engineering AE0B36APO Computer Architectures Ver.1.10 1 Original Desktop/Workstation 680X0 Feature 68000 'EC000 68010 68020 68030 68040 68060 Data bus 16 8/16 16 8/16/32 8/16/32 32 32 Addr bus 23 23 23 32 32 32 32 Misaligned Addr - - - Yes Yes Yes Yes Virtual memory - - Yes Yes Yes Yes Yes Instruct Cache - - 3 256 256 4096 8192 Data Cache - - - - 256 4096 8192 Memory manager 68451 or 68851 68851 Yes Yes Yes ATC entries - - - - 22 64/64 64/64 FPU interface - - - 68881 or 68882 Internal FPU built-in FPU - - - - - Yes Yes Burst Memory - - - - Yes Yes Yes Bus Cycle type asynchronous both synchronous Data Bus Sizing - - - Yes Yes use 68150 Power (watts) 1.2 0.13-0.26 0.13 1.75 2.6 4-6 3.9-4.9 at frequency of 8.0 8-16 8 16-25 16-50 25-40 50-66 MIPS/kDhryst. 1.2/2.1 2.5/4.3 6.5/11 14/23 35/60 100/300 Transistors 68k 84k 190k 273k 1,170k 2,500k Introduction 1979 1982 1984 1987 1991 1994 AE0B36APO Computer Architectures 2 M68xxx/CPU32/ColdFire – Basic Registers Set 31 16 15 8 7 0 User programming D0 D1 model registers D2 D3 DATA REGISTERS D4 D5 D6 D7 16 15 0 A0 A1 A2 A3 ADDRESS REGISTERS A4 A5 A6 16 15 0 A7 (USP) USER STACK POINTER 0 PC PROGRAM COUNTER 15 8 7 0 0 CCR CONDITION CODE REGISTER 31 16 15 0 A7# (SSP) SUPERVISOR STACK Supervisor/system POINTER 15 8 7 0 programing model (CCR) SR STATUS REGISTER 31 0 basic registers VBR VECTOR BASE REGISTER 31 3 2 0 SFC ALTERNATE FUNCTION DFC CODE REGISTERS AE0B36APO Computer Architectures 3 Status Register – Conditional Code Part USER BYTE SYSTEM BYTE (CONDITION CODE REGISTER) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 T1 T0 S 0 0 I2 I1 I0 0 0 0 X N Z V C TRACE INTERRUPT EXTEND ENABLE PRIORITY MASK NEGATIVE SUPERVISOR/USER ZERO STATE OVERFLOW CARRY ● N – negative .. -

RTEMS CPU Supplement Documentation Release 4.11.3 ©Copyright 2016, RTEMS Project (Built 15Th February 2018)

RTEMS CPU Supplement Documentation Release 4.11.3 ©Copyright 2016, RTEMS Project (built 15th February 2018) CONTENTS I RTEMS CPU Architecture Supplement1 1 Preface 5 2 Port Specific Information7 2.1 CPU Model Dependent Features...........................8 2.1.1 CPU Model Name...............................8 2.1.2 Floating Point Unit..............................8 2.2 Multilibs........................................9 2.3 Calling Conventions.................................. 10 2.3.1 Calling Mechanism.............................. 10 2.3.2 Register Usage................................. 10 2.3.3 Parameter Passing............................... 10 2.3.4 User-Provided Routines............................ 10 2.4 Memory Model..................................... 11 2.4.1 Flat Memory Model.............................. 11 2.5 Interrupt Processing.................................. 12 2.5.1 Vectoring of an Interrupt Handler...................... 12 2.5.2 Interrupt Levels................................ 12 2.5.3 Disabling of Interrupts by RTEMS...................... 12 2.6 Default Fatal Error Processing............................. 14 2.7 Symmetric Multiprocessing.............................. 15 2.8 Thread-Local Storage................................. 16 2.9 CPU counter...................................... 17 2.10 Interrupt Profiling................................... 18 2.11 Board Support Packages................................ 19 2.11.1 System Reset................................. 19 3 ARM Specific Information 21 3.1 CPU Model Dependent Features.......................... -

ED135388.Pdf

DOCUMENT RESUME ED 135 388 IB 004 499 AUTHOR Kirby, Paul J.; Gardner, Edward M. Tin! Microcomputer Controlled, interactive Testing Terminal Development. INSTITUTION Air Force Human Resources lab., Lowry AFB, Colo. Technical Training Div. SPONS AGENCY Air Force Human Resources Lab., Brooks AFB, Texas. REPORT NO AIHEI-TR-76-66 PUB DATE Oct 76 NOTE 27p. EDRS PRICE MF-$0.83 HC-$2.06 Plus Postage. DESCRIPTORS Autcinstructional Aids; Computer Programs; *Computer Science; *Individual Tests; Man Machine Systems; Self Pacing Machines; *Testing; *Test Scoring Machines IDENTIFIERS Microcomputers ABSTRACT The evolution of a self-contained test scoring terminal is presented. The rationale for thedesign is presented along with an evolutionary description ofthe requirements for the system. The sequence of software andhardware tools, which were developed in order to build the device, are alsodescribed in this report. The resulting device,which contains an imbedded microcomputer is functionally described and the testingstrategies which it cur.rently supports axe presented.(Author) *********************************************************************** * Dcraents acquired by ERIC include many informalunpublished * *materls not available from other sources. ERICmakes every effort * *to obtain tbe best copyavailable. Nevertheless, items of marginal * *reproducibility are often encountered andthis affects the quality * *of the microfiche and hardcopyxeproductions ERIC makes available * *via the ERIC Document ReproductionService (EDRS). EDRS is not * *responsible -

Technician's Guide to 68HC11 Microcontroller.Pdf

chapter 1 Introduction to Computer Hardware Objectives I ntr odu ct ion to Com put er H ardw are After completing this chapter, you should be able to: ◗ Describe the fundamental elements of every computer system: proces- sor, memory, and input/output ◗ Compare elements of the HC11 block diagram to the fundamentals of every computer system ◗ Describe the use of busses to connect computer elements ◗ Explain the three major functional units of a processor ◗ Illustrate the typical registers inside the processor ◗ List the HC11 processor registers ◗ Discuss the HC11 processor modes ◗ Compare and contrast various memory types ◗ Describe the on-chip memory of the HC11 ◗ Specify input/output functions present on most computers ◗ Use some basic BUFFALO commands to control the EVBU Outline ◗ 1.1 Elements of Every Computer ◗ 1.2 Elements of Processors ◗ 1.3 Introduction to Memory ◗ 1.4 Memory Types ◗ 1.5 Input/Output 1 ◗ 1.6 EVBU/BUFFALO Technician’s Guide to the 68HC11 Microcontroller Introduction Computer systems have been developed for a variety of functions and purposes. General-application desktop machines are the most common. They run a variety of software applications, such as word processing, financial management and data processing. They have all but replaced the typewriter as a necessary business tool. Computers are also present in automobiles, appliances, airplanes and all types of controllers and electromechanical devices. Despite the differences among these computer systems, they all share fundamental components and design. The purpose of this chapter is to provide an understanding of the fundamental components of a computer system. A conceptual presentation regarding the elements of every computer system is made with sufficient detail to establish a foundation for these concepts. -

Gestalt Manager 1

CHAPTER 1 Gestalt Manager 1 This chapter describes how you can use the Gestalt Manager and other system software facilities to investigate the operating environment. You need to know about the 1 operating environment if your application takes advantage of hardware (such as a Gestalt Manager floating-point unit) or software (such as Color QuickDraw) that is not available on all Macintosh computers. You can also use the Gestalt Manager to inform the Operating System that your software is present and to find out about other software registered with the Gestalt Manager. The Gestalt Manager is available in system software versions 6.0.4 and later. The MPW software development system and some other development environments supply code that allows you to use the Gestalt Manager on earlier system software versions; check the documentation provided with your development system. In system software versions earlier than 6.0.4, you can retrieve a limited description of the operating environment with the SysEnvirons function, also described in this chapter. You need to read this chapter if you take advantage of specific hardware or software features that may not be present on all versions of the Macintosh, or if you wish to inform other software that your software is present in the operating environment. This chapter describes how the Gestalt Manager works and then explains how you can ■ determine whether the Gestalt Manager is available ■ call the Gestalt function to investigate the operating environment ■ make information about your own hardware or software available to other applications ■ retrieve a limited description of the operating environment even if the Gestalt Manager is not available About the Gestalt Manager 1 The Macintosh family of computers includes models that use a number of different processors, some accompanied by a floating-point unit (FPU) or memory management unit (MMU). -

From 128K to Quadra: Model by Model

Chapter 12 From 128K to Quadra: Model by Model IN THIS CHAPTER: I What the specs mean I The specs for every Mac model ever made I Secrets of the pre-PowerPC Mac models I Just how much your Mac has devalued Yes, we’ve already been told that we’re nuts to attempt the next two chapters of this book. Since 1984, Apple has created more than 140 different Mac models — including 35 different PowerBooks and 53 different Performas! Each year, Apple piles on another dozen or so new models. By the time you finish reading this page, another Performa model probably will have been born. So, writing a couple of chapters that are supposed to describe every model is an exercise in futility. But we’re going to attempt it anyway, taking the models one by one and tracking their speeds, specs, and life cycles. This chapter will cover all the Apple Macs — both desktop and portable models — from the birth of the original Macintosh 128K to the release of the PowerBook 190, the last Mac ever made that was based on Motorola’s 68000-series processor chip. When you’re finished reading this chapter, you will be one of the few people on Earth who actually knows the difference between a Performa 550, 560, 575, 577, 578, 580, and 588. 375 376 Part II: Secrets of the Machine Chapter 13 will cover every Power Mac — or, more accurately, every PowerPC-based machine (those with four-digit model numbers) — from the first ones released in 1994 to the models released just minutes before this book was printed. -

Numerical Computation Guide

Numerical Computation Guide Sun Microsystems, Inc. 901 San Antonio Road Palo Alto, CA 94303 U.S.A. 650-960-1300 Part No. 806-3568-10 May 2000, Revision A Send comments about this document to: [email protected] Copyright © 2000 Sun Microsystems, Inc., 901 San Antonio Road • Palo Alto, CA 94303-4900 USA. All rights reserved. This product or document is distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape™, Netscape Navigator™, and the Netscape Communications Corporation logo™, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved. Sun, Sun Microsystems, the Sun logo, docs.sun.com, AnswerBook2, Solaris, SunOS, JavaScript, SunExpress, Sun WorkShop, Sun WorkShop Professional, Sun Performance Library, Sun Performance WorkShop, Sun Visual WorkShop, and Forte are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. -

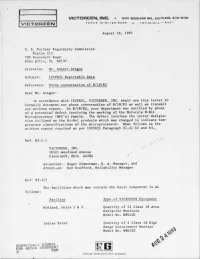

Part 21 Rept Re Marking of Motorola 8-Bit Microprocessor Family

. o *" ']w', ('', , . 1, ;, * , ' i VICTOREEN, INC. - 10101 WDODLAND AVE., CLE(ELAND, DillD 44104 . VICTOREEN "" "*:'''*1'****** = m i n o l a :'' * * * ' August 19, 1983 'i ' . ' U. S. Nuclear Regulatory Commission Region III 799 Roosevelt Road Glen Allyn, IL 60137 . Attentior. Mr. Robert Gregor Subject: 10CFR21 Repertable Data . Reference: Phone conversation of 8/18/83 Dear Mr. Gregor: In accordance with 10CFR21, VICT0REEN, INC. shall use this letter to formally document our phone co'nversation of 8/18/83 as well as transmit our written report. On 8/18/83, your department was notified by phone . of a potential defect involving the marking of the Motorola 8-Bit Microprocessor (MPU's) Family. The defect involves the letter designa- tion utilized on the Hi-Re1 products which was changed to indicate tem- perature classifications of the microprocessor. What follows is the written report required as per 10CFR21 Paragraph 21.21 b2 and b3., , MD Ref: B3.i.) q VICTOREEN, INC. t 10101 Woodland Avenue ,g O-[* Cleveland, Ohio 44104 /k Attention: Roger Zimmerman, Q. A. Manager, and Attention: Ken Stafford, Reliability Manager | | Ref: B3.ii) i The facilities which may contain the basic component is as follows: Facility Type of VICTOREEN Equipment . Midland, Units 1 & 2 Quantity of 12 Class IE Area Radiation Monitors Model No. M861CD Indian Point Ouantity of 2 Class 1E High i Range Containment Monitor Model No. M861CD h , s p 8309070411 830831 g gDRADOCK05000 A shener o obe comoreon sues.o ry | . m . _ _ ._ . d - . P:gs 2 - , ~ . U. S. Nuclear Regulatory Commission , . Region III Clen Allyn, IL 60137 ,. -

A Self-Optimizing Embedded Microprocessor Using a Loop Table

A Self-Optimizing Embedded Microprocessor using a Loop Table for Low Power Frank Vahid* and Ann Gordon-Ross Department of Computer Science and Engineering University of California, Riverside http://www.cs.ucr.edu/~vahid {vahid/ann}@cs.ucr.edu *Also with the Center for Embedded Computer Systems at UC Irvine. ABSTRACT additional transistor capacity is to reduce power in a mass- We describe an approach for a microprocessor to tune itself to its produced embedded microprocessor by, adding tunable fixed application to reduce power in an embedded system. We components to the architecture, and extra circuitry that tunes those define a basic architecture and methodology supporting a components to the particular fixed application. Essentially, the microprocessor self-optimizing mode. We also introduce a loop microprocessor is self-optimizing. A designer using such a part table as a tunable component, although self-optimization can be gets reduced power through some customization while still getting done for other tunable components too. We highlight the benefits of a mass-produced IC. experimental results illustrating good power reductions with no In this paper, we describe a basic architecture and methodology performance penalty. for a self-optimizing microprocessor that tunes itself to an application to reduce power. Such a microprocessor represents an Keywords instance of post-fabrication tuning [16], namely tuning done after System-on-a-chip, self-optimizing architecture, embedded an IC has been fabricated. We introduce self-profiling circuitry systems, parameterized architectures, cores, low-power, tuning, and a designer-controlled self-optimization mode, in which platforms. configurable architectural components would be tuned based on an application’s profile. -

The ZEN of BDM

The ZEN of BDM Craig A. Haller Macraigor Systems Inc. This document may be freely disseminated, electronically or in print, provided its total content is maintained, including the original copyright notice. Introduction You may wonder, why The ZEN of BDM? Easy, BDM (Background Debug Mode) is different from other types of debugging in both implementation and in approach. Once you have a full understanding of how this type of debugging works, the spirit behind it if you will, you can make the most of it. Before we go any further, a note on terminology. “BDM” is Motorola’s term for a method of debugging. It also refers to a hardware port on their microcontroller chips, the “BDM port”. Other chips and other manufacturers use a JTAG port (IBM), a OnCE port (Motorola), an MPSD port (Texas Instruments), etc. (more on these later). The type of debugging we will be discussing is sometimes known as “BDM debugging” even though it may use a JTAG port! For clarity, I will refer to it as “on-chip debugging” or OCD. This will include all the various methods of using resources on the chip that are put there to enable complete software debug and aid in hardware debug. This includes processors from IBM, TI, Analog Devices, Motorola, and others. This paper is an overview of OCD debugging, what it is, and how to use it most effectively. A certain familiarity with debugging is assumed, but novice through expert in microprocessor/microcontroller design and debug will gain much from its reading. Throughout this paper I will try to be as specific as possible when it relates to how different chips implement this type of debugging. -

Embedded Systems

EMBEDDED SOFTWARE & SYSTEMS DEVELOPMENT HCL ENGINEERING AND R&D SERVICES Innovation Simplified Embedded Software & Systems Development at HCL HCL is a leader in developing embedded software and systems for various industries and domains. We have expertise in safety-critical embedded systems with more than 2000 person years of cumulative experience in developing small footprint and safety-critical embedded systems for Medical Devices, Automotive Electronics and Aircraft Components. We use our DSP expertise and IPs to develop fast embedded middleware, rich applications and interactive GUI for consumer electronics, computer peripherals and telecom products. Our embedded systems group comprises of a large talent pool of engineers and equipped with competencies in a range of programming tools, microprocessors and real-time operating systems. HCL has executed turnkey development projects for new products as well as provided discrete services for existing products. Our embedded product lifecycle services provide • Feasibility study, modeling & design, development for new product development • Re-development & re-engineering, technology adaptation for new adaptations. • Lifecycle enhancements, defect tracking and fixing for product sustenance • Test plan design, test automation and scripting for testing and verification Using our unparalleled expertise across various domains, HCL tailors its embedded services to meet the unique challenges of different industries Innovation Partner to Global Fortune companies 2000+ Service person years of Offerings