Birthing the Computer

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1 Oral History Interview with Brian Randell January 7, 2021 Via Zoom

Oral History Interview with Brian Randell January 7, 2021 Via Zoom Conducted by William Aspray Charles Babbage Institute 1 Abstract Brian Randell tells about his upbringing and his work at English Electric, IBM, and Newcastle University. The primary topic of the interview is his work in the history of computing. He discusses his discovery of the Irish computer pioneer Percy Ludgate, the preparation of his edited volume The Origins of Digital Computers, various lectures he has given on the history of computing, his PhD supervision of Martin Campbell-Kelly, the Computer History Museum, his contribution to the second edition of A Computer Perspective, and his involvement in making public the World War 2 Bletchley Park Colossus code- breaking machines, among other topics. This interview is part of a series of interviews on the early history of the history of computing. Keywords: English Electric, IBM, Newcastle University, Bletchley Park, Martin Campbell-Kelly, Computer History Museum, Jim Horning, Gwen Bell, Gordon Bell, Enigma machine, Curta (calculating device), Charles and Ray Eames, I. Bernard Cohen, Charles Babbage, Percy Ludgate. 2 Aspray: This is an interview on the 7th of January 2021 with Brian Randell. The interviewer is William Aspray. We’re doing this interview via Zoom. Brian, could you briefly talk about when and where you were born, a little bit about your growing up and your interests during that time, all the way through your formal education? Randell: Ok. I was born in 1936 in Cardiff, Wales. Went to school, high school, there. In retrospect, one of the things I missed out then was learning or being taught Welsh. -

May 21St at the Time, the EDSAC Used IBM 726 Three Small Cathode Ray Tube Börje Langefors Screens to Display the State of Its Announced Memory

it played tic-tac-toe (known as Noughts and Crosses in the UK). May 21st At the time, the EDSAC used IBM 726 three small cathode ray tube Börje Langefors screens to display the state of its Announced memory. Each one could draw a May 21, 1952 Born: May 21, 1915; grid of 35 x 16 dots. Douglas re- purposed one of them for his Ystad, Sweden The IBM 726 was the company’s game, and obtained input (i.e. Died: Dec. 13, 2009 first magnetic tape unit, where to place a nought or intended for use with the Langefors developed the cross) via EDSAC’s rotary recently announced IBM 701 ‘infological equation’ in 1980, controller. [April 7], the company’s first which describes the difference electronic computer. between information and data in terms of additional semantic The 726 utilized half-inch tapes background and a with seven tracks. Six were for communication time interval. the data and the seventh was employed as a parity track. Langefors joined SAAB, the Some tapes were 1,200 feet long, Swedish aerospace and defense could store 2.3 MB of data, and company, in 1949 where he IBM claimed that just one could utilized analog devices for replace 12,500 punch cards. calculating wing stresses. The need for more powerful tools The drive could write 100 became evident, and the only characters per inch on a tape Swedish computer of the time, EDSAC CRT Tubes. Computer and read 75 inches per second. the BESK [April 1], was Lab, Univ. of Cambridge. CC BY To withstand the system’s fast insufficient for the task. -

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

Technical Details of the Elliott 152 and 153

Appendix 1 Technical Details of the Elliott 152 and 153 Introduction The Elliott 152 computer was part of the Admiralty’s MRS5 (medium range system 5) naval gunnery project, described in Chap. 2. The Elliott 153 computer, also known as the D/F (direction-finding) computer, was built for GCHQ and the Admiralty as described in Chap. 3. The information in this appendix is intended to supplement the overall descriptions of the machines as given in Chaps. 2 and 3. A1.1 The Elliott 152 Work on the MRS5 contract at Borehamwood began in October 1946 and was essen- tially finished in 1950. Novel target-tracking radar was at the heart of the project, the radar being synchronized to the computer’s clock. In his enthusiasm for perfecting the radar technology, John Coales seems to have spent little time on what we would now call an overall systems design. When Harry Carpenter joined the staff of the Computing Division at Borehamwood on 1 January 1949, he recalls that nobody had yet defined the way in which the control program, running on the 152 computer, would interface with guns and radar. Furthermore, nobody yet appeared to be working on the computational algorithms necessary for three-dimensional trajectory predic- tion. As for the guns that the MRS5 system was intended to control, not even the basic ballistics parameters seemed to be known with any accuracy at Borehamwood [1, 2]. A1.1.1 Communication and Data-Rate The physical separation, between radar in the Borehamwood car park and digital computer in the laboratory, necessitated an interconnecting cable of about 150 m in length. -

An Early Program Proof by Alan Turing F

An Early Program Proof by Alan Turing F. L. MORRIS AND C. B. JONES The paper reproduces, with typographical corrections and comments, a 7 949 paper by Alan Turing that foreshadows much subsequent work in program proving. Categories and Subject Descriptors: 0.2.4 [Software Engineeringj- correctness proofs; F.3.1 [Logics and Meanings of Programs]-assertions; K.2 [History of Computing]-software General Terms: Verification Additional Key Words and Phrases: A. M. Turing Introduction The standard references for work on program proofs b) have been omitted in the commentary, and ten attribute the early statement of direction to John other identifiers are written incorrectly. It would ap- McCarthy (e.g., McCarthy 1963); the first workable pear to be worth correcting these errors and com- methods to Peter Naur (1966) and Robert Floyd menting on the proof from the viewpoint of subse- (1967); and the provision of more formal systems to quent work on program proofs. C. A. R. Hoare (1969) and Edsger Dijkstra (1976). The Turing delivered this paper in June 1949, at the early papers of some of the computing pioneers, how- inaugural conference of the EDSAC, the computer at ever, show an awareness of the need for proofs of Cambridge University built under the direction of program correctness and even present workable meth- Maurice V. Wilkes. Turing had been writing programs ods (e.g., Goldstine and von Neumann 1947; Turing for an electronic computer since the end of 1945-at 1949). first for the proposed ACE, the computer project at the The 1949 paper by Alan M. -

Computer Organization & Architecture Eie

COMPUTER ORGANIZATION & ARCHITECTURE EIE 411 Course Lecturer: Engr Banji Adedayo. Reg COREN. The characteristics of different computers vary considerably from category to category. Computers for data processing activities have different features than those with scientific features. Even computers configured within the same application area have variations in design. Computer architecture is the science of integrating those components to achieve a level of functionality and performance. It is logical organization or designs of the hardware that make up the computer system. The internal organization of a digital system is defined by the sequence of micro operations it performs on the data stored in its registers. The internal structure of a MICRO-PROCESSOR is called its architecture and includes the number lay out and functionality of registers, memory cell, decoders, controllers and clocks. HISTORY OF COMPUTER HARDWARE The first use of the word ‘Computer’ was recorded in 1613, referring to a person who carried out calculation or computation. A brief History: Computer as we all know 2day had its beginning with 19th century English Mathematics Professor named Chales Babage. He designed the analytical engine and it was this design that the basic frame work of the computer of today are based on. 1st Generation 1937-1946 The first electronic digital computer was built by Dr John V. Atanasoff & Berry Cliford (ABC). In 1943 an electronic computer named colossus was built for military. 1946 – The first general purpose digital computer- the Electronic Numerical Integrator and computer (ENIAC) was built. This computer weighed 30 tons and had 18,000 vacuum tubes which were used for processing. -

Information Technology 3 and 4/1998. Emerging

OCCASION This publication has been made available to the public on the occasion of the 50th anniversary of the United Nations Industrial Development Organisation. DISCLAIMER This document has been produced without formal United Nations editing. The designations employed and the presentation of the material in this document do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations Industrial Development Organization (UNIDO) concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries, or its economic system or degree of development. Designations such as “developed”, “industrialized” and “developing” are intended for statistical convenience and do not necessarily express a judgment about the stage reached by a particular country or area in the development process. Mention of firm names or commercial products does not constitute an endorsement by UNIDO. FAIR USE POLICY Any part of this publication may be quoted and referenced for educational and research purposes without additional permission from UNIDO. However, those who make use of quoting and referencing this publication are requested to follow the Fair Use Policy of giving due credit to UNIDO. CONTACT Please contact [email protected] for further information concerning UNIDO publications. For more information about UNIDO, please visit us at www.unido.org UNITED NATIONS INDUSTRIAL DEVELOPMENT ORGANIZATION Vienna International Centre, P.O. Box 300, 1400 Vienna, Austria Tel: (+43-1) 26026-0 · www.unido.org · [email protected] EMERGING TECHNOLOGY SERIES 3 and 4/1998 Information Technology UNITED NATIONS INDUSTRIAL DEVELOPMENT ORGANIZATION Vienna, 2000 EMERGING TO OUR READERS TECHNOLOGY SERIES Of special interest in this issue of Emerging Technology Series: Information T~chn~~ogy is the focus on a meeting that took INFORMATION place from 2n to 4 November 1998, in Bangalore, India. -

Computers and Automation

. 7 .7 BP S' J I i2z7itltJ2f computers and automation COMPUTERS AND WAR SAFETY CONTROL A PICTORIAL REPORT ON COMPUTER APPLICATIONS JANUARY 1962 / • Vol. 11 - No.1 GET RESULTS AND RELAXATION .. DIVIDENDS FROM STATISTICAL'S DATA-PROCESSING • oj ~/ si ---0--- rr e~ /~ When data-processing problems s( put the pressure on you, you'll find n the "safety valve" you need at q STATISTICAL. A wealth of experience is always ready to go to work for you "0: here. Behind every assignment is a searching understanding of management problems and solutions ... gained in serving America's top companies since 1933. From this experience comes the consistently-high quality service you would expect from America's oldest and largest independent data-processing and computer service. Sophisticated methods. Responsible personnel. The latest electronic equipment. Coast-to-coast facilities. Advantages like these add up to "know-how" and TABULATING CORPORATION C "show-how" that can not be acquired overnight. il NATIONAL HEADQUARTERS n This experience-in-depth service is available to 104 South Michigan Avenue-Chicago 3, Illinois a you day or night. A call to our m~arest OFFICES IN PRINCIPAL CITIES - COAST TO COAST data-processing and computer center will bring you the results you want ... and relaxation. ,,1/ -/p~ THE STATISTICAL MARK OF EXCELLENCE I 2 CO~IPUTERS and AUTOMATION for January, 1962 c ester, leI. / Park, ~. Y. Hyde U. S. 'J". Y. geles, City, ment. Lynn- Lab., :trical Alto, \rich. bury, Mass. '" Co., ~ssing Iberg, Ither, Icker- Ger- IS. Abbe 1 Mi- I des -- / "mus, Tele- data Alto, \Iich. -

History of Computer Science from Wikipedia, the Free Encyclopedia

History of computer science From Wikipedia, the free encyclopedia The history of computer science began long before the modern discipline of computer science that emerged in the 20th century, and hinted at in the centuries prior. The progression, from mechanical inventions and mathematical theories towards the modern concepts and machines, formed a major academic field and the basis of a massive worldwide industry.[1] Contents 1 Early history 1.1 Binary logic 1.2 Birth of computer 2 Emergence of a discipline 2.1 Charles Babbage and Ada Lovelace 2.2 Alan Turing and the Turing Machine 2.3 Shannon and information theory 2.4 Wiener and cybernetics 2.5 John von Neumann and the von Neumann architecture 3 See also 4 Notes 5 Sources 6 Further reading 7 External links Early history The earliest known as tool for use in computation was the abacus, developed in period 2700–2300 BCE in Sumer . The Sumerians' abacus consisted of a table of successive columns which delimited the successive orders of magnitude of their sexagesimal number system.[2] Its original style of usage was by lines drawn in sand with pebbles . Abaci of a more modern design are still used as calculation tools today.[3] The Antikythera mechanism is believed to be the earliest known mechanical analog computer.[4] It was designed to calculate astronomical positions. It was discovered in 1901 in the Antikythera wreck off the Greek island of Antikythera, between Kythera and Crete, and has been dated to c. 100 BCE. Technological artifacts of similar complexity did not reappear until the 14th century, when mechanical astronomical clocks appeared in Europe.[5] Mechanical analog computing devices appeared a thousand years later in the medieval Islamic world. -

Jan. 27Th SSEC Seeber and Hamilton Had Tried to Persuade Howard Aiken Jan

some aspects of the SSEC's operation still used plugboards. Jan. 27th SSEC Seeber and Hamilton had tried to persuade Howard Aiken Jan. 27 (24 ??), 1948 [March 8] to make the Harvard William K. English Mark II a stored program IBM’s Selective Sequence machine. Aiken wasn’t Born: Jan. 27, 1929; Electronic Calculator (SSEC) was interested, but Thomas Watson Lexington, Kentucky built at its Endicott facility in Sr. [Feb 17] was persuaded with Died: July 26, 2020 1946-47 under the direction of regards the SSEC, especially Wallace Eckert [June 19], Robert English and Douglas Engelbart since he was still upset over his (Rex) Seeber, Frank E. Hamilton, [Jan 30] share credit for creating altercation with Aiken during and other Watson Scientific the first computer mouse [Nov the dedication of the Harvard Computing Lab [Feb 6] staff. 14]. English built the initial Mark I. prototype in 1964 based on It contained 21,400 relays, The SSEC occupied three sides of Engelbart’s notes, and was its 12,500 vacuum tubes, and could a large room on the ground floor first user. performed 14-by-14 decimal of IBM’s headquarters at 590 multiplication in one-fiftieth of a English was Engelbart’s chief Madison Avenue in NYC, where second, and division in one- hardware architect. He led the it was visible to people walking thirtieth of a second, making it 1965 NASA project to find the by on the street. Herbert Grosch around 250 times faster than the best way to select a point on a [Sept 13] estimated its Harvard Mark I [Aug 7]. -

Computer Development at the National Bureau of Standards

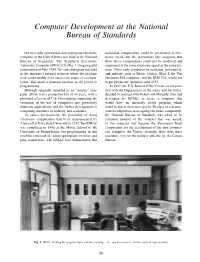

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

Simon E. Gluck Collection of Photographs of EDVAC and MSAC Computers 1990.232

Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 This finding aid was produced using ArchivesSpace on September 19, 2021. Description is written in: English. Describing Archives: A Content Standard Audiovisual Collections PO Box 3630 Wilmington, Delaware 19807 [email protected] URL: http://www.hagley.org/library Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 Table of Contents Summary Information .................................................................................................................................... 3 Biographical Note .......................................................................................................................................... 3 Scope and Content ......................................................................................................................................... 4 Administrative Information ............................................................................................................................ 4 Related Materials ........................................................................................................................................... 5 Controlled Access Headings .......................................................................................................................... 5 Additonal Extent Statement ........................................................................................................................... 5 - Page 2 - Simon E. Gluck collection