Operator Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ME430 Mechatronics Lab 2: Transistors, H-Bridges, and Motors

Name ____________________________________ Name ____________________________________ ME430 Mechatronics Lab 2: Transistors, H‐Bridges, and motors The lab team has demonstrated: Part (A) Driving LEDs and DC Motors by Sourcing and Sinking Current from a Logic Gate ______________ Sourcing Current ______________ Sinking Current Part (B) Driving DC Motors using Logic Gates and Transistors ______________ NPN BJT transistor ______________ N‐channel MOSFET transistor ______________ Darlington Chip (ULN2003) Part (C) Using 12 Volt Power Supplies to Drive Lamps and Fans ______________ MOSFETs ______________ BJTs ______________ Darlingtons Part (D) Using a Darlington to drive multiple LEDs ______________ Dancing lights Part (E) Bi‐directional Control of Motors with H‐Bridge chips ______________ DC Motor with bi‐directional 5V drive circuit ______________ Linear actuator DC motor with bi‐directional 12V drive circuit ______________ Stepper Motor at 5V with 2 sets of bi‐directional phases ME430 Mechatronics: Lab 2 1 Part (A) Driving LEDs and DC Motors by Sourcing and Sinking Current from a Logic Gate In the “Intro to Transistors” video lecture, you also learned about sourcing and sinking current from a logic gate. Sinking the current allows much higher current levels. In this part we would like to build the two configurations and verify that they work. (1) Sourcing Current First, rebuild the simple current sourcing circuit you built for the beginning of Lab 1. Make sure that one works before you move on. Recall that it looks like We would like to modify the circuit to also drive (by sourcing the current from the 7404) a DC (brushed) motor. These are the ordinary‐looking silver‐grey motors. -

2N6294 Silicon NPN Transistor Darlington Power Amplifier, Switch TO−66 Type Package

2N6294 Silicon NPN Transistor Darlington Power Amplifier, Switch TO−66 Type Package Description: The 2N6294 silicon NPN Darlington transistor is a TO−66 type case designed for general purpose amplifier, low−frequency switching and hammer driver applications. Features: D High DC Current Gain: hFE = 3000 Typ @ IC = 2A D Low Collector−Emitter Saturation Voltage: VCE(sat) = 2V Max @ IC = 2A D Collector−Emitter Sustaining Voltage: VCEO(sus) = 60V Min D Monolithic Construction with Built−In Base−Emitter Shunt Resistors Absolute Maximum Ratings: Collector−Emitter Voltage, VCEO ...................................................... 60V Collector−Base Voltage, VCB ......................................................... 60V Emitter−Base Voltage, VEB ........................................................... 5V Collector Current, IC Continuous ................................................................... 4A Peak ........................................................................ 8A Base Current, IB ................................................................. 80mA Total Power Dissipation (TC = +25C), PD ............................................ 50W Derate Above 25C..................................................... 0.286W/C Operating Junction Temperature Range, TJ ..................................−65 to +200C Storage Temperature Range, Tstg ..........................................−65 to +200C Thermal Resistance, Junction−to−Case, RthJC ..................................... 3.5C/W Electrical Characteristics: (TC = +25C unless -

ULN2803A Darlington Transistor Arrays Datasheet

Product Order Technical Tools & Support & Folder Now Documents Software Community ULN2803A SLRS049H –FEBRUARY 1997–REVISED FEBRUARY 2017 ULN2803A Darlington Transistor Arrays 1 Features 3 Description The ULN2803A device is a 50 V, 500 mA Darlington 1• 500-mA-Rated Collector Current (Single Output) transistor array. The device consists of eight NPN Darlington pairs that feature high-voltage outputs with • High-Voltage Outputs: 50 V common-cathode clamp diodes for switching • Output Clamp Diodes inductive loads. The collector-current rating of each • Inputs Compatible With Various Types of Logic Darlington pair is 500 mA. The Darlington pairs may be connected in parallel for higher current capability. 2 Applications Applications include relay drivers, hammer drivers, • Relay Drivers lamp drivers, display drivers (LED and gas discharge), line drivers, and logic buffers. The • Hammer Drivers ULN2803A device has a 2.7-kΩ series base resistor • Lamp Drivers for each Darlington pair for operation directly with • Display Drivers (LED and Gas Discharge) TTL or 5-V CMOS devices. • Line Drivers Device Information(1) • Logic Buffers PART NUMBER PACKAGE BODY SIZE (NOM) • Stepper Motors ULN2803ADW SOIC (18) 11.55 mm × 7.50 mm • IP Camera (1) For all available packages, see the orderable addendum at • HVAC Valve and LED Dot Matrix the end of the data sheet. Logic Diagram 1 18 1B 1C 2 17 2B 2C 3 16 3B 3C 4 15 4B 4C 5 14 5B 5C 6 13 6B 6C 7 12 7B 7C 8 11 8B 8C 10 COM 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. -

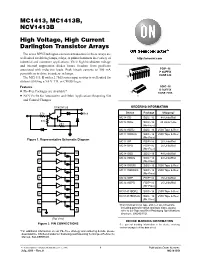

MC1413, MC1413B, NCV1413B High Voltage, High Current Darlington Transistor Arrays

MC1413, MC1413B, NCV1413B High Voltage, High Current Darlington Transistor Arrays The seven NPN Darlington connected transistors in these arrays are well suited for driving lamps, relays, or printer hammers in a variety of http://onsemi.com industrial and consumer applications. Their high breakdown voltage and internal suppression diodes insure freedom from problems associated with inductive loads. Peak inrush currents to 500 mA PDIP−16 P SUFFIX permit them to drive incandescent lamps. CASE 648 The MC1413, B with a 2.7 kW series input resistor is well suited for 16 systems utilizing a 5.0 V TTL or CMOS Logic. 1 Features SOIC−16 • Pb−Free Packages are Available* D SUFFIX 16 CASE 751B • NCV Prefix for Automotive and Other Applications Requiring Site 1 and Control Changes 1/7 MC1413, B ORDERING INFORMATION † 2.7 k Pin 9 Device Package Shipping MC1413D SOIC−16 48 Units/Rail 5.0 k MC1413DG SOIC−16 48 Units/Tube 3.0 k (Pb−Free) MC1413DR2 SOIC−16 2500 Tape & Reel MC1413DR2G SOIC−16 2500 Tape & Reel (Pb−Free) Figure 1. Representative Schematic Diagram MC1413P PDIP−16 25 Units/Rail MC1413PG PDIP−16 25 Units/Rail (Pb−Free) 1 16 MC1413BD SOIC−16 48 Units/Rail MC1413BDG SOIC−16 48 Units/Rail 2 15 (Pb−Free) MC1413BDR2 SOIC−16 2500 Tape & Reel 3 14 MC1413BDR2G SOIC−16 2500 Tape & Reel (Pb−Free) 4 13 MC1413BP PDIP−16 25 Units/Rail MC1413BPG PDIP−16 25 Units/Rail 5 12 (Pb−Free) NCV1413BDR2 SOIC−16 2500 Tape & Reel 6 11 NCV1413BDR2G SOIC−16 2500 Tape & Reel (Pb−Free) 7 10 †For information on tape and reel specifications, including part orientation and tape sizes, please 8 9 refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. -

Darlington Class Ab Pushpull Amplifier

© 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company DARLINGTON CLASS AB PUSHPULL AMPLIFIER • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Push Pull Amplifier When an amplifier is biased at cutoff so that it operates in the linear region for 180 degree of the input cycle and is in cutoff for 180 degree, it is a class B amplifier. Class AB amplifiers are biased to conduct for slightly more than 180 degree. The primary advantage of a class B or class AB amplifier over a class A amplifier is that either one is more efficient than a class A amplifier; you can get more output power for a given amount of input power. A disadvantage of class B or class AB is that it is more difficult to implement the circuit in order to get a linear reproduction of the input waveform. The term push-pull refers to a common type of class B or class AB amplifier circuit in which two transistors are used on alternating half- cycles to reproduce the input waveform at the output. • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Darlington Push Pull Amplifier The complementary Darlington, also known as the Sziklai pair, it is similar to the traditional Darlington pair except it uses complementary transistors (one npn and one pnp). The complementary Darlington is used when it is determined that output power transistors of the same type should be used (both npn or both pnp). Class AB push-pull amplifier consists of two npn output power transistors, The upper part of the push-pull configuration is a traditional Darlington, and the lower part is a complementary Darlington. -

Products Catalog Index

Products Catalog Index PART NO. MANUFACTURER DESCRIPTION URL PRICE NRSA471M25V10x16TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA471M25V10x16TRF-datasheet.html QUOTE NRSA471M35V10x20TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA471M35V10x20TRF-datasheet.html QUOTE NRSA472M10V16x25TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA472M10V16x25TRF-datasheet.html QUOTE NRSA472M16V16x31TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA472M16V16x31TRF-datasheet.html QUOTE NRSA472M25V18x36TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA472M25V18x36TRF-datasheet.html QUOTE NRSA472M35V22x36TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA472M35V22x36TRF-datasheet.html QUOTE NRSA472M50V22x42TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA472M50V22x42TRF-datasheet.html QUOTE NRSA4R7M100V5x11TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA4R7M100V5x11TRF-datasheet.html QUOTE NRSA4R7M50V5x11TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA4R7M50V5x11TRF-datasheet.html QUOTE NRSA682M10V16x31TRF NIC Components Miniature Aluminum Electrolytic Capacitor http://www.searchdatasheet.com/NRSA682M10V16x31TRF-datasheet.html QUOTE NRSZ4R7M50V5x11 -

Design of a 100W Power Amplifier with Darlington Complementary Symmetry Output Power Transistor

UNIVERSITY OF NAIROBI FACULTY OF ENGINEERING DEPARTMENT OF ELECTRICAL AND INFORMATION ENGINEERING DESIGN OF A 100W POWER AMPLIFIER WITH DARLINGTON COMPLEMENTARY SYMMETRY OUTPUT POWER TRANSISTOR PROJECT INDEX: 113 SUBMITTED BY: KOLL JACKSON RISONA F17/37338/2010 SUPERVISOR: MR. S. L OGABA EXAMINER: PROF ABUNGU PROJECT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE AWARD OF THE DEGREE OF BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING OF THE UNIVERSITY OF NAIROBI 2016 i DECLARATION OF ORIGINALITY I, KOLL JACKSON RISONA (F17/37338/2010), hereby declare that this project is my original work. To the best of my knowledge, the work presented here has not been presented for a degree in any other Institution of Higher Learning. ………………………………………… ………………… Name of student Date This project has been submitted for examination with my approval as university supervisor. ………………………………………… ………………… Name of supervisor Date ii DEDICATION I dedicate this project to my parents Mr. and Mrs. John Kol ole Sawi, my siblings and friends for their continued and undying support throughout this journey and I am forever grateful for the opportunity they have given me to achieve my dreams. iii ACKNOWLEDGEMENT I would like to express my gratitude towards my project supervisor Mr. S.L. Ogaba of The Nairobi University and my colleagues for their guidance and constant supervision as well as providing necessary information regarding the project and also for their support in completing the project. I am also grateful to electronics lab technicians for giving me permission to use their facilities. iv ABSTRACT An amplifier is an electronic device used to magnify the value of a signal. -

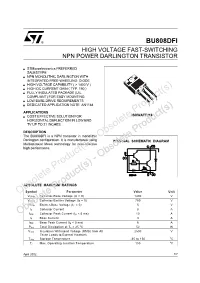

High Voltage Fast-Switching Npn Power Darlington Transistor

® BU808DFI HIGH VOLTAGE FAST-SWITCHING NPN POWER DARLINGTON TRANSISTOR ■ STMicroelectronics PREFERRED SALESTYPE ■ NPN MONOLITHIC DARLINGTON WITH INTEGRATED FREE-WHEELING DIODE ■ HIGH VOLTAGE CAPABILITY ( > 1400 V ) ■ HIGH DC CURRENT GAIN ( TYP. 150 ) ■ FULLY INSULATED PACKAGE (U.L. COMPLIANT) FOR EASY MOUNTING 3 ■ LOW BASE-DRIVE REQUIREMENTS 2 ■ DEDICATED APPLICATION NOTE AN1184 1 APPLICATIONS ISOWATT218 ■ COST EFFECTIVE SOLUTION FOR HORIZONTAL DEFLECTION IN LOW END TV UP TO 21 INCHES. DESCRIPTION The BU808DFI is a NPN transistor in monolithic Darlington configuration. It is manufactured using INTERNAL SCHEMATIC DIAGRAM Multiepitaxial Mesa technology for cost-effective high performance. ABSOLUTE MAXIMUM RATINGS Symbol Parameter Value Unit VCBO Collector-Base Voltage (IE = 0) 1400 V ObsoleteVCEO Collector-Emitter Product(s) Voltage (IB = 0) - Obsolete Product(s) 700 V VEBO Emitter-Base Voltage (IC = 0) 5 V IC Collector Current 8 A ObsoleteICM Collector PeakProduct(s) Current (tp < 5 ms) - Obsolete Product(s) 10 A IB Base Current 3 A IBM Base Peak Current (tp < 5 ms) 6 A o Ptot Total Dissipation at Tc = 25 C52W Visol Insulation Withstand Voltage (RMS) from All 2500 V Three Leads to Exernal Heatsink o Tstg Storage Temperature -65 to 150 C o Tj Max. Operating Junction Temperature 150 C April 2002 1/7 BU808DFI THERMAL DATA o Rthj-case Thermal Resistance Junction-case Max 2.4 C/W o ELECTRICAL CHARACTERISTICS (Tcase = 25 C unless otherwise specified) Symbol Parameter Test Conditions Min. Typ. Max. Unit ICES Collector Cut-off VCE = 1400 V 400 -

I I Jun 1 7 1965

TEXAS INSTRUMENTS INCORPORATELJ I Semiconductor-Components Division I I I P.O. Box 5012 i GPO PRICE $ 1 Dallas, Texas, 75222 CFSTI PRICE(S) $ ~ 0 I Hard copy (HC) Microfiche (MF) TECHNICAL SUMMARY REPORT ff 653 July65 c ON Design, Development and Delivery on One (1) Breadboard Model and Three (3) Production Units of a 75 VA Integrated Static Inverter (27 April 1965 to 27 May 1965) Contract No. NAS8-11925 11 June 1965 JUN 17 1965 t3-~ DDC-IRA E Prepared for National Aeronautics and Space Administration George C. Marshall Space Flight Center Hunts vi 11e, Alabama l- - TECHNICAL DISCUSSION A, Proqress Report for Month of May, 1965 1. Power Supply System A discrete component breadboard version of the inverter and output filter portion of the power supply has been built and tested for various loading conditions. A variable dc la!, supply and a pulse'generator were used to simulate the dc regulator and oscillator/countdown circuit, respectively. The Johnson counter has been built with SN530 flip flops. The breadboard model was built with discrete Darlington power transistors instead of a single power transistor and integrated circuit driver after efficiency calculations indicated this was the best approach. Work has also begun on the regulator. From efficiency considerations a "switching" regulator is deemed necessary. One approach is in block diagram form and a second straightforward technique is presently being breadboarded . Tentative specifications have been submitted to the device design enqineers on the power switches and the integrated counters. Oscillator specifications have been forwarded to two manufacturers of temperature compensated crystal oscillators. -

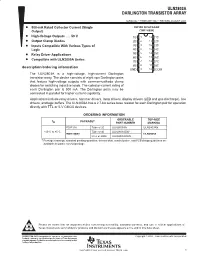

ULN2803A Is a High-Voltage, High-Current Darlington Transistor Array

ULN2803A DARLINGTON TRANSISTOR ARRAY SLRS049C − FEBRUARY1997 − REVISED AUGUST 2004 D 500-mA Rated Collector Current (Single DW OR N PACKAGE Output) (TOP VIEW) D High-Voltage Outputs ...50 V 1B 1 18 1C D Output Clamp Diodes 2B 2 17 2C D Inputs Compatible With Various Types of 3B 3 16 3C Logic 4B 4 15 4C D Relay Driver Applications 5B 5 14 5C 6B 6 13 6C D Compatible with ULN2800A Series 7 12 7B 7C 8 11 description/ordering information 8B 8C GND 9 10 COM The ULN2803A is a high-voltage, high-current Darlington transistor array. The device consists of eight npn Darlington pairs that feature high-voltage outputs with common-cathode clamp diodes for switching inductive loads. The collector-current rating of each Darlington pair is 500 mA. The Darlington pairs may be connected in parallel for higher current capability. Applications include relay drivers, hammer drivers, lamp drivers, display drivers (LED and gas discharge), line drivers, and logic buffers. The ULN2803A has a 2.7-kΩ series base resistor for each Darlington pair for operation directly with TTL or 5-V CMOS devices. ORDERING INFORMATION ORDERABLE TOP-SIDE T PACKAGE† A PART NUMBER MARKING PDIP (N) Tube of 20 ULN2803AN ULN2803AN −40°C to 85°C Tube of 40 ULN2803ADW SOIC (DW) ULN2803A Reel of 2000 ULN2003ADWR † Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. -

1.ABSTRACT Sound Operated Switch Is One of the Interesting Applications of 555 Timer IC. the Circuit Uses A555 Timer IC and Transistor BC547 for Its Operation

1.ABSTRACT Sound operated switch is one of the interesting applications of 555 timer IC. The circuit uses a555 timer IC and transistor BC547 for its operation. The electrets microphone is used to provide the pulse to the 555 timer. The operation is simple. Clap and the lamp turns on. Clap again it turns off.The electrets microphone picks up the sound of your claps, coughs, and the sound of that knocked off the table. It produces a small electrical signal which is amplified by the succeeding transistor stage.Two transistor cross connected as a bistable multivibrator change state at each signal. One of thesetransistors drives a heavier transistor which controls a lamp.The transistor type is not critical and any n-p-n silicon transistors can be used. 2. INTRODUCTION Clap switch is an beginners project done using 555 timer IC. Its application is interesting thatwe can switch on an off by just clapping the hands. Simply by lying on the bed even we can switch on and off the light. The circuit which is provided in this report is the most simple andeconomical circuit for a clap switch. Since it uses a simple condenser mike to produce the pulsesignal more voltage is not necessary. It can be used for controlling ornamental lightning circuit COMPONENTS USED MICROPHONE: Function of microphone :it is a transducer which convert the energy from one form to another form . it convert sound energy to electrical energy Types of microphones microphones were not created equal. Microphones fall into two overarching categories, dynamic and condenser microphones. -

Ctg Product List

Product List Crestwood Technology Group 914.779.3500 | [email protected] CTGNOW.com Any part, any platform, we can help. Here is a quick overview of parts and material we provide. Expendables Rotables ATA Chapters Actives INTEGRATED CIRCUITS Batteries Actuators ATA Chapters AC to DC Switching Converters Bonding Leads Air Regulators Accessory Gearboxes Analog Cable Assemblies APUs Air Analog – Digital Converter Connectors Ballast Units Air Conditioning Angular and linear Position Sensors Contacts Boroscopes Airborn Auxiliary Power Appdlication Processor and SOC Fans Cargo Liners Auto Flight Audio Processor Fasteners Cargo Nets Central Maintenance System Controllers Filters Cargo Panels Communications Converters Hardware Cockpit Avionics Doors CPLD Inductors Composites Electrical Power CPUs Lamps/LEDs Compressors Engine Controls Current miters Placards/Decals Disks Engine Exhaust Current Mode PWM Controller Relays Displays Engine Fuel and Control Current Sensor Tape Doors Engine Indicating DC to DC Controller Drive-Shafts Engine Oil Digital Elevator Assemblies Equipment / Furnishings Consumables Digital – Analog Converter Engine Components Fire Protection D-RAM Engines Flight Controls Adhesives, Tapes & Sealants DSP Evacuation Slides and Life Fuel Solvents EE-PROM Rafts Fuselage Composite Materials EPROM Fire Extinguishers Hardware Shop Supplies FPGA Flap Carriages Helicopter Vibration Oils, Greases & Lubricants Hall Effect Sensor Fuel Pumps Hydraulic Power Paints & Coatings Hot Swap Controller Gear Box Ice and Rain Protection Industrial