Model Checking 0(Einleitung).Key

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Edsger Dijkstra: the Man Who Carried Computer Science on His Shoulders

INFERENCE / Vol. 5, No. 3 Edsger Dijkstra The Man Who Carried Computer Science on His Shoulders Krzysztof Apt s it turned out, the train I had taken from dsger dijkstra was born in Rotterdam in 1930. Nijmegen to Eindhoven arrived late. To make He described his father, at one time the president matters worse, I was then unable to find the right of the Dutch Chemical Society, as “an excellent Aoffice in the university building. When I eventually arrived Echemist,” and his mother as “a brilliant mathematician for my appointment, I was more than half an hour behind who had no job.”1 In 1948, Dijkstra achieved remarkable schedule. The professor completely ignored my profuse results when he completed secondary school at the famous apologies and proceeded to take a full hour for the meet- Erasmiaans Gymnasium in Rotterdam. His school diploma ing. It was the first time I met Edsger Wybe Dijkstra. shows that he earned the highest possible grade in no less At the time of our meeting in 1975, Dijkstra was 45 than six out of thirteen subjects. He then enrolled at the years old. The most prestigious award in computer sci- University of Leiden to study physics. ence, the ACM Turing Award, had been conferred on In September 1951, Dijkstra’s father suggested he attend him three years earlier. Almost twenty years his junior, I a three-week course on programming in Cambridge. It knew very little about the field—I had only learned what turned out to be an idea with far-reaching consequences. a flowchart was a couple of weeks earlier. -

Simula Mother Tongue for a Generation of Nordic Programmers

Simula! Mother Tongue! for a Generation of! Nordic Programmers! Yngve Sundblad HCI, CSC, KTH! ! KTH - CSC (School of Computer Science and Communication) Yngve Sundblad – Simula OctoberYngve 2010Sundblad! Inspired by Ole-Johan Dahl, 1931-2002, and Kristen Nygaard, 1926-2002" “From the cold waters of Norway comes Object-Oriented Programming” " (first line in Bertrand Meyer#s widely used text book Object Oriented Software Construction) ! ! KTH - CSC (School of Computer Science and Communication) Yngve Sundblad – Simula OctoberYngve 2010Sundblad! Simula concepts 1967" •# Class of similar Objects (in Simula declaration of CLASS with data and actions)! •# Objects created as Instances of a Class (in Simula NEW object of class)! •# Data attributes of a class (in Simula type declared as parameters or internal)! •# Method attributes are patterns of action (PROCEDURE)! •# Message passing, calls of methods (in Simula dot-notation)! •# Subclasses that inherit from superclasses! •# Polymorphism with several subclasses to a superclass! •# Co-routines (in Simula Detach – Resume)! •# Encapsulation of data supporting abstractions! ! KTH - CSC (School of Computer Science and Communication) Yngve Sundblad – Simula OctoberYngve 2010Sundblad! Simula example BEGIN! REF(taxi) t;" CLASS taxi(n); INTEGER n;! BEGIN ! INTEGER pax;" PROCEDURE book;" IF pax<n THEN pax:=pax+1;! pax:=n;" END of taxi;! t:-NEW taxi(5);" t.book; t.book;" print(t.pax)" END! Output: 7 ! ! KTH - CSC (School of Computer Science and Communication) Yngve Sundblad – Simula OctoberYngve 2010Sundblad! -

Submission Data for 2020-2021 CORE Conference Ranking Process International Symposium on Formal Methods (Was Formal Methods Europe FME)

Submission Data for 2020-2021 CORE conference Ranking process International Symposium on Formal Methods (was Formal Methods Europe FME) Ana Cavalcanti, Stefania Gnesi, Lars-Henrik Eriksson, Nico Plat, Einar Broch Johnsen, Maurice ter Beek Conference Details Conference Title: International Symposium on Formal Methods (was Formal Methods Europe FME) Acronym : FM Rank: A Data and Metrics Google Scholar Metrics sub-category url: https://scholar.google.com.au/citations?view_op=top_venues&hl=en&vq=eng_theoreticalcomputerscienceposition in sub-category: 20+Image of top 20: ACM Metrics Not Sponsored by ACM Aminer Rank 1 Aminer Rank: 28Name in Aminer: World Congress on Formal MethodsAcronym or Shorthand: FMh-5 Index: 17CCF: BTHU: âĂŞ Top Aminer Cites: http://portal.core.edu.au/core/media/conf_submissions_citations/extra_info1804_aminer_top_cite.png Other Rankings Not aware of any other Rankings Conferences in area: 1. Formal Methods Symposium (FM) 2. Software Engineering and Formal Methods (SEFM), Integrated Formal Methods (IFM) 3. Fundamental Approaches to Software Engineering (FASE), NASA Formal Methods (NFM), Runtime Verification (RV) 4. Formal Aspects of Component Software (FACS), Automated Technology for Verification and Analysis (ATVA) 5. International Conference on Formal Engineering Methods (ICFEM), FormaliSE, Formal Methods in Computer-Aided Design (FMCAD), Formal Methods for Industrial Critical Systems (FMICS) 6. Brazilian Symposium on Formal Methods (SBMF), Theoretical Aspects of Software Engineering (TASE) 7. International Symposium On Leveraging Applications of Formal Methods, Verification and Validation (ISoLA) Top People Publishing Here name: Frank de Boer justification: h-index: 42 ( https://www.cwi.nl/people/frank-de-boer) Frank S. de Boer is senior researcher at the CWI, where he leads the research group on Formal Methods, and Professor of Software Correctness at Leiden University, The Netherlands. -

The Standard Model for Programming Languages: the Birth of A

The Standard Model for Programming Languages: The Birth of a Mathematical Theory of Computation Simone Martini Department of Computer Science and Engineering, University of Bologna, Italy INRIA, Sophia-Antipolis, Valbonne, France http://www.cs.unibo.it/~martini [email protected] Abstract Despite the insight of some of the pioneers (Turing, von Neumann, Curry, Böhm), programming the early computers was a matter of fiddling with small architecture-dependent details. Only in the sixties some form of “mathematical program development” will be in the agenda of some of the most influential players of that time. A “Mathematical Theory of Computation” is the name chosen by John McCarthy for his approach, which uses a class of recursively computable functions as an (extensional) model of a class of programs. It is the beginning of that grand endeavour to present programming as a mathematical activity, and reasoning on programs as a form of mathematical logic. An important part of this process is the standard model of programming languages – the informal assumption that the meaning of programs should be understood on an abstract machine with unbounded resources, and with true arithmetic. We present some crucial moments of this story, concluding with the emergence, in the seventies, of the need of more “intensional” semantics, like the sequential algorithms on concrete data structures. The paper is a small step of a larger project – reflecting and tracing the interaction between mathematical logic and programming (languages), identifying some -

Compsci 6 Programming Design and Analysis

CompSci 6 Programming Design and Analysis Robert C. Duvall http://www.cs.duke.edu/courses/cps006/fall04 http://www.cs.duke.edu/~rcd CompSci 6 : Spring 2005 1.1 What is Computer Science? Computer science is no more about computers than astronomy is about telescopes. Edsger Dijkstra Computer science is not as old as physics; it lags by a couple of hundred years. However, this does not mean that there is significantly less on the computer scientist's plate than on the physicist's: younger it may be, but it has had a far more intense upbringing! Richard Feynman http://www.wordiq.com CompSci 6 : Spring 2005 1.2 Scientists and Engineers Scientists build to learn, engineers learn to build – Fred Brooks CompSci 6 : Spring 2005 1.3 Computer Science and Programming Computer Science is more than programming The discipline is called informatics in many countries Elements of both science and engineering Elements of mathematics, physics, cognitive science, music, art, and many other fields Computer Science is a young discipline Fiftieth anniversary in 1997, but closer to forty years of research and development First graduate program at CMU (then Carnegie Tech) in 1965 To some programming is an art, to others a science, to others an engineering discipline CompSci 6 : Spring 2005 1.4 What is Computer Science? What is it that distinguishes it from the separate subjects with which it is related? What is the linking thread which gathers these disparate branches into a single discipline? My answer to these questions is simple --- it is the art of programming a computer. -

Principles of Computer Science I

Computer Science and Programming Principles of Computer Science is more than programming – The discipline is called informatics in many countries Computer Science I – Elements of both science and engineering • Scientists build to learn, engineers learn to build – Fred Brooks – Elements of mathematics, physics, cognitive science, music, art, and many other fields Computer Science is a young discipline – Fiftieth anniversary in 1997, but closer to forty years of Prof. Nadeem Abdul Hamid research and development CSC 120A - Fall 2004 – First graduate program at CMU (then Carnegie Tech) in Lecture Unit 1 1965 To some programming is an art, to others a science CSC 120A - Berry College - Fall 2004 2 What is Computer Science? CSC 120 - Course Mechanics Syllabus on Viking Web (Handouts section) What is it that distinguishes it from the Class Meetings separate subjects with which it is related? – Lectures: Mon/Wed/Fri, 10–10:50AM, SCI 107 What is the linking thread which gathers these – Labs: Thu, 2:45–4:45 PM, SCI 228 disparate branches into a single discipline? Contact My answer to these questions is simple --- it is – Office phone: (706) 368-5632 – Home phone: (706) 234-7211 the art of programming a computer. It is the art – Email: [email protected] of designing efficient and elegant methods of Office Hours: SCI 354B getting a computer to solve problems, – Mon 11-12:30, 2:30-4 theoretical or practical, small or large, simple – Tue 9-11, 2:30-4 or complex. – Wed 11-12:30 – Thu 9-11 C.A.R. (Tony) Hoare – (or by appt) CSC 120A - Berry College - Fall 2004 3 CSC 120A - Berry College - Fall 2004 4 CSC 120 – Keys to Success CSC 120 – Materials & Resources Start early; work steadily; don’t fall behind. -

Insight, Inspiration and Collaboration

Chapter 1 Insight, inspiration and collaboration C. B. Jones, A. W. Roscoe Abstract Tony Hoare's many contributions to computing science are marked by insight that was grounded in practical programming. Many of his papers have had a profound impact on the evolution of our field; they have moreover provided a source of inspiration to several generations of researchers. We examine the development of his work through a review of the development of some of his most influential pieces of work such as Hoare logic, CSP and Unifying Theories. 1.1 Introduction To many who know Tony Hoare only through his publications, they must often look like polished gems that come from a mind that rarely makes false steps, nor even perhaps has to work at their creation. As so often, this impres- sion is a further compliment to someone who actually adds to very hard work and many discarded attempts the final polish that makes complex ideas rel- atively easy for the reader to comprehend. As indicated on page xi of [HJ89], his ideas typically go through many revisions. The two authors of the current paper each had the honour of Tony Hoare supervising their doctoral studies in Oxford. They know at first hand his kind and generous style and will count it as an achievement if this paper can convey something of the working style of someone big enough to eschew competition and point scoring. Indeed it will be apparent from the following sections how often, having started some new way of thinking or exciting ideas, he happily leaves their exploration and development to others. -

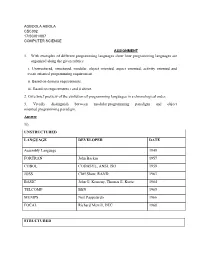

1. with Examples of Different Programming Languages Show How Programming Languages Are Organized Along the Given Rubrics: I

AGBOOLA ABIOLA CSC302 17/SCI01/007 COMPUTER SCIENCE ASSIGNMENT 1. With examples of different programming languages show how programming languages are organized along the given rubrics: i. Unstructured, structured, modular, object oriented, aspect oriented, activity oriented and event oriented programming requirement. ii. Based on domain requirements. iii. Based on requirements i and ii above. 2. Give brief preview of the evolution of programming languages in a chronological order. 3. Vividly distinguish between modular programming paradigm and object oriented programming paradigm. Answer 1i). UNSTRUCTURED LANGUAGE DEVELOPER DATE Assembly Language 1949 FORTRAN John Backus 1957 COBOL CODASYL, ANSI, ISO 1959 JOSS Cliff Shaw, RAND 1963 BASIC John G. Kemeny, Thomas E. Kurtz 1964 TELCOMP BBN 1965 MUMPS Neil Pappalardo 1966 FOCAL Richard Merrill, DEC 1968 STRUCTURED LANGUAGE DEVELOPER DATE ALGOL 58 Friedrich L. Bauer, and co. 1958 ALGOL 60 Backus, Bauer and co. 1960 ABC CWI 1980 Ada United States Department of Defence 1980 Accent R NIS 1980 Action! Optimized Systems Software 1983 Alef Phil Winterbottom 1992 DASL Sun Micro-systems Laboratories 1999-2003 MODULAR LANGUAGE DEVELOPER DATE ALGOL W Niklaus Wirth, Tony Hoare 1966 APL Larry Breed, Dick Lathwell and co. 1966 ALGOL 68 A. Van Wijngaarden and co. 1968 AMOS BASIC FranÇois Lionet anConstantin Stiropoulos 1990 Alice ML Saarland University 2000 Agda Ulf Norell;Catarina coquand(1.0) 2007 Arc Paul Graham, Robert Morris and co. 2008 Bosque Mark Marron 2019 OBJECT-ORIENTED LANGUAGE DEVELOPER DATE C* Thinking Machine 1987 Actor Charles Duff 1988 Aldor Thomas J. Watson Research Center 1990 Amiga E Wouter van Oortmerssen 1993 Action Script Macromedia 1998 BeanShell JCP 1999 AngelScript Andreas Jönsson 2003 Boo Rodrigo B. -

The Birth of a Mathematical Theory of Computation

The Standard Model for Programming Languages: The Birth of a Mathematical Theory of Computation Simone Martini Universit`adi Bologna and INRIA Sophia-Antipolis Bologna, 27 November 2020 Happy birthday, Maurizio! 1 / 58 This workshop: Recent Developments of the Design and Implementation of Programming Languages Well, not so recent: we go back exactly 60 years! It's more a revisionist's tale. 2 / 58 This workshop: Recent Developments of the Design and Implementation of Programming Languages Well, not so recent: we go back exactly 60 years! It's more a revisionist's tale. 3 / 58 viewpoints VDOI:10.1145/2542504 Thomas Haigh Historical Reflections HISTORY AND PHILOSOPHY OF LOGIC, 2015 Actually, Turing Vol. 36, No. 3, 205–228, http://dx.doi.org/10.1080/01445340.2015.1082050 Did Not Invent Edgar G. Daylight the Computer Separating the origins of computer science and technology.Towards a Historical Notion of ‘Turing—the Father of Computer Science’ viewpoints HE 100TH ANNIVERSARY of the birth of Alan Turing was cel- EDGAR G. DAYLIGHT ebrated in 2012. The com- viewpointsputing community threw its Utrecht University, The Netherlands biggest ever birthday party. [email protected]:10.1145/2658985V TMajor events were organized around the world, including conferences or festi- vals in Princeton, Cambridge, Manches- Viewpoint Received 14 January 2015 Accepted 3 March 2015 ter, and Israel. There was a concert in Seattle and an opera in Finland. Dutch In the popular imagination, the relevance of Turing’s theoretical ideas to people producing actual machines was and French researchers built small Tur- Why Did Computer ing Machines out of Lego Mindstorms significant and appreciated by everybody involved in computing from the moment he published his 1936 paper kits. -

The Soul of Computer Science

The Soul of Computer Science Salvador Lucas DSIC, Universitat Polit`ecnicade Val`encia(UPV) Talk at the Universidad Complutense de Madrid 1 Salvador Lucas (UPV) UCM 2016 October 26, 2016 1 / 63 The Soul of Computer Science 80 years of Computer Science! 2 Salvador Lucas (UPV) UCM 2016 October 26, 2016 2 / 63 The Soul of Computer Science The soul of Computer Science is Logic Waves of Logic in the history of Computer Science (incomplete list): 0 Hilbert posses \the main problem of mathematical logic" (20's) 1 Church and Turing's logical devices as effective methods (1936) 2 Shannon's encoding of Boolean functions as circuits (1938) 3 von Neumann's logical design of an electronic computer (1946) 4 Floyd/Hoare's logical approach to program verification (1967-69) 5 Kowalski's predicate logic as programming language (1974) 6 Hoare's challenge of a verifying compiler (2003) 7 Berners-Lee's semantic web challenge (2006) Soul Distinguishing mark of living things (...) responsible for planning and practical thinking (Stanford Encyclopedia of Philosophy) We can say: Logic is the soul of Computer Science! 3 Salvador Lucas (UPV) UCM 2016 October 26, 2016 3 / 63 The Soul of Computer Science Hilbert and the Decision Problem David Hilbert (1862-1943) 4 Salvador Lucas (UPV) UCM 2016 October 26, 2016 4 / 63 There is no solution! In 1970, Yuri Matiyasevich proved it unsolvable, i.e., there is no such `process'. How could Matiyasevich reach such a conclusion? The Soul of Computer Science Hilbert and the Decision Problem In his \Mathematical Problems" address during the2 nd International Congress of Mathematicians (Paris, 1900), he proposed the following: 10th Hilbert's problem Given a diophantine equation with any number of unknown quantities and with rational integral numerical coefficients: To devise a process according to which it can be determined by a finite number of operations whether the equation is solvable in rational integers. -

Education in Programming David Gries Dr. Rer. Nat., Munich Institute

Education in Programming David Gries Dr. rer. nat., Munich Institute of Technology, 1966 Computer Science, Cornell University, Ithaca, NY 1 1 A Glimerick of Hope David Gries, 1995 Abstract Well I got my degree at that place The world is turning to C, And my ancestors came from that race Though at best it is taught awkwardly, Though Great New York C But we don’t have to mope, Was the Birthplace of me There’s a glimmer of hope, And CS at Cornell is my base. In the methods of formality President Mary of Eire So I don't have a real PhD. Was supposed to come to regale ya. It's the Dr. Rer. Nat. that's for me. But matters of State And it's from MIT Made her cancel that date --On your side of the sea So you’re stuck with this guy from Bavaria Munich Inst. of Technolology 2 2 In 1962–63, in Illinois writing the ALCOR-ILLINOIS 7090 ALGOL Compiler I came to Munich to get a PhD (and finish the compiler) Manfred Paul Rudiger Wiehle Elaine and David Gries 3 3 Instrumental in the development of programming languages and their implementation A early as 1952, Bauer: Keller principle Influential in development of Algol 60 Educate the next generation of computer scientists 1968 and 1969 NATO Conferences on Software Engineering (Garmisch and Rome) 4 4 1968 and 1969 NATO Conferences Software Engineering (Garmisch and Rome) 5 5 1968 and 1969 NATO Conferences Software Engineering (Garmisch and Rome) 6 6 Instrumental in the development of programming languages and their implementation Educate the next generation of computer scientists 1968 and 1969 NATO Conferences on Software Engineering (Garmisch and Rome) The Marktoberdorf Summer Schools now led ably by Manfred Broy 7 7 The teaching of programming simplicity elegance perfection intellectual honesty Edsger W. -

BCIS 1305 Business Computer Applications

BCIS 1305 Business Computer Applications BCIS 1305 Business Computer Applications San Jacinto College This course was developed from generally available open educational resources (OER) in use at multiple institutions, drawing mostly from a primary work curated by the Extended Learning Institute (ELI) at Northern Virginia Community College (NOVA), but also including additional open works from various sources as noted in attributions on each page of materials. Cover Image: “Keyboard” by John Ward from https://flic.kr/p/tFuRZ licensed under a Creative Commons Attribution License. BCIS 1305 Business Computer Applications by Extended Learning Institute (ELI) at NOVA is licensed under a Creative Commons Attribution 4.0 International License, except where otherwise noted. CONTENTS Module 1: Introduction to Computers ..........................................................................................1 • Reading: File systems ....................................................................................................................................... 1 • Reading: Basic Computer Skills ........................................................................................................................ 1 • Reading: Computer Concepts ........................................................................................................................... 1 • Tutorials: Computer Basics................................................................................................................................ 1 Module 2: Computer