A Systemc Behavioral Model for Delay Variation Analysis in Asynchronous Designs

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Didcot Railway CENTRE

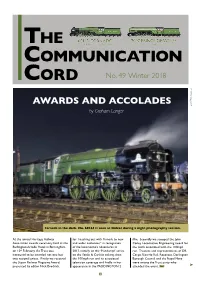

THE COMMUNICATION ORD No. 49 Winter 2018 C Shapland Andrew AWARDS AND ACCOLADES by Graham Langer Tornado in the dark. No. 60163 is seen at Didcot during a night photography session. At the annual Heritage Railway for “reaching out with Tornado to new film. Secondly we scooped the John Association awards ceremony held at the and wider audiences” in recognition Coiley Locomotive Engineering award for Burlington Arcade Hotel in Birmingham of the locomotive’s adventures in the work associated with the 100mph on 10th February, the Trust was 2017, initially on the ‘Plandampf’ series run. Trustees and representatives of DB honoured to be awarded not one but on the Settle & Carlisle railway, then Cargo, Ricardo Rail, Resonate, Darlington two national prizes. Firstly we received the 100mph run and its associated Borough Council and the Royal Navy the Steam Railway Magazine Award, television coverage and finally in her were among the Trust party who ➤ presented by editor Nick Brodrick, appearance in the PADDINGTON 2 attended the event. TCC 1 Gwynn Jones CONTENTS EDItorIAL by Graham Langer PAGE 1-2 Mandy Gran Even while Tornado Awards and Accolades up his own company Paul was Head of PAGE 3 was safely tucked Procurement for Northern Rail and Editorial up at Locomotive previously Head of Property for Arriva Tornado helps Blue Peter Maintenance Services Trains Northern. t PAGE 4 in Loughborough Daniela Filova,´ from Pardubice in the Tim Godfrey – an obituary for winter overhaul, Czech Republic, joined the Trust as Richard Hardy – an obituary she continued to Assistant Mechanical Engineer to David PAGE 5 generate headlines Elliott. -

Unraveling the Evolutionary History of Orangutans (Genus: Pongo)- the Impact of Environmental Processes and the Genomic Basis of Adaptation

Zurich Open Repository and Archive University of Zurich Main Library Strickhofstrasse 39 CH-8057 Zurich www.zora.uzh.ch Year: 2015 Unraveling the evolutionary history of Orangutans (genus: Pongo)- the impact of environmental processes and the genomic basis of adaptation Mattle-Greminger, Maja Patricia Posted at the Zurich Open Repository and Archive, University of Zurich ZORA URL: https://doi.org/10.5167/uzh-121397 Dissertation Published Version Originally published at: Mattle-Greminger, Maja Patricia. Unraveling the evolutionary history of Orangutans (genus: Pongo)- the impact of environmental processes and the genomic basis of adaptation. 2015, University of Zurich, Faculty of Science. Unraveling the Evolutionary History of Orangutans (genus: Pongo) — The Impact of Environmental Processes and the Genomic Basis of Adaptation Dissertation zur Erlangung der naturwissenschaftlichen Doktorwürde (Dr. sc. nat.) vorgelegt der Mathematisch‐naturwissenschaftlichen Fakultät der Universität Zürich von Maja Patricia Mattle‐Greminger von Richterswil (ZH) Promotionskomitee Prof. Dr. Carel van Schaik (Vorsitz) PD Dr. Michael Krützen (Leitung der Dissertation) Dr. Maria Anisimova Zürich, 2015 To my family Table of Contents Table of Contents ........................................................................................................ 1 Summary ..................................................................................................................... 3 Zusammenfassung ..................................................................................................... -

Intermedial Autobiography Since Roland Barthes A

UNIVERSITY OF CALIFORNIA Los Angeles Between Erasure and Exposure: Intermedial Autobiography Since Roland Barthes A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in French and Francophone Studies by Lauren Elizabeth Van Arsdall 2015 © Copyright by Lauren Elizabeth Van Arsdall 2015 ABSTRACT OF THE DISSERTATION Between Erasure and Exposure: Intermedial Autobiography Since Roland Barthes by Lauren Elizabeth Van Arsdall Doctor of Philosophy in French and Francophone Studies University of California, Los Angeles, 2015 Professor Malina Stefanovska, Chair In my dissertation, I investigate the trend toward intermedial representations of the self in contemporary French personal writing of an autobiographical type. The theoretical framework of my dissertation is based on notions of referentiality presented in La chambre claire, and in essays contemporaneous to Roland Barthes’s by Jean-Luc Nancy, Jacques Derrida, Pierre Bourdieu, and Jean Baudrillard. As I demonstrate, they are in dialogue with it, all the while exploring the boundaries of self-representation in relation to illness and death. At the outset, an analysis of the discourses of photography in France from the 1980s to the early 2000s informs my discussion of representations of an expected death in works by Alix Cléo Roubaud, Jacques Roubaud, Annie Ernaux, and Hervé Guibert. I argue that the legacy of a Barthesian conceptualization of the photograph obliges writers to rethink their stance towards representing the self. Through gestures of erasure and exposure, they create an intermedial aesthetic coupling writing, photography, and film to explore anew certain taboos concerning self and death. Intermediality opens up the notions of referentiality presented in Roland Barthes’s La chambre ii claire: note sure la photographie— the making of traces through writing, memories, and recording the body. -

Variation and Exceptionality in Modern Hebrew Spirantization (Dissertation) Michal Temkin Martinez Boise State University SOURCES of NON-CONFORMITY in PHONOLOGY

Boise State University ScholarWorks Mary Ellen Ryder Linguistics Lab Department of English 5-1-2010 Sources of Non-conformity in Phonology: Variation and Exceptionality in Modern Hebrew Spirantization (Dissertation) Michal Temkin Martinez Boise State University SOURCES OF NON-CONFORMITY IN PHONOLOGY: VARIATION AND EXCEPTIONALITY IN MODERN HEBREW SPIRANTIZATION by Michal Temkin Martínez A Dissertation Presented to the FACULTY OF THE USC GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA In Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY (LINGUISTICS) May 2010 Copyright 2010 Michal Temkin Martínez Dedication To my grandparents for instilling in me a love for language ii Acknowledgements Although I realize that writing a dissertation and earning a Ph.D. are not as monumental as, say, winning a Nobel Prize, this is my biggest accomplishment in life thus far, and there are many people without whom it would have been impossible. Therefore, I feel it is only right to take the time now to thank them for their support. My advisor and dissertation chair, Rachel Walker, has been an amazing mentor and role model. Rachel embodies the well-balanced academic, her teaching and advising styles are enviable, and as I now realize more than ever before, her seemingly effortless manner stems from constant dedication and preparation. I am extremely grateful for her support in all aspects of my education, including the many service projects I found myself involved in. I could not have asked for a more understanding and compassionate advisor. My committee members – Louis Goldstein, Elsi Kaiser, Anna Lubowicz, and Mario Saltarelli – have all contributed to my work in many ways. -

2008 International List of Protected Names

LISTE INTERNATIONALE DES NOMS PROTÉGÉS (également disponible sur notre Site Internet : www.IFHAonline.org) INTERNATIONAL LIST OF PROTECTED NAMES (also available on our Web site : www.IFHAonline.org) Fédération Internationale des Autorités Hippiques de Courses au Galop International Federation of Horseracing Authorities _________________________________________________________________________________ _ 46 place Abel Gance, 92100 Boulogne, France Avril / April 2008 Tel : + 33 1 49 10 20 15 ; Fax : + 33 1 47 61 93 32 E-mail : [email protected] Internet : www.IFHAonline.org La liste des Noms Protégés comprend les noms : The list of Protected Names includes the names of : ) des gagnants des 33 courses suivantes depuis leur ) the winners of the 33 following races since their création jusqu’en 1995 first running to 1995 inclus : included : Preis der Diana, Deutsches Derby, Preis von Europa (Allemagne/Deutschland) Kentucky Derby, Preakness Stakes, Belmont Stakes, Jockey Club Gold Cup, Breeders’ Cup Turf, Breeders’ Cup Classic (Etats Unis d’Amérique/United States of America) Poule d’Essai des Poulains, Poule d’Essai des Pouliches, Prix du Jockey Club, Prix de Diane, Grand Prix de Paris, Prix Vermeille, Prix de l’Arc de Triomphe (France) 1000 Guineas, 2000 Guineas, Oaks, Derby, Ascot Gold Cup, King George VI and Queen Elizabeth, St Leger, Grand National (Grande Bretagne/Great Britain) Irish 1000 Guineas, 2000 Guineas, Derby, Oaks, Saint Leger (Irlande/Ireland) Premio Regina Elena, Premio Parioli, Derby Italiano, Oaks (Italie/Italia) -

2009 International List of Protected Names

Liste Internationale des Noms Protégés LISTE INTERNATIONALE DES NOMS PROTÉGÉS (également disponible sur notre Site Internet : www.IFHAonline.org) INTERNATIONAL LIST OF PROTECTED NAMES (also available on our Web site : www.IFHAonline.org) Fédération Internationale des Autorités Hippiques de Courses au Galop International Federation of Horseracing Authorities __________________________________________________________________________ _ 46 place Abel Gance, 92100 Boulogne, France Tel : + 33 1 49 10 20 15 ; Fax : + 33 1 47 61 93 32 E-mail : [email protected] 2 03/02/2009 International List of Protected Names Internet : www.IFHAonline.org 3 03/02/2009 Liste Internationale des Noms Protégés La liste des Noms Protégés comprend les noms : The list of Protected Names includes the names of : ) des gagnants des 33 courses suivantes depuis leur ) the winners of the 33 following races since their création jusqu’en 1995 first running to 1995 inclus : included : Preis der Diana, Deutsches Derby, Preis von Europa (Allemagne/Deutschland) Kentucky Derby, Preakness Stakes, Belmont Stakes, Jockey Club Gold Cup, Breeders’ Cup Turf, Breeders’ Cup Classic (Etats Unis d’Amérique/United States of America) Poule d’Essai des Poulains, Poule d’Essai des Pouliches, Prix du Jockey Club, Prix de Diane, Grand Prix de Paris, Prix Vermeille, Prix de l’Arc de Triomphe (France) 1000 Guineas, 2000 Guineas, Oaks, Derby, Ascot Gold Cup, King George VI and Queen Elizabeth, St Leger, Grand National (Grande Bretagne/Great Britain) Irish 1000 Guineas, 2000 Guineas, -

An Independent Locus Upstream of ASIP Controls Variation in the Shade of the Bay Coat Colour in Horses

G C A T T A C G G C A T genes Article An Independent Locus Upstream of ASIP Controls Variation in the Shade of the Bay Coat Colour in Horses 1,2, 3, 4 5 Laura J. Corbin y , Jessica Pope y, Jacqueline Sanson , Douglas F. Antczak , Donald Miller 5, Raheleh Sadeghi 5 and Samantha A. Brooks 4,6,* 1 Population Health Sciences, Bristol Medical School, University of Bristol, Bristol BS8 2BN, UK; [email protected] 2 MRC Integrative Epidemiology Unit at University of Bristol, Bristol BS8 2BN, UK 3 Bristol Veterinary School, University of Bristol, Bristol BS8 1QU, UK; [email protected] 4 Department of Animal Sciences, University of Florida, Gainesville, FL 32610, USA; [email protected] 5 Baker Institute for Animal Health, College of Veterinary Medicine, Cornell University, Ithaca, NY 14853, USA; [email protected] (D.F.A.); [email protected] (D.M.); [email protected] (R.S.) 6 UF Genetics Institute, University of Florida, Gainesville, FL 32611, USA * Correspondence: samantha.brooks@ufl.edu These authors share first authorship. y Received: 7 April 2020; Accepted: 27 May 2020; Published: 30 May 2020 Abstract: Novel coat colour phenotypes often emerge during domestication, and there is strong evidence of genetic selection for the two main genes that control base coat colour in horses—ASIP and MC1R. These genes direct the type of pigment produced, red pheomelanin (MC1R) or black eumelanin (ASIP), as well as the relative concentration and the temporal–spatial distribution of melanin pigment deposits in the skin and hair coat. -

HAWN AC1.H3 5138 R.Pdf

UNIVERSITY OF HAWAI'/ LIBRARY A mGHER-ORDER DEPTH-INTEGRATED MODEL FOR WATER WAVES AND CURRENTS GENERATED BY UNDERWATER LANDSLIDES A DISSERTATION SUBMITTED TO TIIE GRADUATE DMSION OF TIIE UNIVERSITY OF HAWAII IN PARTIAL Ftrr.FILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN CML ENGINEERING AUGUST 2008 By Hongqiang Zhou Dissertation. Committee: Michelle H. Teng, Chairperson Janet M. Becker Edmond D.H. Cheng Jannette B. Frandsen H. Ronald Riggs We certify that we have read this dissertation and that, in our opinion, it is satisfactory in scope and quality as a dissertation for the degree of Doctor of Philosophy in Civil Engineering. DISSERT XI~ COMMITTEE ~ '~ ChairpersZ ~ ~'¥;~ ~.JF;e~ (.. ii ACKNOWLEDGEMENT I would like to express my sincere gratitude and deepest respect to Prof. Michelle H. Teng, my academic advisor, for her continuous encouragement and superb guidance throughout my doctoral studies and research. Without her support, this dissertation would never have been accomplished. I am also grateful to Profs. Janet M. Becker, Edmond D.H. Cheng, Jannette B. Frandsen, and H. Ronald Riggs. Their invaluable help and inspiring advices are important for this research. Special appreciation goes to Prof. Clark C.K. Liu for his excellent teaching and helpful advices on this dissertation. I am obliged to the department and college technicians, Mr. Brian Kodama, Mr. Miles Wagner and Mr. Mitchell Pinkerton, for their help in the experiments. I thank them with gratitude for their time and knowledge that they shared with me. Thanks are also due to department secretaries Ms. Janis Kusatsu and Ms. Amy Fujishige for the administrative help and their kindness that made me feel home at the Department of Civil and Environmental Engineering. -

Nutrition and Feeding Management for Horse Owners (Agdex 460/51-1)

NUTRITION AND FEEDING MANAGEMENT FOR HORSE OWNERS NUTRITION AND FEEDING MANAGEMENT NUTRITION AND FEEDING Management FOR HORSE OWNERS NUTRITION AND FEEDING MANAGEMENT FOR HORSE OWNERS Susan Novak, Ph. D Anna Kate Shoveller, Ph. D With contributions by Lori K. Warren, Ph. D Published by: Alberta Agriculture and Rural Development Information Packaging Centre 7000-113 Street Edmonton, Alberta Canada T6H 0T6 Editor: Ken Blackley Graphic Designer: Perpetual Notion Design Inc. Copyright © 2008. Her Majesty the Queen in Right of Alberta (Alberta Agriculture and Rural Development) All rights reserved No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical photocopying,recording, or otherwise without written permission from the Information Packaging Centre, Alberta Agriculture and Rural Development. ISBN 0-7732-6078-1 Copies of this publication may be purchased from: Publications Office Alberta Agriculture and Rural Development Phone: 1-800-292-5697 (toll-free in Canada) or (780) 427-0391 or see our website www.agriculture.alberta.ca/publications for information on other information products. Printed in Canada NutritioN aNd FeediNg MaNageMeNt For horse owNers • i TABLE OF CONTENTS INTRODUCTION ..................................................................................1 EVALUATING YOUR HORSE’S CONDITION ...........................................1 Body Condition Scoring ...............................................................................2 Determining -

Synthetics and Sealed Dirt: the Science, Data And

THURSDAY, APRIL 11, 2019 SYNTHETICS AND SEALED REVERSAL ON “NO WHIP” DAY AT SANTA ANITA DIRT: THE SCIENCE, DATA by Dan Ross In the latest move in the ongoing chess games at Santa Anita, AND EXPERT OPINION jockeys will carry and use their crops under the existing rules when race-riding at the track this Friday. This reverses a decision the Jockey’s Guild touted last week, that the jockeys would ride on Friday without one. “We will comply, for the time being, with the request from the Thoroughbred Owners of California to not proceed with the jockeys not using riding crops during the races at Santa Anita Park on Friday, April 12,” said Jockeys’ Guild President and CEO Terry Meyocks, in a joint press release between the Jockeys’ Guild and the Thoroughbred Owners of California (TOC). “For the past month we have received virtually no support from industry organizations in California until contacted by the TOC in the last day and a half,” Meyocks said. Cont. p8 IN TDN EUROPE TODAY Enable running on the Tapeta track at Newcastle | Racing Post WAR FRONT’S MUNITIONS WINS DJEBEL by Dan Ross Godolphin’s Munitions (War Front) proved gamest in the G3 Amid the talk of whip use and medication restrictions during Prix Djebel at Maisons-Laffitte on Wednesday. Click or tap the last scheduled California Horse Racing Board (CHRB) here to go straight to TDN Europe. meeting, there was another topic that resonated loudly: the safety of Santa Anita's track surface. "We're definitely considering plans in the future, on these rainy days, of almost being like in the Northeast, when they have snow days and take the day off," said The Stronach Group's COO Tim Ritvo, about the possibility of restricting racing and training on a sealed track. -

The History and Delineation of the Horse, in All His Varieties

IV III I'll! iiini'i' ir:i II, II : 3 9090 013 401 209 Webster Family Library of Veterinary Medicine Cummings School of Veterinary Medicine at Tuft? Univcirsity 200 Westboro Road Norfh Grafton. MA 01536 ^11 pr 2^ A a' I ^^i > \ THE HISTORY AND DELINEATION OF THE HORSE, IN ALL HIS VARIETIES. COJlPUElILKDIlsG THE Al'PROrRIATE USES, MAXAGEMEM', AND TROGRESSIVE IMPRO\-EMENT OF EACH: WITH A PARTICULAR INVESTIGATION OF THE CHARACTER OF THE RACE-HORSE, AND THE iSusmess of tjje Cutt ILLUSTRATED BY ANECDOTES AND BIOGRAPHICAL NOTICES OF DISTINGUISHED SPORTSMEN. THE ENGRAVIKCS FROM ORIGINAL PAINTINGS. WITH INSTRUCTIONS FOR BREEDING, BREAKING, TRAINING, AND THE GENERAL MANAGEMENT OF THE HORSE, BOTH li\ A STATE OF HEALTH AND OF DISEASE. BY JOHN LAWRENCE, AUrilOR OF " A PHILOSOPHICAL AND PRACTICAL TREATISE ON HORSES," &c. &c. Sllbton Press: l-aiNTEU FOR JAMES CUNDEE, IVY-LANE, PATERNOSTER-HOW AND JOHN SCOTT, ROSO.MAN STREET, CLERKENWELL, LONDON. 1809. 9Lt5 p;i PREFACE. It is the object of the ensuing Work, to unite with the utiHty of description, the most finished eleg-ance of the graphic art. To pourtray the noblest and most beau- tiful of all animals, in his natural and improved form, in order to aid the comprehension and judgment of the reader, by an address to the eye, as well as to the under- standing. To blend both useful and ornamental decora- tion with solid instruction, and with such a degree of amusement, as may result from anecdotes connected with the subject. With respect to arrangement, a cursory, yet it is hoped, satisfactory view, is given of the Horses and Horsemanship of the earliest ages, and of this country especially, with an attention to the various species in use, and a delineation of the origin of the Race Horse, through the blood of which, the English breed has been generally ameliorated and elevated to its present state of perfection. -

Europe and the Microscope in the Enlightenment

Eu r o p e a n d t h e M ic r o sc o pe in t h e Enlightenment by Marc James Ratcliff History of Medicine Department of Anatomy University College London Thesis submitted to University College London for the degree of Doctor of Philosophy January 2001 ProQuest Number: U643645 All rights reserved INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted. In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion. uest. ProQuest U643645 Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code. Microform Edition © ProQuest LLC. ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, Ml 48106-1346 A bstract While historians of the microscope currently consider that no systematic programme of microscopy took place during the Enlightenment, this thesis challenges this view and aims to show when and where microscopes were used as research tools. The focus of the inquiry is the research on microscopic animalcules and the relationship of European microscope making and practices of the microscope with topical trends of the industrial revolution, such as quantification. Three waves of research are characterised for the research on animalcules in the Enlightenment: 1. seventeenth-century observations on animalcules crowned by Louis Joblot's 1718 work in the milieu of the Paris Académie royale des sciences, 2.