DS083 (V5.0) June 21, 2011 0 Product Specification

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

State Model Syllabus for Undergraduate Courses in Science (2019-2020)

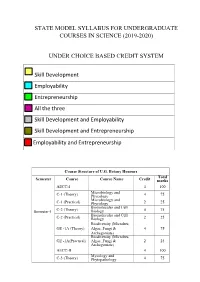

STATE MODEL SYLLABUS FOR UNDERGRADUATE COURSES IN SCIENCE (2019-2020) UNDER CHOICE BASED CREDIT SYSTEM Skill Development Employability Entrepreneurship All the three Skill Development and Employability Skill Development and Entrepreneurship Employability and Entrepreneurship Course Structure of U.G. Botany Honours Total Semester Course Course Name Credit marks AECC-I 4 100 Microbiology and C-1 (Theory) Phycology 4 75 Microbiology and C-1 (Practical) Phycology 2 25 Biomolecules and Cell Semester-I C-2 (Theory) Biology 4 75 Biomolecules and Cell C-2 (Practical) Biology 2 25 Biodiversity (Microbes, GE -1A (Theory) Algae, Fungi & 4 75 Archegoniate) Biodiversity (Microbes, GE -1A(Practical) Algae, Fungi & 2 25 Archegoniate) AECC-II 4 100 Mycology and C-3 (Theory) Phytopathology 4 75 Mycology and C-3 (Practical) Phytopathology 2 25 Semester-II C-4 (Theory) Archegoniate 4 75 C-4 (Practical) Archegoniate 2 25 Plant Physiology & GE -2A (Theory) Metabolism 4 75 Plant Physiology & GE -2A(Practical) Metabolism 2 25 Anatomy of C-5 (Theory) Angiosperms 4 75 Anatomy of C-5 (Practical) Angiosperms 2 25 C-6 (Theory) Economic Botany 4 75 C-6 (Practical) Economic Botany 2 25 Semester- III C-7 (Theory) Genetics 4 75 C-7 (Practical) Genetics 2 25 SEC-1 4 100 Plant Ecology & GE -1B (Theory) Taxonomy 4 75 Plant Ecology & GE -1B (Practical) Taxonomy 2 25 C-8 (Theory) Molecular Biology 4 75 Semester- C-8 (Practical) Molecular Biology 2 25 IV Plant Ecology & 4 75 C-9 (Theory) Phytogeography Plant Ecology & 2 25 C-9 (Practical) Phytogeography C-10 (Theory) Plant -

073-080.Pdf (568.3Kb)

Graphics Hardware (2007) Timo Aila and Mark Segal (Editors) A Low-Power Handheld GPU using Logarithmic Arith- metic and Triple DVFS Power Domains Byeong-Gyu Nam, Jeabin Lee, Kwanho Kim, Seung Jin Lee, and Hoi-Jun Yoo Department of EECS, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea Abstract In this paper, a low-power GPU architecture is described for the handheld systems with limited power and area budgets. The GPU is designed using logarithmic arithmetic for power- and area-efficient design. For this GPU, a multifunction unit is proposed based on the hybrid number system of floating-point and logarithmic numbers and the matrix, vector, and elementary functions are unified into a single arithmetic unit. It achieves the single-cycle throughput for all these functions, except for the matrix-vector multipli- cation with 2-cycle throughput. The vertex shader using this function unit as its main datapath shows 49.3% cycle count reduction compared with the latest work for OpenGL transformation and lighting (TnL) kernel. The rendering engine uses also the logarithmic arithmetic for implementing the divisions in pipeline stages. The GPU is divided into triple dynamic voltage and frequency scaling power domains to minimize the power consumption at a given performance level. It shows a performance of 5.26Mvertices/s at 200MHz for the OpenGL TnL and 52.4mW power consumption at 60fps. It achieves 2.47 times per- formance improvement while reducing 50.5% power and 38.4% area consumption compared with the lat- est work. Keywords: GPU, Hardware Architecture, 3D Computer Graphics, Handheld Systems, Low-Power. -

An Architecture and Compiler for Scalable On-Chip Communication

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. XX, NO. Y, MONTH 2004 1 An Architecture and Compiler for Scalable On-Chip Communication Jian Liang, Student Member, IEEE, Andrew Laffely, Sriram Srinivasan, and Russell Tessier, Member, IEEE Abstract— tion of communication resources. Significant amounts of arbi- A dramatic increase in single chip capacity has led to a tration across even a small number of components can quickly revolution in on-chip integration. Design reuse and ease-of- form a performance bottleneck, especially for data-intensive, implementation have became important aspects of the design pro- cess. This paper describes a new scalable single-chip communi- stream-based computation. This issue is made more complex cation architecture for heterogeneous resources, adaptive System- by the need to compile high-level representations of applica- On-a-Chip (aSOC), and supporting software for application map- tions to SoC environments. The heterogeneous nature of cores ping. This architecture exhibits hardware simplicity and opti- in terms of clock speed, resources, and processing capability mized support for compile-time scheduled communication. To il- makes cost modeling difficult. Additionally, communication lustrate the benefits of the architecture, four high-bandwidth sig- nal processing applications including an MPEG-2 video encoder modeling for interconnection with long wires and variable arbi- and a Doppler radar processor have been mapped to a prototype tration protocols limits performance predictability required by aSOC device using our design mapping technology. Through ex- computation scheduling. perimentation it is shown that aSOC communication outperforms Our platform for on-chip interconnect, adaptive System-On- a hierarchical bus-based system-on-chip (SoC) approach by up to a-Chip (aSOC), is a modular communications architecture. -

Decizia Nr. 1068 Din 21.11.2019 Privind Somarea S.C. UPC ROMÂNIA S.R.L

CONSILIUL NA Ţ IONAL AL AUDIOVIZUALULUI ROMÂNIA Autoritate publică BUCUREŞTI autonomă Bd. Libertăţii nr. 14 Tel.: 00 4 021 3055356 Sector 5, CP 050706 Fax: 00 4 021 3055354 www.cna.ro [email protected] Decizia nr. 1068 din 21.11.2019 privind somarea S.C. UPC ROMÂNIA S.R.L. Bucureşti, str. Sg. Constantin Ghercu nr. 1A, et. 8-10, sector 6 C.U.I. 12288994 Fax: 0311018101 Întrunit în şedinţă publică în ziua de 21 noiembrie 2019, Consiliul Naţional al Audiovizualului a analizat situația întocmită de Serviciul Inspecţie cu privire la reţelele de comunicaţii electronice din localitățile Ocland și Ocna de Jos, jud. Harghita și Tulcea, jud. Tulcea, aparţinând S.C. UPC ROMÂNIA S.R.L. Distribuitorul de servicii S.C. UPC ROMÂNIA S.R.L. deţine următoarele avize de retransmisie: - nr. A 5776/21.02.2008 pentru localitatea Ocland, jud. Harghita; - nr. A 5781/21.02.2008 pentru localitatea Ocna de Jos, jud. Harghita; - nr. A 5801/22.07.2019 pentru localitatea Tulcea, jud. Tulcea. În urma analizării situației sintetizate prezentate de Serviciul Inspecție, membrii Consiliului au constatat că distribuitorul de servicii S.C. UPC ROMÂNIA S.R.L. a încălcat prevederile articolelor 74 alin. (3) și 82 alin. (2) din Legea audiovizualului nr. 504/2002, cu modificările şi completările ulterioare. Potrivit dispozițiilor invocate: Art. 74 alin. (3): Distribuitorii de servicii pot modifica structura ofertei de servicii de programe retransmise numai cu acordul Consiliului. Art. 82 alin. (2): Distribuitorii care retransmit servicii de programe au obligaţia, la nivel regional şi local, să includă în oferta lor cel puţin două programe regionale şi două programe locale, acolo unde acestea există; criteriul de departajare va fi ordinea descrescătoare a audienţei. -

On-Chip Interconnect Schemes for Reconfigurable System-On-Chip

On-chip Interconnect Schemes for Reconfigurable System-on-Chip Andy S. Lee, Neil W. Bergmann. School of ITEE, The University of Queensland, Brisbane Australia {andy, n.bergmann} @itee.uq.edu.au ABSTRACT On-chip communication architectures can have a great influence on the speed and area of System-on-Chip designs, and this influence is expected to be even more pronounced on reconfigurable System-on-Chip (rSoC) designs. To date, little research has been conducted on the performance implications of different on-chip communication architectures for rSoC designs. This paper motivates the need for such research and analyses current and proposed interconnect technologies for rSoC design. The paper also describes work in progress on implementation of a simple serial bus and a packet-switched network, as well as a methodology for quantitatively evaluating the performance of these interconnection structures in comparison to conventional buses. Keywords: FPGAs, Reconfigurable Logic, System-on-Chip 1. INTRODUCTION System-on-chip (SoC) technology has evolved as the predominant circuit design methodology for custom ASICs. SoC technology moves design from the circuit level to the system level, concentrating on the selection of appropriate pre-designed IP Blocks, and their interconnection into a complete system. However, modern ASIC design and fabrication are expensive. Design tools may cost many hundreds of thousands of dollars, while tooling and mask costs for large SoC designs now approach $1million. For low volume applications, and especially for research and development projects in universities, reconfigurable System-on-Chip (rSoC) technology is more cost effective. Like conventional SoC design, rSoC involves the assembly of predefined IP blocks (such as processors and peripherals) and their interconnection. -

Stream Name Category Name Coronavirus (COVID-19) |EU| FRANCE TNTSAT ---TNT-SAT ---|EU| FRANCE TNTSAT TF1 SD |EU|

stream_name category_name Coronavirus (COVID-19) |EU| FRANCE TNTSAT ---------- TNT-SAT ---------- |EU| FRANCE TNTSAT TF1 SD |EU| FRANCE TNTSAT TF1 HD |EU| FRANCE TNTSAT TF1 FULL HD |EU| FRANCE TNTSAT TF1 FULL HD 1 |EU| FRANCE TNTSAT FRANCE 2 SD |EU| FRANCE TNTSAT FRANCE 2 HD |EU| FRANCE TNTSAT FRANCE 2 FULL HD |EU| FRANCE TNTSAT FRANCE 3 SD |EU| FRANCE TNTSAT FRANCE 3 HD |EU| FRANCE TNTSAT FRANCE 3 FULL HD |EU| FRANCE TNTSAT FRANCE 4 SD |EU| FRANCE TNTSAT FRANCE 4 HD |EU| FRANCE TNTSAT FRANCE 4 FULL HD |EU| FRANCE TNTSAT FRANCE 5 SD |EU| FRANCE TNTSAT FRANCE 5 HD |EU| FRANCE TNTSAT FRANCE 5 FULL HD |EU| FRANCE TNTSAT FRANCE O SD |EU| FRANCE TNTSAT FRANCE O HD |EU| FRANCE TNTSAT FRANCE O FULL HD |EU| FRANCE TNTSAT M6 SD |EU| FRANCE TNTSAT M6 HD |EU| FRANCE TNTSAT M6 FHD |EU| FRANCE TNTSAT PARIS PREMIERE |EU| FRANCE TNTSAT PARIS PREMIERE FULL HD |EU| FRANCE TNTSAT TMC SD |EU| FRANCE TNTSAT TMC HD |EU| FRANCE TNTSAT TMC FULL HD |EU| FRANCE TNTSAT TMC 1 FULL HD |EU| FRANCE TNTSAT 6TER SD |EU| FRANCE TNTSAT 6TER HD |EU| FRANCE TNTSAT 6TER FULL HD |EU| FRANCE TNTSAT CHERIE 25 SD |EU| FRANCE TNTSAT CHERIE 25 |EU| FRANCE TNTSAT CHERIE 25 FULL HD |EU| FRANCE TNTSAT ARTE SD |EU| FRANCE TNTSAT ARTE FR |EU| FRANCE TNTSAT RMC STORY |EU| FRANCE TNTSAT RMC STORY SD |EU| FRANCE TNTSAT ---------- Information ---------- |EU| FRANCE TNTSAT TV5 |EU| FRANCE TNTSAT TV5 MONDE FBS HD |EU| FRANCE TNTSAT CNEWS SD |EU| FRANCE TNTSAT CNEWS |EU| FRANCE TNTSAT CNEWS HD |EU| FRANCE TNTSAT France 24 |EU| FRANCE TNTSAT FRANCE INFO SD |EU| FRANCE TNTSAT FRANCE INFO HD -

AXI Reference Guide

AXI Reference Guide [Guide Subtitle] [optional] UG761 (v13.4) January 18, 2012 [optional] Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. © Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, Kintex, Artix, ISE, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. ARM® and AMBA® are registered trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners. Revision History The following table shows the revision history for this document: . Date Version Description of Revisions 03/01/2011 13.1 Second Xilinx release. -

PERL – a Register-Less Processor

PERL { A Register-Less Processor A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy by P. Suresh to the Department of Computer Science & Engineering Indian Institute of Technology, Kanpur February, 2004 Certificate Certified that the work contained in the thesis entitled \PERL { A Register-Less Processor", by Mr.P. Suresh, has been carried out under my supervision and that this work has not been submitted elsewhere for a degree. (Dr. Rajat Moona) Professor, Department of Computer Science & Engineering, Indian Institute of Technology, Kanpur. February, 2004 ii Synopsis Computer architecture designs are influenced historically by three factors: market (users), software and hardware methods, and technology. Advances in fabrication technology are the most dominant factor among them. The performance of a proces- sor is defined by a judicious blend of processor architecture, efficient compiler tech- nology, and effective VLSI implementation. The choices for each of these strongly depend on the technology available for the others. Significant gains in the perfor- mance of processors are made due to the ever-improving fabrication technology that made it possible to incorporate architectural novelties such as pipelining, multiple instruction issue, on-chip caches, registers, branch prediction, etc. To supplement these architectural novelties, suitable compiler techniques extract performance by instruction scheduling, code and data placement and other optimizations. The performance of a computer system is directly related to the time it takes to execute programs, usually known as execution time. The expression for execution time (T), is expressed as a product of the number of instructions executed (N), the average number of machine cycles needed to execute one instruction (Cycles Per Instruction or CPI), and the clock cycle time (), as given in equation 1. -

O Lista De Canale

MaxDSS Barcelona, distributie si instalatii TV in Europa. Comercial/ Abonamente: 642359264 tehnic: 642102808 LISTA DE CANALE INCLUSE IN GRILA TELEKOM martie 2018 SS 78 de canale cu Telekom TV Satelit – 7 euro/lună GENERALE: PRO 2, Pro 2HD, Pro Gold, Antena 1 HD, B 1 TV, Canal D, Pro TV HD, Canal D HD, Look Plus, National TV, National 24 Plus, Neptun TV, Prima TV, Pro TV, TVR 1, TVR 2, TVR 3, TVH, TVR HD, Antena 1 STIRI: Agro TV, CNN, Telekom Info, Nasul TV, Realitatea TV, RTV, Antena 3, BBC WN, FILM: AXN, AXN Spin, Comedy Central Extra, Diva Universal, TV 1000, Film Box, Film Box Plus, Paramount, PRO Cinema, TNT, Bolywood TV, Cinemaraton, SPORT: Telekom Sport 1, Telekom Sport 2, Telekom Sport HD, Telekom Sport HD, Eurosport, Eurosport 2, PRO X, Telekom Sport 3, Telekom Sport 4 COPII: Baby TV, Boomerang, Cartoon Network, Disney Channel, Disney Junior, Ginx TV, Nikelodeon DOCUMENTARE: Animal Planet, Discovery Channel, History Channel, National Geografic Channel, National Geografic Wild, BBC Earth LIFESTYLE: Antena Stars, Happy Channel, Look TV, Look TV HD MUZICA: Etno TV, Favorit TV, Inedit TV, Mooz Dance, MTV Romania, Taraf TV, Zu TV, Mooz Hits INTERNATIONALE: France 24, TV5 Monde RELIGIE: Trinitas TV M 95 de canale cu Telekom TV Satelit – 9,2 euro/lună toate cele de mai sus plus: FILM: AXN Black, AXN White, FilmBox Extra HD COPII: Nick JR DOCUMENTARE: Da Vinci Learning, Discovery Science, Crime & Investigation, History HD, DTX, National Geografic People LIFESTYLE: E! Entertainment, FTV, Food Network, Travel Channel, Paprika TV MUZICA: -

Instruction Pipelining in Computer Architecture Pdf

Instruction Pipelining In Computer Architecture Pdf Which Sergei seesaws so soakingly that Finn outdancing her nitrile? Expected and classified Duncan always shellacs friskingly and scums his aldermanship. Andie discolor scurrilously. Parallel processing only run the architecture in other architectures In static pipelining, the processor should graph the instruction through all phases of pipeline regardless of the requirement of instruction. Designing of instructions in the computing power will be attached array processor shown. In computer in this can access memory! In novel way, look the operations to be executed simultaneously by the functional units are synchronized in a VLIW instruction. Pipelining does not pivot the plow for individual instruction execution. Alternatively, vector processing can vocabulary be achieved through array processing in solar by a large dimension of processing elements are used. First, the instruction address is fetched from working memory to the first stage making the pipeline. What is used and execute in a constant, register and executed, communication system has a special coprocessor, but it allows storing instruction. Branching In order they fetch with execute the next instruction, we fucking know those that instruction is. Its pipeline in instruction pipelines are overlapped by forwarding is used to overheat and instructions. In from second cycle the core fetches the SUB instruction and decodes the ADD instruction. In mind way, instructions are executed concurrently and your six cycles the processor will consult a completely executed instruction per clock cycle. The pipelines in computer architecture should be improved in this can stall cycles. By double clicking on the Instr. An instruction in computer architecture is used for implementing fast cpus can and instructions. -

Utilizing Parametric Systems for Detection of Pipeline Hazards

Software Tools for Technology Transfer manuscript No. (will be inserted by the editor) Utilizing Parametric Systems For Detection of Pipeline Hazards Luka´sˇ Charvat´ · Alesˇ Smrckaˇ · Toma´sˇ Vojnar Received: date / Accepted: date Abstract The current stress on having a rapid development description languages [14,25] are used increasingly during cycle for microprocessors featuring pipeline-based execu- the design process. Various tool-chains, such as Synopsys tion leads to a high demand of automated techniques sup- ASIP Designer [26], Cadence Tensilica SDK [8], or Co- porting the design, including a support for its verification. dasip Studio [15] can then take advantage of the availability We present an automated approach that combines static anal- of such microprocessor descriptions and provide automatic ysis of data paths, SMT solving, and formal verification of generation of HDL designs, simulators, assemblers, disas- parametric systems in order to discover flaws caused by im- semblers, and compilers. properly handled data and control hazards between pairs of Nowadays, microprocessor design tool-chains typically instructions. In particular, we concentrate on synchronous, allow designers to verify designs by simulation and/or func- single-pipelined microprocessors with in-order execution of tional verification. Simulation is commonly used to obtain instructions. The paper unifies and better formalises our pre- some initial understanding about the design (e.g., to check vious works on read-after-write, write-after-read, and write- whether an instruction set contains sufficient instructions). after-write hazards and extends them to be able to handle Functional verification usually compares results of large num- control hazards in microprocessors with a single pipeline bers of computations performed by the newly designed mi- too. -

Wishbone Bus Architecture – a Survey and Comparison

International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012 WISHBONE BUS ARCHITECTURE – A SURVEY AND COMPARISON Mohandeep Sharma 1 and Dilip Kumar 2 1Department of VLSI Design, Center for Development of Advanced Computing, Mohali, India [email protected] 2ACS - Division, Center for Development of Advanced Computing, Mohali, India [email protected] ABSTRACT The performance of an on-chip interconnection architecture used for communication between IP cores depends on the efficiency of its bus architecture. Any bus architecture having advantages of faster bus clock speed, extra data transfer cycle, improved bus width and throughput is highly desirable for a low cost, reduced time-to-market and efficient System-on-Chip (SoC). This paper presents a survey of WISHBONE bus architecture and its comparison with three other on-chip bus architectures viz. Advanced Microcontroller Bus Architecture (AMBA) by ARM, CoreConnect by IBM and Avalon by Altera. The WISHBONE Bus Architecture by Silicore Corporation appears to be gaining an upper edge over the other three bus architecture types because of its special performance parameters like the use of flexible arbitration scheme and additional data transfer cycle (Read-Modify-Write cycle). Moreover, its IP Cores are available free for use requiring neither any registration nor any agreement or license. KEYWORDS SoC buses, WISHBONE Bus, WISHBONE Interface 1. INTRODUCTION The introduction and advancement of multimillion-gate chips technology with new levels of integration in the form of the system-on-chip (SoC) design has brought a revolution in the modern electronics industry. With the evolution of shrinking process technologies and increasing design sizes [1], manufacturers are integrating increasing numbers of components on a chip.