Open PDF in New Window

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

Memristive Devices for Computing J

REVIEW ARTICLE PUBLISHED ONLINE: 27 DECEMBER 2012 | DOI: 10.1038/NNANO.2012.240 Memristive devices for computing J. Joshua Yang1, Dmitri B. Strukov2 and Duncan R. Stewart3 Memristive devices are electrical resistance switches that can retain a state of internal resistance based on the history of applied voltage and current. These devices can store and process information, and offer several key performance characteristics that exceed conventional integrated circuit technology. An important class of memristive devices are two-terminal resistance switches based on ionic motion, which are built from a simple conductor/insulator/conductor thin-film stack. These devices were originally conceived in the late 1960s and recent progress has led to fast, low-energy, high-endurance devices that can be scaled down to less than 10 nm and stacked in three dimensions. However, the underlying device mechanisms remain unclear, which is a significant barrier to their widespread application. Here, we review recent progress in the development and understanding of memristive devices. We also examine the performance requirements for computing with memristive devices and detail how the outstanding challenges could be met. he search for new computing technologies is driven by the con- excellent review articles8–19. Here, we focus on the chemical and phys- tinuing demand for improved computing performance, but ical mechanisms of memristive devices, and try to identify the key Tto be of use a new technology must be scalable and capable. issues that impede the commercialization of memristors as computer Memristor or memristive nanodevices seem to fulfil these require- memory and logic. ments — they can be scaled down to less than 10 nm and offer fast, non-volatile, low-energy electrical switching. -

Navaraj, William Ringal Taube (2019) Inorganic Micro/Nanostructures- Based High-Performance Flexible Electronics for Electronic Skin Application

Navaraj, William Ringal Taube (2019) Inorganic micro/nanostructures- based high-performance flexible electronics for electronic skin application. PhD thesis. https://theses.gla.ac.uk/40973/ This work is made available under the Creative Commons Attribution- NonCommercial 4.0 License: https://creativecommons.org/licenses/by- nc/4.0/ Enlighten: Theses https://theses.gla.ac.uk/ [email protected] Inorganic Micro/Nanostructures-based High-performance Flexible Electronics for Electronic Skin Application William Ringal Taube Navaraj A Thesis submitted to School of Engineering University of Glasgow in fulfilment of the requirements for the degree of Doctor of Philosophy January 2019 Supervisors: Prof. Ravinder Dahiya Prof. Duncan Gregory Abstract Electronics in the future will be printed on diverse substrates, benefiting several emerging applications such as electronic skin (e-skin) for robotics/prosthetics, flexible displays, flexible/conformable biosensors, large area electronics, and implantable devices. For such applications, electronics based on inorganic micro/nanostructures (IMNSs) from high mobility materials such as single crystal silicon and compound semiconductors in the form of ultrathin chips, membranes, nanoribbons (NRs), nanowires (NWs) etc., offer promising high-performance solutions compared to conventional organic materials. This thesis presents an investigation of the various forms of IMNSs for high-performance electronics. Active components (from Silicon) and sensor components (from indium tin oxide (ITO), vanadium pentaoxide (V2O5), and zinc oxide (ZnO)) were realised based on the IMNS for application in artificial tactile skin for prosthetics/robotics. Inspired by human tactile sensing, a capacitive-piezoelectric tandem architecture was realised with indium tin oxide (ITO) on a flexible polymer sheet for achieving static (upto 0.25 kPa-1 sensitivity) and dynamic (2.28 kPa-1 sensitivity) tactile sensing. -

Ultra Low Power Robust 12T Sram Architecture Based on Parallel Cross- Coupling Feedback

OF JOURNAL CRITICAL REVIEWS ISSN- 2394-5125 VOL 7, ISSUE 19, 2020 ULTRA LOW POWER ROBUST 12T SRAM ARCHITECTURE BASED ON PARALLEL CROSS- COUPLING FEEDBACK Dr.H.Kareemullah2, Mr.C.Venkatnarayanan2 1Assistant Professor, Department of Electronics & Instrumentation Engineering, B.S.A.Crescent Institute of Science & Technology, Chennai, email: [email protected] 2Teaching Fellow, Department of ECE,University College of Engineering Arni, Thatchur, Arni – 632 326. email: [email protected] ABSTRACT: Ultra-low power, low on-chip processing circuits are highly desirable for lightweight and wearable applications. Memory is an integral part of most of these systems and is also diminished as the scale of the system reduces. Low power and processing architecture at high speed is therefore a major concern. The durability of random static access memory cells (SRAM) is another critical factor. This paper provides a new standard memory cell based (SCM) twelve-transistor (12 T) circuit. In order to achieve high region performance and low energy usage, three gating transistors for each column of SRAM cells have been used. The three-stage read-out system eliminates reading delays as well as energy consumption. As compared to the previously published SCM circuit in a 65-nm CMOS technology, the read and write energy consumption per operation is reduced. In comparison to the previously published SCM circuit, read time and cell lay-out are also reduced . In comparison, the traditional T-architecture guarantees high data consistency and writes functionality with the proposed 12 T SRAM module. KEYWORDS: SCM, twelve-transistor and SRAM cells I. INTRODUCTION: The need for low power / energy consumption of the integrated ICs, is increasingly rigid with the prosperity of portable and wearable electronic devices and the ubiquitous implementation of wireless sensor networks. -

Computer Development at the National Bureau of Standards

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

Modeling of Memristive Systems and Its Applications

Modeling of memristive systems and its applications By Jose´ Balaam Alarcon´ Angulo Thesis submitted as a partial requirement for the degree of Master in Science with specialty in Electronics at the Instituto Nacional de Astrof´ısica, Optica´ y Electronica´ San Andres´ Cholula, Puebla Adviser: Dr. Librado Arturo Sarmiento Reyes, INAOE c INAOE 2017 The author hereby grants to INAOE permission to reproduce and to distribute copies of this thesis document in whole or in part Modeling of memristive systems and its applications Master's Thesis By: Jos´eBalaam Alarc´onAngulo Adviser: Dr. Librado Arturo Sarmiento Reyes Instituto Nacional de Astrof´ısica Optica´ y Electr´onica Electronics Department San Andres´ Cholula, Puebla. January 16, 2018 i Agradezco a mis padres Guadalupe Alarc´ony Ma. Teresa y a mi hermana Dayanira Alarc´onpor su incondicional apoyo a lo largo de toda mi vida. Al doctor Arturo Sarmiento por su orientaci´ondurante el desarrollo de esta tesis.Y a todos mis amigos que siempre est´anah´ıe hicieron invaluables aportes para el desarrollo de este trabajo. Modeling of memristive systems and its applications iii To my future readers. I hope you will enjoy reading this work as much as I did when writing it and that it will serves as a guide for future work. Modeling of memristive systems and its applications Resumen Desde el advenimiento del memristor como elemento b´asicode circuito real, ha habido un significativo impulso en la investigaci´onorientada al desarrollo de aplicaciones del memristor en dise~node circuitos y procesamiento de se~nales.Amplificadores con retroalimentac´onnegativa basados en nullores se encuentran entre las aplicaciones m´as factibles debido a que la propiedad de memoria del memristor puede ser incorporada a la transferencia de amplificaci´onal colocar el memristor directamente en el lazo de retroalimentaci´on. -

Simon E. Gluck Collection of Photographs of EDVAC and MSAC Computers 1990.232

Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 This finding aid was produced using ArchivesSpace on September 19, 2021. Description is written in: English. Describing Archives: A Content Standard Audiovisual Collections PO Box 3630 Wilmington, Delaware 19807 [email protected] URL: http://www.hagley.org/library Simon E. Gluck collection of photographs of EDVAC and MSAC computers 1990.232 Table of Contents Summary Information .................................................................................................................................... 3 Biographical Note .......................................................................................................................................... 3 Scope and Content ......................................................................................................................................... 4 Administrative Information ............................................................................................................................ 4 Related Materials ........................................................................................................................................... 5 Controlled Access Headings .......................................................................................................................... 5 Additonal Extent Statement ........................................................................................................................... 5 - Page 2 - Simon E. Gluck collection -

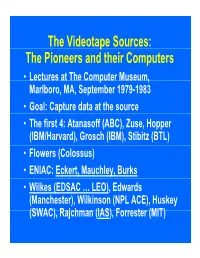

P the Pioneers and Their Computers

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA.. -

A Survey of Memristive Threshold Logic Circuits Akshay Kumar Maan, Deepthi Anirudhan Jayadevi, and Alex Pappachen James, Senior Member, IEEE

IEEE TRANSACTIONS ON NEURAL NETWORKS AND LEARNING SYSTEMS 1 A Survey of Memristive Threshold Logic Circuits Akshay Kumar Maan, Deepthi Anirudhan Jayadevi, and Alex Pappachen James, Senior Member, IEEE Abstract—In this paper, we review the different memristive Threshold logic (TL) itself was first introduced by Warren threshold logic (MTL) circuits that are inspired from the synaptic McCulloch and Walter Pitts in 1943 [17] in the early model action of flow of neurotransmitters in the biological brain. of an artificial neuron based on the basic property of firing Brain-like generalisation ability and area minimisation of these threshold logic circuits aim towards crossing the Moore’s law of the biological neuron. The logic computed the sign of the boundaries at device, circuits and systems levels. Fast switch- weighted sum of its inputs. Modelling a neuron as a threshold ing memory, signal processing, control systems, programmable logic gate (TLG) that fires when input reaches a threshold has logic, image processing, reconfigurable computing, and pattern been the basis of the research on neural networks (NNs) and recognition are identified as some of the potential applications of their hardware implementation in standard CMOS logic [18]. MTL systems. The physical realization of nanoscale devices with However, to continue geometrical scaling of semiconductor memristive behaviour from materials like TiO2, ferroelectrics, silicon, and polymers has accelerated research effort in these components as per Moore’s Law (and beyond), semiconductor application areas inspiring the scientific community to pursue industry needs to investigate a future beyond CMOS, and design of high speed, low cost, low power and high density designs beyond the fetch-decode-execute paradigm of von neuromorphic architectures. -

Feedback Systems with Memristors

Feedback Systems with Memristors Milan Stork1, Josef Hrusak2, Daniel Mayer3 1,2Department of Applied Electronics and Telecommunications, 3Department of Theory of Electrical Engineering University of West Bohemia, 30614 Plzen, Czech Republic [email protected], [email protected], [email protected] Abstract In 1971 the electrical engineer Leon Chua pointed out [1], that, a fourth passive element should in fact be added to the list The contribution is concerned on the properties of the new of basic circuits elements. He named this hypothetical element, ideal circuit element, a memristor. By definition, a linking flux and charge, the memristor. It is just the inability to memristor relates the charge q and the magnetic flux in a duplicate the properties of the memistor with a combination of circuit, and complements a resistor R, a capacitor C, and an the other three passive circuits elements, what makes the inductor L as an ingredient of ideal electrical circuits. The existence question of the memristor fundamental. properties of these three elements and their circuits are a The point is that a static nonlinearity interpreted as a part of the standard curricula. The existence of the memristor always appears instantaneously as a nonlinear memristor as the fourth ideal circuit element was predicted resistor. However, in fact it represents a new passive element, in 1971 based on symmetry arguments, but was clearly which may relate some state variable to flux without storing a experimentally demonstrated in 2008. The definition of the magnetic field. memristor is based solely on fundamental circuit variables, The HP memristor is a passive two-terminal electronic device similar to the resistor, capacitor, and inductor. -

John William Mauchly

John William Mauchly Born August 30, 1907, Cincinnati, Ohio; died January 8, 1980, Abington, Pa.; the New York Times obituary (Smolowe 1980) described Mauchly as a “co-inventor of the first electronic computer” but his accomplishments went far beyond that simple description. Education: physics, Johns Hopkins University, 1929; PhD, physics, Johns Hopkins University, 1932. Professional Experience: research assistant, Johns Hopkins University, 1932-1933; professor of physics, Ursinus College, 1933-1941; Moore School of Electrical Engineering, 1941-1946; member, Electronic Control Company, 1946-1948; president, Eckert-Mauchly Computer Company, 1948-1950; Remington-Rand, 1950-1955; director, Univac Applications Research, Sperry-Rand 1955-1959; Mauchly Associates, 1959-1980; Dynatrend Consulting Company, 1967-1980. Honors and Awards: president, ACM, 1948-1949; Howard N. Potts Medal, Franklin Institute, 1949; John Scott Award, 1961; Modern Pioneer Award, NAM, 1965; AMPS Harry Goode Memorial Award for Excellence, 1968; IEEE Emanual R. Piore Award, 1978; IEEE Computer Society Pioneer Award, 1980; member, Information Processing Hall of Fame, Infornart, Dallas, Texas, 1985. Mauchly was born in Cincinnati, Ohio, on August 30, 1907. He attended Johns Hopkins University initially as an engineering student but later transferred into physics. He received his PhD degree in physics in 1932 and the following year became a professor of physics at Ursinus College in Collegeville, Pennsylvania. At Ursinus he was well known for his excellent and dynamic teaching, and for his research in meteorology. Because his meteorological work required extensive calculations, he began to experiment with alternatives to mechanical tabulating equipment in an effort to reduce the time required to solve meteorological equations. -

The Manchester University "Baby" Computer and Its Derivatives, 1948 – 1951”

Expert Report on Proposed Milestone “The Manchester University "Baby" Computer and its Derivatives, 1948 – 1951” Thomas Haigh. University of Wisconsin—Milwaukee & Siegen University March 10, 2021 Version of citation being responded to: The Manchester University "Baby" Computer and its Derivatives, 1948 - 1951 At this site on 21 June 1948 the “Baby” became the first computer to execute a program stored in addressable read-write electronic memory. “Baby” validated the widely used Williams- Kilburn Tube random-access memories and led to the 1949 Manchester Mark I which pioneered index registers. In February 1951, Ferranti Ltd's commercial Mark I became the first electronic computer marketed as a standard product ever delivered to a customer. 1: Evaluation of Citation The final wording is the result of several rounds of back and forth exchange of proposed drafts with the proposers, mediated by Brian Berg. During this process the citation text became, from my viewpoint at least, far more precise and historically reliable. The current version identifies several distinct contributions made by three related machines: the 1948 “Baby” (known officially as the Small Scale Experimental Machine or SSEM), a minimal prototype computer which ran test programs to prove the viability of the Manchester Mark 1, a full‐scale computer completed in 1949 that was fully designed and approved only after the success of the “Baby” and in turn served as a prototype of the Ferranti Mark 1, a commercial refinement of the Manchester Mark 1 of which I believe 9 copies were sold. The 1951 date refers to the delivery of the first of these, to Manchester University as a replacement for its home‐built Mark 1.